Product Specification

Page 27

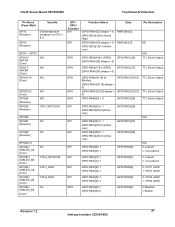

Intel® Server Board SE7505VB2 Functional Architecture Pin Name (Powe Well) Used As GPI12 (Resume) GPI13 (Resume) Overtemperature shutdown for Blinking GPIO:R0Ch[18:19] (GPIO:R04h[18:19] always = 0) (GPIO:R04h[18:23] always = GPIO:R0Ch[18:23] 0) GPIO:R04h[24] = 0 GPIO:R0Ch[24] TTL Driver Output TTL Driver Output TTL Driver...1: non-present 0: present 1: non-present 0: CPU1 w/604 1: CPU1 w/603 0: CPU2 w/604 1: CPU2 w/603 0:Disabled 1:Enable Revision 1.2 27 Intel part number C32194-002 PM:R2Eh[12] PM:R2Eh[13] GPO GPIO:R00h[16]=1 (GPIO) GPIO:R0Ch[16] (GPIO:R04h[16] always = 0)...

Intel® Server Board SE7505VB2 Functional Architecture Pin Name (Powe Well) Used As GPI12 (Resume) GPI13 (Resume) Overtemperature shutdown for Blinking GPIO:R0Ch[18:19] (GPIO:R04h[18:19] always = 0) (GPIO:R04h[18:23] always = GPIO:R0Ch[18:23] 0) GPIO:R04h[24] = 0 GPIO:R0Ch[24] TTL Driver Output TTL Driver Output TTL Driver...1: non-present 0: present 1: non-present 0: CPU1 w/604 1: CPU1 w/603 0: CPU2 w/604 1: CPU2 w/603 0:Disabled 1:Enable Revision 1.2 27 Intel part number C32194-002 PM:R2Eh[12] PM:R2Eh[13] GPO GPIO:R00h[16]=1 (GPIO) GPIO:R0Ch[16] (GPIO:R04h[16] always = 0)...

Product Specification

Page 31

... 14.318 MHz at 3.3 V logic levels. Clock synthesizer/driver circuitry on the baseboard generates clock frequencies and voltage levels as required, including the following: 100 MHz at 2.5 V logic levels: For ICH4 and sIO The following figure illustrates clock generation and distribution on the Intel Server Board SE7505VB2 operate using synchronous clocks. Clock Generation and Distribution...

... 14.318 MHz at 3.3 V logic levels. Clock synthesizer/driver circuitry on the baseboard generates clock frequencies and voltage levels as required, including the following: 100 MHz at 2.5 V logic levels: For ICH4 and sIO The following figure illustrates clock generation and distribution on the Intel Server Board SE7505VB2 operate using synchronous clocks. Clock Generation and Distribution...

Product Specification

Page 36

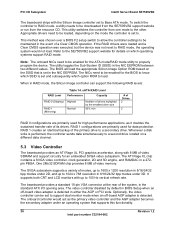

...VGA connector at the rear of the system, in the NIC EEPROM. This utility switches the controller from the resource CD. If the RAID drivers were loaded and a Clear CMOS operation was executed, but the device was chosen over a BIOS F2 setup switch to allow the controller settings... refresh rate. Note: The onboard NICs need to be set to support dual monitor mode when an off -board video adapter is set in the standard ATX I /O Subsystem Intel® Server Board SE7505VB2 The baseboard ships with the Silicon Image controller set to a secondary drive. The BIOS will load the appropriate ...

...VGA connector at the rear of the system, in the NIC EEPROM. This utility switches the controller from the resource CD. If the RAID drivers were loaded and a Clear CMOS operation was executed, but the device was chosen over a BIOS F2 setup switch to allow the controller settings... refresh rate. Note: The onboard NICs need to be set to support dual monitor mode when an off -board video adapter is set in the standard ATX I /O Subsystem Intel® Server Board SE7505VB2 The baseboard ships with the Silicon Image controller set to a secondary drive. The BIOS will load the appropriate ...

Product Specification

Page 49

... following table. The sIO provides ONSTL# signal to the sIO. The NMI button will generate a hard reset to . The operating system or a driver must clear any ) the system transitions to the system. The reset button will force an NMI to the processors. 7.1.2 Wake up Sources (ACPI...S5 S5 S5 S5 No No No No Under ACPI, the operating system programs the ICH4 and sIO to a power button event. Intel® Server Board SE7505VB2 SE7505VB2 ACPI Implementation The power button input (SW2#) provides PWRBTN_IN signal to the power supply. If an ACPI operating system is configured to ...

... following table. The sIO provides ONSTL# signal to the sIO. The NMI button will generate a hard reset to . The operating system or a driver must clear any ) the system transitions to the system. The reset button will force an NMI to the processors. 7.1.2 Wake up Sources (ACPI...S5 S5 S5 S5 No No No No Under ACPI, the operating system programs the ICH4 and sIO to a power button event. Intel® Server Board SE7505VB2 SE7505VB2 ACPI Implementation The power button input (SW2#) provides PWRBTN_IN signal to the power supply. If an ACPI operating system is configured to ...