Specification Update

Page 1

... Specification Update. Document Number: 313279-027 Intel® Core™2 Extreme Processor X6800Δ and Intel® Core™2 Duo Desktop Processor E6000Δ and E4000Δ Sequence Specification Update - Current characterized errata are documented in the 775-land LGA Package supporting Intel® 64Φ Architecture, Intel® Virtualization Technology± and Intel® Trusted Execution Technologyŧ December...

... Specification Update. Document Number: 313279-027 Intel® Core™2 Extreme Processor X6800Δ and Intel® Core™2 Duo Desktop Processor E6000Δ and E4000Δ Sequence Specification Update - Current characterized errata are documented in the 775-land LGA Package supporting Intel® 64Φ Architecture, Intel® Virtualization Technology± and Intel® Trusted Execution Technologyŧ December...

Specification Update

Page 2

... of any time, without an Intel 64-enabled BIOS. The Intel® Core™2 Duo and Intel® Core™2 Extreme Processors may make changes to them. Enabling Execute Disable Bit functionality requires a PC with a processor with your PC manufacturer on your system vendor for Intel 64. Intel, the Intel logo, Celeron, Pentium, Xeon, Intel SpeedStep, Intel Core, and Core Inside are not intended for...

... of any time, without an Intel 64-enabled BIOS. The Intel® Core™2 Duo and Intel® Core™2 Extreme Processors may make changes to them. Enabling Execute Disable Bit functionality requires a PC with a processor with your PC manufacturer on your system vendor for Intel 64. Intel, the Intel logo, Celeron, Pentium, Xeon, Intel SpeedStep, Intel Core, and Core Inside are not intended for...

Specification Update

Page 4

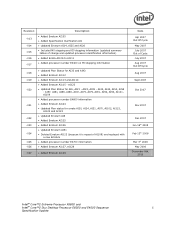

...003 -004 -005 -006 -007 -008 -009 -010 -011 -012 Description • Initial release of the Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 Sequence Specification Update • Updated Erratum AI19, AI29 and AI40 • Added Erratum AI58-AI67 • ... 2007 Out Of Cycle Feb 2007 Mar 2007 Apr 2007 Apr 2007 Out Of Cycle 4 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update AI85 • Corrected Plan information in Summary table of ...

...003 -004 -005 -006 -007 -008 -009 -010 -011 -012 Description • Initial release of the Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 Sequence Specification Update • Updated Erratum AI19, AI29 and AI40 • Added Erratum AI58-AI67 • ... 2007 Out Of Cycle Feb 2007 Mar 2007 Apr 2007 Apr 2007 Out Of Cycle 4 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update AI85 • Corrected Plan information in Summary table of ...

Specification Update

Page 5

...Nov 2007 Dec 2007 Jan 16th 2008 Feb 13th 2008 Mar 3rd 2008 May 2008 December 8th, 2010 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 5 Specification Update AI23, AI38 - AI57, AI61, AI66, AI69, AI72,... AI75, AI79, AI91, AI92, AI94, AI101, AI109 • Added processor number E4600 information • Added Erratum AI124 • ...

...Nov 2007 Dec 2007 Jan 16th 2008 Feb 13th 2008 Mar 3rd 2008 May 2008 December 8th, 2010 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 5 Specification Update AI23, AI38 - AI57, AI61, AI66, AI69, AI72,... AI75, AI79, AI91, AI92, AI94, AI101, AI109 • Added processor number E4600 information • Added Erratum AI124 • ...

Specification Update

Page 6

...; 64 and IA-32 Architectures Software Developer's Manual Volume 3B: System Programming Guide Document Location http://www.intel.com/product s/processor/manuals/index.h tm 6 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update This document may also contain information that has not been previously published. Preface Preface...

...; 64 and IA-32 Architectures Software Developer's Manual Volume 3B: System Programming Guide Document Location http://www.intel.com/product s/processor/manuals/index.h tm 6 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update This document may also contain information that has not been previously published. Preface Preface...

Specification Update

Page 7

... throughout the product's lifecycle, or until a particular stepping is no longer commercially available. These processors are made to the appropriate product specification or user documentation (datasheets, manuals, etc.). § Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 7 Specification Update Note: Errata remain in greater detail or further...

... throughout the product's lifecycle, or until a particular stepping is no longer commercially available. These processors are made to the appropriate product specification or user documentation (datasheets, manuals, etc.). § Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 7 Specification Update Note: Errata remain in greater detail or further...

Specification Update

Page 8

...Changes Summary Tables of the component, and to account for the other outstanding issues through documentation or Specification Changes as noted. Intel intends to fix some of the errata in a future stepping of Changes The following notations: Codes Used in Summary Table ... to listed stepping. Row Shaded: This item is fixed in a future stepping of the document. 8 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update There are no plans to the listed MCH steppings. This table uses...

...Changes Summary Tables of the component, and to account for the other outstanding issues through documentation or Specification Changes as noted. Intel intends to fix some of the errata in a future stepping of Changes The following notations: Codes Used in Summary Table ... to listed stepping. Row Shaded: This item is fixed in a future stepping of the document. 8 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update There are no plans to the listed MCH steppings. This table uses...

Specification Update

Page 9

...; M processor Intel® Pentium® M processor on 65nm process Dual-Core Intel® Xeon® processor LV Dual-Core Intel® Xeon® processor 5100 series Intel® Core™2 Duo/Solo processor for Intel® Centrino® Duo processor technology Intel® Core™2 Extreme processor X6800 and Intel® Core™2 Duo desktop processor E6000 and E4000 sequence Quad-Core Intel® Xeon® processor 5300 series Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000...

...; M processor Intel® Pentium® M processor on 65nm process Dual-Core Intel® Xeon® processor LV Dual-Core Intel® Xeon® processor 5100 series Intel® Core™2 Duo/Solo processor for Intel® Centrino® Duo processor technology Intel® Core™2 Extreme processor X6800 and Intel® Core™2 Duo desktop processor E6000 and E4000 sequence Quad-Core Intel® Xeon® processor 5300 series Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000...

Specification Update

Page 10

...® dual-core processor Quad-Core Intel® Xeon® processor 3200 series Dual-Core Intel® Xeon® processor 3000 series Intel® Pentium® dual-core desktop processor E2000 sequence Intel® Celeron® processor 500 series Intel® Xeon® processor 7200, 7300 series Intel® Core™2 Extreme processor QX9650 and Intel® Core™2 Quad processor Q9000 series Intel® Core™ 2 Duo processor E8000 series Quad-Core Intel® Xeon® processor 5400 series Dual-Core Intel®...

...® dual-core processor Quad-Core Intel® Xeon® processor 3200 series Dual-Core Intel® Xeon® processor 3000 series Intel® Pentium® dual-core desktop processor E2000 sequence Intel® Celeron® processor 500 series Intel® Xeon® processor 7200, 7300 series Intel® Core™2 Extreme processor QX9650 and Intel® Core™2 Quad processor Q9000 series Intel® Core™ 2 Duo processor E8000 series Quad-Core Intel® Xeon® processor 5400 series Dual-Core Intel®...

Specification Update

Page 11

...State from SMRAM AI22 X X X X Fixed Sequential Code Fetch to Non-canonical Address May have Non-deterministic Results AI23 X X X X Fixed VMCALL to Activate Dual-monitor Treatment of SMIs and SMM Ignores Reserved Bit settings in VM-exit Control Field AI24 X X X X X No Fix The PECI Controller Resets to the ... X X Fixed (E)CX May Get Incorrectly Updated When Performing Fast String REP MOVS or Fast String REP STOS With Large Data Structures Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 11 Specification Update

...State from SMRAM AI22 X X X X Fixed Sequential Code Fetch to Non-canonical Address May have Non-deterministic Results AI23 X X X X Fixed VMCALL to Activate Dual-monitor Treatment of SMIs and SMM Ignores Reserved Bit settings in VM-exit Control Field AI24 X X X X X No Fix The PECI Controller Resets to the ... X X Fixed (E)CX May Get Incorrectly Updated When Performing Fast String REP MOVS or Fast String REP STOS With Large Data Structures Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 11 Specification Update

Specification Update

Page 12

Summary Tables of Changes NO B1 B2 L2 M0 G0 Plan ERRATA AI31 X X X X Fixed Performance Monitoring Events for Retired Loads (CBH) and Instructions Retired (C0H) May Not Be Accurate AI32 X X X X X No Fix Upper 32 bits of 'From' Address Reported through BTMs or BTSs May be Incorrect AI33 X X X Fixed Unsynchronized Cross-Modifying Code Operations Can Cause Unexpected Instruction Execution Results MSRs Actual Frequency Clock Count (IA32_APERF) or Maximum AI34 X X X X X No Fix Frequency Clock Count (IA32_MPERF) May Contain Incorrect Data after a Machine Check Exception (MCE) AI35 X ...

Summary Tables of Changes NO B1 B2 L2 M0 G0 Plan ERRATA AI31 X X X X Fixed Performance Monitoring Events for Retired Loads (CBH) and Instructions Retired (C0H) May Not Be Accurate AI32 X X X X X No Fix Upper 32 bits of 'From' Address Reported through BTMs or BTSs May be Incorrect AI33 X X X Fixed Unsynchronized Cross-Modifying Code Operations Can Cause Unexpected Instruction Execution Results MSRs Actual Frequency Clock Count (IA32_APERF) or Maximum AI34 X X X X X No Fix Frequency Clock Count (IA32_MPERF) May Contain Incorrect Data after a Machine Check Exception (MCE) AI35 X ...

Specification Update

Page 13

... M0 G0 Plan ERRATA AI52 X X X X X No Fix Last Branch Records (LBR) Updates May be Set for Non-Single-Step #DB Exception Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 13 Specification Update Summary Tables of Read/Write (R/W) or User/Supervisor (U/S) or Present (P) Bits without TLB Shootdown...

... M0 G0 Plan ERRATA AI52 X X X X X No Fix Last Branch Records (LBR) Updates May be Set for Non-Single-Step #DB Exception Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 13 Specification Update Summary Tables of Read/Write (R/W) or User/Supervisor (U/S) or Present (P) Bits without TLB Shootdown...

Specification Update

Page 14

... Performance Monitoring Version 2 is Supported, When Only Version 1 Capabilities are Available AI87 X X X X X No Fix Unaligned Accesses to Paging Structures May Cause the Processor to Hang AI88 X X X X X No Fix Microcode Updates Performed During VMX Non-root Operation Could Result in Unexpected Behavior AI89 X X X X X No...X X X X Fixed The Stack Size May be Incorrect as a Result of VIP/VIF Check on SYSEXIT and SYSRET 14 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update

... Performance Monitoring Version 2 is Supported, When Only Version 1 Capabilities are Available AI87 X X X X X No Fix Unaligned Accesses to Paging Structures May Cause the Processor to Hang AI88 X X X X X No Fix Microcode Updates Performed During VMX Non-root Operation Could Result in Unexpected Behavior AI89 X X X X X No...X X X X Fixed The Stack Size May be Incorrect as a Result of VIP/VIF Check on SYSEXIT and SYSRET 14 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update

Specification Update

Page 15

... May Result in a Processor Hang AI115 X X X X X No Fix Instruction Fetch May Cause a Livelock During Snoops of the L1 Data Cache AI116 X X X X X No Fix Use of Memory Aliasing with Inconsistent Memory Type may Cause a System Hang or a Machine Check Exception Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence...

... May Result in a Processor Hang AI115 X X X X X No Fix Instruction Fetch May Cause a Livelock During Snoops of the L1 Data Cache AI116 X X X X X No Fix Use of Memory Aliasing with Inconsistent Memory Type may Cause a System Hang or a Machine Check Exception Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence...

Specification Update

Page 16

There are no Documentation Changes in this Specification Update revision. § 16 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update Number SPECIFICATION CLARIFICATIONS AI1 Clarification of Changes NO... Not Reflect Machine Check Error Reporting Enable Correctly AI124 X X X X X No Fix RSM Instruction Execution under Certain Conditions May Cause Processor Hang or Unexpected Instruction Execution Results AI125 X X X Fixed NMIs May Not Be Blocked by a VM-Entry Failure AI126 X X ...

There are no Documentation Changes in this Specification Update revision. § 16 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update Number SPECIFICATION CLARIFICATIONS AI1 Clarification of Changes NO... Not Reflect Machine Check Error Reporting Enable Correctly AI124 X X X X X No Fix RSM Instruction Execution under Certain Conditions May Cause Processor Hang or Unexpected Instruction Execution Results AI125 X X X Fixed NMIs May Not Be Blocked by a VM-Entry Failure AI126 X X ...

Specification Update

Page 17

Identification Information Identification Information Figure 1. Intel® Core™2 Duo Desktop Processor 2M SKU Package with 800 MHz FSB INTEL M ©'05 E4500 INTEL® CORE™2 DUO SLxxx [COO] 2.20GHZ/2M/800/06 [FPO] e4 ATPO S/N Figure 2. Intel® Core™2 Duo Desktop Processor 2M SKU Package with 1066 MHz FSB INTEL M ©'05 INTEL® CORE™2 DUO 6400 SLxxx [COO] 2.13GHZ/2M/1066/06 [FPO] e4 ATPO S/N Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 17 Specification Update

Identification Information Identification Information Figure 1. Intel® Core™2 Duo Desktop Processor 2M SKU Package with 800 MHz FSB INTEL M ©'05 E4500 INTEL® CORE™2 DUO SLxxx [COO] 2.20GHZ/2M/800/06 [FPO] e4 ATPO S/N Figure 2. Intel® Core™2 Duo Desktop Processor 2M SKU Package with 1066 MHz FSB INTEL M ©'05 INTEL® CORE™2 DUO 6400 SLxxx [COO] 2.13GHZ/2M/1066/06 [FPO] e4 ATPO S/N Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 17 Specification Update

Specification Update

Page 20

... Device ID register accessible through Table 3. Component Identification Information Component Identification Information The Intel® Core™2 Extreme processor and Intel® Core™2 Duo desktop processor can be identified by the following notes are provided in the EAX, EBX,..., and the generation field of 8W 20 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update The Model corresponds to the Intel Processor Identification and the CPUID Instruction Application Note (AP...

... Device ID register accessible through Table 3. Component Identification Information Component Identification Information The Intel® Core™2 Extreme processor and Intel® Core™2 Duo desktop processor can be identified by the following notes are provided in the EAX, EBX,..., and the generation field of 8W 20 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update The Model corresponds to the Intel Processor Identification and the CPUID Instruction Application Note (AP...

Specification Update

Page 21

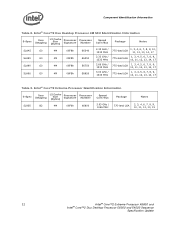

Intel® Core™2 Duo Desktop Processor 4M SKU Identification Information S-Spec Core Stepping L2 Cache Size (bytes) Processor Signature Processor Number SLA4U B2 4M 06F6h E6320 SLA4T B2 4M 06F6h E6420 SL9S8 B2 4M 06F6h E6600 SL9ZL B2 4M 06F6h E6600 SL9S7 B2 4M 06F6h E6700 SL9ZF B2 4M 06F6h E6700 Speed Core/Bus 1.86 GHz / 1066 MHz 2.13 GHz...

Intel® Core™2 Duo Desktop Processor 4M SKU Identification Information S-Spec Core Stepping L2 Cache Size (bytes) Processor Signature Processor Number SLA4U B2 4M 06F6h E6320 SLA4T B2 4M 06F6h E6420 SL9S8 B2 4M 06F6h E6600 SL9ZL B2 4M 06F6h E6600 SL9S7 B2 4M 06F6h E6700 SL9ZF B2 4M 06F6h E6700 Speed Core/Bus 1.86 GHz / 1066 MHz 2.13 GHz...

Specification Update

Page 22

... Notes 2, 3, 4, 6, 7, 8, 9, 10, 11, 12, 13, 15 22 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update Component Identification Information Table 2. Intel® Core™2 Duo Desktop Processor 4M SKU Identification Information S-Spec SLAA5 SLA9X SLA9V SLA9U Core Stepping L2 Cache Size (bytes) Processor Signature Processor Number G0 4M 06FBh E6540 G0 4M...

... Notes 2, 3, 4, 6, 7, 8, 9, 10, 11, 12, 13, 15 22 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update Component Identification Information Table 2. Intel® Core™2 Duo Desktop Processor 4M SKU Identification Information S-Spec SLAA5 SLA9X SLA9V SLA9U Core Stepping L2 Cache Size (bytes) Processor Signature Processor Number G0 4M 06FBh E6540 G0 4M...

Specification Update

Page 23

... Service Routine (ISR) set . LOCK# Asserted During a Special Cycle Shutdown Transaction May Unexpectedly De-assert Problem: During a processor shutdown transaction, when LOCK# is asserted and if a DEFER# is received during shutdown. Address Reported by Machine-Check Architecture ...in the in-service register and mask all interrupts at the same or lower priority. AI3. Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 23 Specification Update Implication: An interrupt may occur. This ISR routine ...

... Service Routine (ISR) set . LOCK# Asserted During a Special Cycle Shutdown Transaction May Unexpectedly De-assert Problem: During a processor shutdown transaction, when LOCK# is asserted and if a DEFER# is received during shutdown. Address Reported by Machine-Check Architecture ...in the in-service register and mask all interrupts at the same or lower priority. AI3. Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 23 Specification Update Implication: An interrupt may occur. This ISR routine ...