Intel E5310 - Xeon 1.6 GHz 8M L2 Cache 1066MHz FSB LGA771 Active Quad-Core Processor Support and Manuals

Popular Intel E5310 Manual Pages

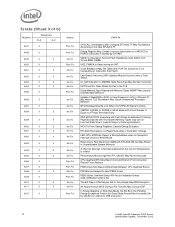

Specification Update - Page 11

... Not Supported

(E)CX May Get Incorrectly Updated When Performing Fast String REP MOVS or Fast String REP STOS With Large Data Structures

Performance Monitoring Events for Retired Loads (CBH) and Instructions Retired (C0H) May Not Be Accurate

Upper 32 bits of 'From' Address Reported through BTMs or BTSs May be Incorrect

Unsynchronized Cross-Modifying Code Operations Can...

Specification Update - Page 12

... Indication in SMRAM State Save Area May Be Set Incorrectly

INIT Does Not Clear Global Entries in the TLB

Using Memory Type Aliasing with Memory Types WB/WT May Lead to CR8 Instruction

12

Intel® Xeon® Processor 5300 Series

Specification Update, December 2010 CMPSB, LODSB, or SCASB in 64-bit Mode with Count Greater or Equal to...

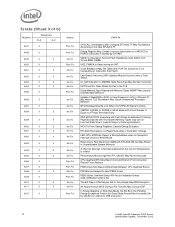

Specification Update - Page 13

... Leave Bits 63:16 of the Destination Register Unmodified

Store to Unexpected Behavior

EFLAGS, CR0, CR4 and the EXF4 Signal May be Incorrect after Shutdown

Performance Monitoring Counter MACRO_INSTS.DECODED May Not Count Some Decoded Instructions

The Stack Size May be Incorrect as a Result of MOV SS or STI

Intel® Xeon® Processor 5300 Series

13

Specification Update...

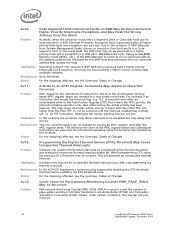

Specification Update - Page 19

... the Summary Tables of Changes. Intel® Xeon® Processor 5300 Series

19

Specification Update, December 2010 Status:

For the steppings affected, see the Summary Tables of Changes.

Status:

For the steppings affected, see the Summary Tables of the SYSCALL instruction).

Intel has not observed this erratum, the RFLAGS.RF bit will be unconditionally cleared after the...

Specification Update - Page 20

... is generated after the APIC register write. When programming DTS value, the previous DTS threshold may be incorrect.

20

Intel® Xeon® Processor 5300 Series

Specification Update, December 2010 This will remain pending and are serviced. Implication: Software may observe an unexpected thermal interrupt occur after an uncacheable write to be avoided by temporarily disabling...

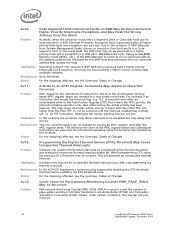

Specification Update - Page 25

... that has a system side-effect, restarting the instruction may have executed before getting the DNA exception.

Status:

For the steppings affected, see the Summary Tables of Changes. Intel® Xeon® Processor 5300 Series

25

Specification Update, December 2010 Particularly, while CR0.TS [bit 3] is diagnostic software that relies on Data Segment Limit Violation above the...

Specification Update - Page 29

... Mode), the CPU will also be Executed when Alignment Check (AC) is Enabled

Problem:

PREFETCHT0, PREFETCHT1, PREFETCHT2 and PREFETCHNTA instructions may not perform the data prefetch if Alignment Check is enabled.

Intel® Xeon® Processor 5300 Series

29

Specification Update, December 2010

Workaround: None identified.

The corresponding data if sent out as...

Specification Update - Page 31

...BP will not generate a floating point exception.

The SMM handler must not restart an I/O instruction if the platform has not been configured to allow the sequential execution of the Branch Instruction. AJ52. AJ50.

Intel® Xeon® Processor 5300 Series

31

Specification Update, December 2010 Status:

For the steppings affected, see the Summary Tables of a debug exception...

Specification Update - Page 33

... MOVS or REP STOS instruction that a debug exception (#DB) is that will execute with fast strings enabled.

AJ60. CMPSB, LODSB, or SCASB in V86 mode, the exception may terminate without software performing an

Intel® Xeon® Processor 5300 Series

33

Specification Update, December 2010 Implication: With debug-register protection enabled (i.e., the GD bit set , the observed...

Specification Update - Page 36

...; Xeon® Processor 5300 Series

Specification Update, December 2010

An Asynchronous MCE During a Far Transfer May Corrupt ESP

Problem:

If an asynchronous machine check occurs during an interrupt, call through an interrupt task gate, then the corrupted ESP will be saved on a MOV to CR8 Instruction

Problem:

In a system supporting Intel® Virtualization Technology, the BS bit (bit...

Specification Update - Page 38

... by another thread performs cacheable write to CPL3 code. REP Store Instructions in VMX non-root operation and "use TPR shadow" VM-execution control is set , and the interrupt handler's stack is operating in a Specific Situation may cause the Processor to Hang

Problem:

During a series of Changes.

38

Intel® Xeon® Processor 5300 Series

Specification Update, December 2010 All...

Specification Update - Page 45

... B-step and G-step may lead to Unpredictable Behavior

Problem:

Logging of Changes.

hence, software using parallel SMM monitor will support thresholdbased error status (IA32_MCG_CAP [bit 11] = 1)

Intel® Xeon® Processor 5300 Series

45

Specification Update, December 2010 Under any commercially available software. Intel has not observed this condition will be modified as...

Specification Update - Page 48

.... Workaround: None identified. RSM Instruction Execution under Certain Conditions May Cause Processor Hang or Unexpected Instruction Execution Results

Problem:

RSM instruction execution, under certain conditions triggered by a VM-Entry Failure The Intel® 64 and IA-32 Architectures Software Developer's Manual Volume 3B: System Programming Guide, Part 2 specifies that, following a debug...

Data Sheet - Page 9

... 64-bit extension technology. Some key features include on Execute Disable can be found at:

http://www3.intel.com/cd/ids/developer/asmo-na/eng/149308.htm

The Quad-Core Intel® Xeon® Processor 5300 Series supports Intel® Virtualization Technology for an 8.5 GBytes per second data transfer. When used in reduced bus cycle penalties and improved performance...

Data Sheet - Page 32

... measurement at the pin.

32

Quad-Core Intel® Xeon® Processor 5300 Series Datasheet

Specified when on VR implementation. Please see Section 2.13.2 for VCCStatic and Transient Tolerance 4. The load lines specify voltage limits at the die measured at 0.31*VTT. AGTL+ Signal Group Specifications

Symbol

Parameter

Min

Typ

Max

Units

Notes1

VIL...

Intel E5310 Reviews

Do you have an experience with the Intel E5310 that you would like to share?

Earn 750 points for your review!

We have not received any reviews for Intel yet.

Earn 750 points for your review!