Specification Update

Page 1

...: 313279-027 Intel® Core™2 Extreme Processor X6800Δ and Intel® Core™2 Duo Desktop Processor E6000Δ and E4000Δ Sequence Specification Update - on 65 nm Process in this Specification Update. Current characterized errata are documented in the 775-land LGA Package supporting Intel® 64Φ Architecture, Intel® Virtualization Technology± and Intel® Trusted...

...: 313279-027 Intel® Core™2 Extreme Processor X6800Δ and Intel® Core™2 Duo Desktop Processor E6000Δ and E4000Δ Sequence Specification Update - on 65 nm Process in this Specification Update. Current characterized errata are documented in the 775-land LGA Package supporting Intel® 64Φ Architecture, Intel® Virtualization Technology± and Intel® Trusted...

Specification Update

Page 2

.... Processor numbers differentiate features within each processor family, not across different processor families. Copyright © 2006 - 2010, Intel Corporation 2 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update Intel reserves... OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. The Intel® Core™2 Duo and Intel® Core™2 Extreme Processors may cause the product to specifications and product descriptions at any features or instructions ...

.... Processor numbers differentiate features within each processor family, not across different processor families. Copyright © 2006 - 2010, Intel Corporation 2 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update Intel reserves... OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. The Intel® Core™2 Duo and Intel® Core™2 Extreme Processors may cause the product to specifications and product descriptions at any features or instructions ...

Specification Update

Page 4

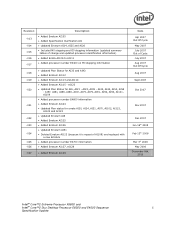

...Erratum AI61 with a new erratum • Added Erratum AI83 - AI85 • Corrected Plan information in Summary Table of the Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 Sequence Specification Update • Updated Erratum AI19, AI29 and AI40 • Added Erratum AI58-AI67 • Updated Erratum... 2006 Jan 2007 Jan 2007 Out Of Cycle Feb 2007 Mar 2007 Apr 2007 Apr 2007 Out Of Cycle 4 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update

...Erratum AI61 with a new erratum • Added Erratum AI83 - AI85 • Corrected Plan information in Summary Table of the Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 Sequence Specification Update • Updated Erratum AI19, AI29 and AI40 • Added Erratum AI58-AI67 • Updated Erratum... 2006 Jan 2007 Jan 2007 Out Of Cycle Feb 2007 Mar 2007 Apr 2007 Apr 2007 Out Of Cycle 4 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update

Specification Update

Page 5

... 2007 Oct 2007 Nov 2007 Dec 2007 Jan 16th 2008 Feb 13th 2008 Mar 3rd 2008 May 2008 December 8th, 2010 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 5 Specification Update AI123 • Updated Plan Status for AI33 and AI43 • Added Erratum AI112 • Added...

... 2007 Oct 2007 Nov 2007 Dec 2007 Jan 16th 2008 Feb 13th 2008 Mar 3rd 2008 May 2008 December 8th, 2010 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 5 Specification Update AI123 • Updated Plan Status for AI33 and AI43 • Added Erratum AI112 • Added...

Specification Update

Page 6

...; 64 and IA-32 Architectures Software Developer's Manual Volume 3B: System Programming Guide Document Location http://www.intel.com/product s/processor/manuals/index.h tm 6 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update Preface Preface This document is intended for hardware system manufacturers and for software developers...

...; 64 and IA-32 Architectures Software Developer's Manual Volume 3B: System Programming Guide Document Location http://www.intel.com/product s/processor/manuals/index.h tm 6 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update Preface Preface This document is intended for hardware system manufacturers and for software developers...

Specification Update

Page 7

... that is no longer commercially available. Products are modifications to the appropriate product specification or user documentation (datasheets, manuals, etc.). § Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 7 Specification Update Hardware and software designed to fully functional. Under these circumstances, errata removed from published specifications...

... that is no longer commercially available. Products are modifications to the appropriate product specification or user documentation (datasheets, manuals, etc.). § Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 7 Specification Update Hardware and software designed to fully functional. Under these circumstances, errata removed from published specifications...

Specification Update

Page 8

Intel intends to fix some of the errata in a future stepping of the product. This table uses the following notations: Codes Used in Summary Table Stepping X: ... in a future stepping of the component, and to the listed MCH steppings. Summary Tables of Changes Summary Tables of the document. 8 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update There are no plans to fix this stepping. (No mark) or (Blank Box): This erratum...

Intel intends to fix some of the errata in a future stepping of the product. This table uses the following notations: Codes Used in Summary Table Stepping X: ... in a future stepping of the component, and to the listed MCH steppings. Summary Tables of Changes Summary Tables of the document. 8 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update There are no plans to fix this stepping. (No mark) or (Blank Box): This erratum...

Specification Update

Page 9

...; Pentium® 4 processor on 65nm process Dual-Core Intel® Xeon® processor LV Dual-Core Intel® Xeon® processor 5100 series Intel® Core™2 Duo/Solo processor for Intel® Centrino® Duo processor technology Intel® Core™2 Extreme processor X6800 and Intel® Core™2 Duo desktop processor E6000 and E4000 sequence Quad-Core Intel® Xeon® processor 5300 series Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and...

...; Pentium® 4 processor on 65nm process Dual-Core Intel® Xeon® processor LV Dual-Core Intel® Xeon® processor 5100 series Intel® Core™2 Duo/Solo processor for Intel® Centrino® Duo processor technology Intel® Core™2 Extreme processor X6800 and Intel® Core™2 Duo desktop processor E6000 and E4000 sequence Quad-Core Intel® Xeon® processor 5300 series Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and...

Specification Update

Page 10

... processor QX9650 and Intel® Core™2 Quad processor Q9000 series Intel® Core™ 2 Duo processor E8000 series Quad-Core Intel® Xeon® processor 5400 series Dual-Core Intel® Xeon® processor 5200 series Intel® Core™2 Duo Processor and Intel® Core™2 Extreme Processor on 45-nm Process Quad-Core Intel® Xeon® processor 3300 series Dual-Core Intel® Xeon® E3110 Processor Intel® Celeron® dual-core processor E1000 series Intel® Core™2 Extreme Processor...

... processor QX9650 and Intel® Core™2 Quad processor Q9000 series Intel® Core™ 2 Duo processor E8000 series Quad-Core Intel® Xeon® processor 5400 series Dual-Core Intel® Xeon® processor 5200 series Intel® Core™2 Duo Processor and Intel® Core™2 Extreme Processor on 45-nm Process Quad-Core Intel® Xeon® processor 3300 series Dual-Core Intel® Xeon® E3110 Processor Intel® Celeron® dual-core processor E1000 series Intel® Core™2 Extreme Processor...

Specification Update

Page 11

...State from SMRAM AI22 X X X X Fixed Sequential Code Fetch to Non-canonical Address May have Non-deterministic Results AI23 X X X X Fixed VMCALL to Activate Dual-monitor Treatment of SMIs and SMM Ignores Reserved Bit settings in VM-exit Control Field AI24 X X X X X No Fix The PECI Controller Resets to the ... X X Fixed (E)CX May Get Incorrectly Updated When Performing Fast String REP MOVS or Fast String REP STOS With Large Data Structures Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 11 Specification Update

...State from SMRAM AI22 X X X X Fixed Sequential Code Fetch to Non-canonical Address May have Non-deterministic Results AI23 X X X X Fixed VMCALL to Activate Dual-monitor Treatment of SMIs and SMM Ignores Reserved Bit settings in VM-exit Control Field AI24 X X X X X No Fix The PECI Controller Resets to the ... X X Fixed (E)CX May Get Incorrectly Updated When Performing Fast String REP MOVS or Fast String REP STOS With Large Data Structures Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 11 Specification Update

Specification Update

Page 12

Summary Tables of Changes NO B1 B2 L2 M0 G0 Plan ERRATA AI31 X X X X Fixed Performance Monitoring Events for Retired Loads (CBH) and Instructions Retired (C0H) May Not Be Accurate AI32 X X X X X No Fix Upper 32 bits of 'From' Address Reported through BTMs or BTSs May be Incorrect AI33 X X X Fixed Unsynchronized Cross-Modifying Code Operations Can Cause Unexpected Instruction Execution Results MSRs Actual Frequency Clock Count (IA32_APERF) or Maximum AI34 X X X X X No Fix Frequency Clock Count (IA32_MPERF) May Contain Incorrect Data after a Machine Check Exception (MCE) AI35 X ...

Summary Tables of Changes NO B1 B2 L2 M0 G0 Plan ERRATA AI31 X X X X Fixed Performance Monitoring Events for Retired Loads (CBH) and Instructions Retired (C0H) May Not Be Accurate AI32 X X X X X No Fix Upper 32 bits of 'From' Address Reported through BTMs or BTSs May be Incorrect AI33 X X X Fixed Unsynchronized Cross-Modifying Code Operations Can Cause Unexpected Instruction Execution Results MSRs Actual Frequency Clock Count (IA32_APERF) or Maximum AI34 X X X X X No Fix Frequency Clock Count (IA32_MPERF) May Contain Incorrect Data after a Machine Check Exception (MCE) AI35 X ...

Specification Update

Page 13

... Behavior AI56 X X X X Fixed Update of Read/Write (R/W) or User/Supervisor (U/S) or Present (P) Bits without TLB Shootdown May Cause Unexpected Processor Behavior AI57 X X X X Fixed BTS Message May Be Lost When the STPCLK# Signal is Programmed to Cause VM Exit to Return to a... X X X X No Fix Performance Monitoring Event FP_ASSIST May Not be Set for Non-Single-Step #DB Exception Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 13 Specification Update AI60 X X X X X No Fix MOV To/From Debug Registers Causes ...

... Behavior AI56 X X X X Fixed Update of Read/Write (R/W) or User/Supervisor (U/S) or Present (P) Bits without TLB Shootdown May Cause Unexpected Processor Behavior AI57 X X X X Fixed BTS Message May Be Lost When the STPCLK# Signal is Programmed to Cause VM Exit to Return to a... X X X X No Fix Performance Monitoring Event FP_ASSIST May Not be Set for Non-Single-Step #DB Exception Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 13 Specification Update AI60 X X X X X No Fix MOV To/From Debug Registers Causes ...

Specification Update

Page 14

... Performance Monitoring Version 2 is Supported, When Only Version 1 Capabilities are Available AI87 X X X X X No Fix Unaligned Accesses to Paging Structures May Cause the Processor to Hang AI88 X X X X X No Fix Microcode Updates Performed During VMX Non-root Operation Could Result in Unexpected Behavior AI89 X X X X X No...X X X X Fixed The Stack Size May be Incorrect as a Result of VIP/VIF Check on SYSEXIT and SYSRET 14 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update

... Performance Monitoring Version 2 is Supported, When Only Version 1 Capabilities are Available AI87 X X X X X No Fix Unaligned Accesses to Paging Structures May Cause the Processor to Hang AI88 X X X X X No Fix Microcode Updates Performed During VMX Non-root Operation Could Result in Unexpected Behavior AI89 X X X X X No...X X X X Fixed The Stack Size May be Incorrect as a Result of VIP/VIF Check on SYSEXIT and SYSRET 14 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update

Specification Update

Page 15

... May Result in a Processor Hang AI115 X X X X X No Fix Instruction Fetch May Cause a Livelock During Snoops of the L1 Data Cache AI116 X X X X X No Fix Use of Memory Aliasing with Inconsistent Memory Type may Cause a System Hang or a Machine Check Exception Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence...

... May Result in a Processor Hang AI115 X X X X X No Fix Instruction Fetch May Cause a Livelock During Snoops of the L1 Data Cache AI116 X X X X X No Fix Use of Memory Aliasing with Inconsistent Memory Type may Cause a System Hang or a Machine Check Exception Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence...

Specification Update

Page 16

There are no Documentation Changes in this Specification Update revision. § 16 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update There are Not Cleared When the Processor is Reset AI122 X Fixed VTPR Access May Lead to System Hang AI123 X Fixed IA32_MC1_STATUS MSR Bit[60] Does Not...

There are no Documentation Changes in this Specification Update revision. § 16 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update There are Not Cleared When the Processor is Reset AI122 X Fixed VTPR Access May Lead to System Hang AI123 X Fixed IA32_MC1_STATUS MSR Bit[60] Does Not...

Specification Update

Page 17

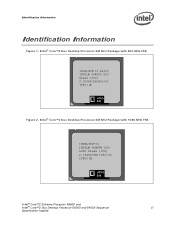

Intel® Core™2 Duo Desktop Processor 2M SKU Package with 800 MHz FSB INTEL M ©'05 E4500 INTEL® CORE™2 DUO SLxxx [COO] 2.20GHZ/2M/800/06 [FPO] e4 ATPO S/N Figure 2. Intel® Core™2 Duo Desktop Processor 2M SKU Package with 1066 MHz FSB INTEL M ©'05 INTEL® CORE™2 DUO 6400 SLxxx [COO] 2.13GHZ/2M/1066/06 [FPO] e4 ATPO S/N Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 17 Specification Update Identification Information Identification Information Figure 1.

Intel® Core™2 Duo Desktop Processor 2M SKU Package with 800 MHz FSB INTEL M ©'05 E4500 INTEL® CORE™2 DUO SLxxx [COO] 2.20GHZ/2M/800/06 [FPO] e4 ATPO S/N Figure 2. Intel® Core™2 Duo Desktop Processor 2M SKU Package with 1066 MHz FSB INTEL M ©'05 INTEL® CORE™2 DUO 6400 SLxxx [COO] 2.13GHZ/2M/1066/06 [FPO] e4 ATPO S/N Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 17 Specification Update Identification Information Identification Information Figure 1.

Specification Update

Page 20

... CPUID instruction is executed with a 2 in the EAX register. NOTES: 1. These parts support Intel® Virtualization Technology (Intel® VT) 5. These parts have THERMTRIP# enabled 9. Component Identification Information Component Identification Information The Intel® Core™2 Extreme processor and Intel® Core™2 Duo desktop processor can be identified by the following notes are provided in the EAX, EBX...

... CPUID instruction is executed with a 2 in the EAX register. NOTES: 1. These parts support Intel® Virtualization Technology (Intel® VT) 5. These parts have THERMTRIP# enabled 9. Component Identification Information Component Identification Information The Intel® Core™2 Extreme processor and Intel® Core™2 Duo desktop processor can be identified by the following notes are provided in the EAX, EBX...

Specification Update

Page 21

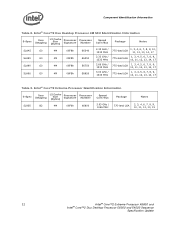

... Information Table 1. Intel® Core™2 Duo Desktop Processor 4M SKU Identification Information S-Spec Core Stepping L2 Cache Size (bytes) Processor Signature Processor Number SLA4U B2 4M 06F6h E6320 SLA4T B2 4M 06F6h E6420 SL9S8 B2 4M 06F6h E6600 SL9ZL B2 4M 06F6h E6600 SL9S7 B2 4M ..., 12, 13, 16 775-land LGA 1, 3, 4, 6, 7, 8, 9, 10, 11, 12, 13, 15 775-land LGA 1, 3, 4, 6, 7, 8, 9, 10, 11, 12, 13, 16 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 21 Specification Update

... Information Table 1. Intel® Core™2 Duo Desktop Processor 4M SKU Identification Information S-Spec Core Stepping L2 Cache Size (bytes) Processor Signature Processor Number SLA4U B2 4M 06F6h E6320 SLA4T B2 4M 06F6h E6420 SL9S8 B2 4M 06F6h E6600 SL9ZL B2 4M 06F6h E6600 SL9S7 B2 4M ..., 12, 13, 16 775-land LGA 1, 3, 4, 6, 7, 8, 9, 10, 11, 12, 13, 15 775-land LGA 1, 3, 4, 6, 7, 8, 9, 10, 11, 12, 13, 16 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 21 Specification Update

Specification Update

Page 22

...-land LGA Notes 2, 3, 4, 6, 7, 8, 9, 10, 11, 12, 13, 15 22 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update Intel® Core™2 Duo Desktop Processor 4M SKU Identification Information S-Spec SLAA5 SLA9X SLA9V SLA9U Core Stepping L2 Cache Size (bytes) Processor Signature Processor Number G0 4M 06FBh E6540 G0 4M 06FBh E6550...

...-land LGA Notes 2, 3, 4, 6, 7, 8, 9, 10, 11, 12, 13, 15 22 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update Intel® Core™2 Duo Desktop Processor 4M SKU Identification Information S-Spec SLAA5 SLA9X SLA9V SLA9U Core Stepping L2 Cache Size (bytes) Processor Signature Processor Number G0 4M 06FBh E6540 G0 4M 06FBh E6550...

Specification Update

Page 23

...-bit L2 ECC errors. AI2. LOCK# Asserted During a Special Cycle Shutdown Transaction May Unexpectedly De-assert Problem: During a processor shutdown transaction, when LOCK# is asserted and if a DEFER# is received during shutdown. Workaround: None identified. Under some scenarios...interrupts that vector was programmed as masked. Intel has not observed this erratum occurs, the system may be used when writing the LVT. Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 23 Specification Update Address...

...-bit L2 ECC errors. AI2. LOCK# Asserted During a Special Cycle Shutdown Transaction May Unexpectedly De-assert Problem: During a processor shutdown transaction, when LOCK# is asserted and if a DEFER# is received during shutdown. Workaround: None identified. Under some scenarios...interrupts that vector was programmed as masked. Intel has not observed this erratum occurs, the system may be used when writing the LVT. Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 23 Specification Update Address...