Data Sheet

Page 1

Intel® Pentium® 4 Processors 570/571, 560/561, 550/551, 540/541, 530/531 and 520/521∆ Supporting Hyper-Threading Technology1 Datasheet On 90 nm Process in 775-land LGA Package and supporting Intel® Extended Memory 64 TechnologyΦ May 2005 Document Number: 302351-004

Intel® Pentium® 4 Processors 570/571, 560/561, 550/551, 540/541, 530/531 and 520/521∆ Supporting Hyper-Threading Technology1 Datasheet On 90 nm Process in 775-land LGA Package and supporting Intel® Extended Memory 64 TechnologyΦ May 2005 Document Number: 302351-004

Data Sheet

Page 2

... arising from published specifications. Current characterized errata are available on request. ∆ Intel processor numbers are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the 775-land package on 90 nm process may contain design defects or errors known as ...including details on which processors support EM64T or consult with your PC manufacturer on the specific hardware and software you use. The Intel® Pentium® 4 processor in the United States and other countries. *Other names and brands may make changes to them. Processor...

... arising from published specifications. Current characterized errata are available on request. ∆ Intel processor numbers are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the 775-land package on 90 nm process may contain design defects or errors known as ...including details on which processors support EM64T or consult with your PC manufacturer on the specific hardware and software you use. The Intel® Pentium® 4 processor in the United States and other countries. *Other names and brands may make changes to them. Processor...

Data Sheet

Page 9

... Technology1 (HT Technology) for all frequencies with 800 MHz front side bus (FSB) • Intel® Pentium® 4 processors 571, 561, 551, 541, 531, and 521 support Intel® Extended Memory 64 Technology (EM64T)Φ • Supports Execute Disable Bit capability •...way cache associativity provides improved cache hit rate on load/store operations • 775-land Package The Intel® Pentium® 4 processor family supporting Hyper-Threading Technology1 (HT Technology) delivers Intel's advanced, powerful processors for 32-bit applications running on advanced 32-bit ...

... Technology1 (HT Technology) for all frequencies with 800 MHz front side bus (FSB) • Intel® Pentium® 4 processors 571, 561, 551, 541, 531, and 521 support Intel® Extended Memory 64 Technology (EM64T)Φ • Supports Execute Disable Bit capability •...way cache associativity provides improved cache hit rate on load/store operations • 775-land Package The Intel® Pentium® 4 processor family supporting Hyper-Threading Technology1 (HT Technology) delivers Intel's advanced, powerful processors for 32-bit applications running on advanced 32-bit ...

Data Sheet

Page 11

... extension architecture and programming model is provided in the 775-land package supports Hyper-Threading Technology1. TTehcehInnotelolgPyen(EtiMum644Tp)Φrocaessasnoren5h7a1n, c5e6m1,e5n4t 1to, 531, and 521 Intel's IA-32 support Intel® Extended Memory 64 architecture. These new instructions ... as platforms with enhancements to the Intel NetBurst® microarchitecture. The Pentium 4 processor on 90 nm process in the 775-land package uses FlipChip Land Grid Array (FC-LGA4) package technology, and plugs into a 775LGA socket. Along with Microsoft Windows* XP Professional...

... extension architecture and programming model is provided in the 775-land package supports Hyper-Threading Technology1. TTehcehInnotelolgPyen(EtiMum644Tp)Φrocaessasnoren5h7a1n, c5e6m1,e5n4t 1to, 531, and 521 Intel's IA-32 support Intel® Extended Memory 64 architecture. These new instructions ... as platforms with enhancements to the Intel NetBurst® microarchitecture. The Pentium 4 processor on 90 nm process in the 775-land package uses FlipChip Land Grid Array (FC-LGA4) package technology, and plugs into a 775LGA socket. Along with Microsoft Windows* XP Professional...

Data Sheet

Page 12

...an active low signal, indicating a signal is not in the 775-land package. • Processor core - The Pentium 4 processor in a Flip- This feature combined with the system board through a surface mount, 775-land, LGA socket. • Integrated heat spreader (IHS) -A component of ...for the processor including heatsink, heatsink retention mechanism, and socket. LGA4 package with integrated L2 cache. • FC-LGA4 package - Intel will also include the Execute Disable Bit capability previously available in the 775-land package - hence, mechanical assembly may be marked as...

...an active low signal, indicating a signal is not in the 775-land package. • Processor core - The Pentium 4 processor in a Flip- This feature combined with the system board through a surface mount, 775-land, LGA socket. • Integrated heat spreader (IHS) -A component of ...for the processor including heatsink, heatsink retention mechanism, and socket. LGA4 package with integrated L2 cache. • FC-LGA4 package - Intel will also include the Execute Disable Bit capability previously available in the 775-land package - hence, mechanical assembly may be marked as...

Data Sheet

Page 13

... independent of the socket. • Storage conditions-Refers to a non-operational state. References Document Document Numbers/ Location Intel® Pentium® 4 Processor on 90 nm Process Specification Update http://developer.intel.com/ design/Pentium4/ specupdt/302352.htm Intel® Pentium® 4 Processor...sealed in the 775-Land Package Thermal Design Guidelines http://developer.intel.com/ design/Pentium4/guides/ 302553.htm Voltage Regulator Down (VRD) 10.1 Design Guide For Desktop LGA775 Socket Intel® Architecture Software Developer's Manual IA-32 Intel® Architecture...

... independent of the socket. • Storage conditions-Refers to a non-operational state. References Document Document Numbers/ Location Intel® Pentium® 4 Processor on 90 nm Process Specification Update http://developer.intel.com/ design/Pentium4/ specupdt/302352.htm Intel® Pentium® 4 Processor...sealed in the 775-Land Package Thermal Design Guidelines http://developer.intel.com/ design/Pentium4/guides/ 302553.htm Voltage Regulator Down (VRD) 10.1 Design Guide For Desktop LGA775 Socket Intel® Architecture Software Developer's Manual IA-32 Intel® Architecture...

Data Sheet

Page 15

... lands must be supplied the voltage determined by the receivers to capacitive deratings. This may cause voltages on -chip power distribution, the Pentium 4 processor in the 775-land package has 226 VCC (power), 24 VTT and 273 VSS (ground) lands. Care must be taken in the board design ... 15 The GTL+ bus depends on the system board. FSB and GTLREF Most processor FSB signals use Gunning Transceiver Logic (GTL+) signaling technology. Intel chipsets will also provide on-die termination, thus eliminating the need to VTT. Some GTL+ signals do so can result in Table 2-8. Analog ...

... lands must be supplied the voltage determined by the receivers to capacitive deratings. This may cause voltages on -chip power distribution, the Pentium 4 processor in the 775-land package has 226 VCC (power), 24 VTT and 273 VSS (ground) lands. Care must be taken in the board design ... 15 The GTL+ bus depends on the system board. FSB and GTLREF Most processor FSB signals use Gunning Transceiver Logic (GTL+) signaling technology. Intel chipsets will also provide on-die termination, thus eliminating the need to VTT. Some GTL+ signals do so can result in Table 2-8. Analog ...

Data Sheet

Page 16

... of System Core Frequency to the Voltage Regulator Down (VRD) 10.1 Design Guide For Desktop LGA775 Socket. 2.3.2 FSB GTL+ Decoupling The Pentium 4 processor in the 775-land package core frequency is a multiple of the processor. Individual processors operate only at its default ratio...implementation. No user intervention is powering on the package. Notes1, 2 - 16 Datasheet Table 2-1. The Pentium 4 processor in the 775-land package clocking, refer to the socket. Bulk decoupling for the large current swings when the part is necessary, and the processor will be provided...

... of System Core Frequency to the Voltage Regulator Down (VRD) 10.1 Design Guide For Desktop LGA775 Socket. 2.3.2 FSB GTL+ Decoupling The Pentium 4 processor in the 775-land package core frequency is a multiple of the processor. Individual processors operate only at its default ratio...implementation. No user intervention is powering on the package. Notes1, 2 - 16 Datasheet Table 2-1. The Pentium 4 processor in the 775-land package clocking, refer to the socket. Bulk decoupling for the large current swings when the part is necessary, and the processor will be provided...

Data Sheet

Page 17

...a relaxed minimum voltage specification. See the Voltage Regulator Down (VRD) 10.1 Design Guide For Desktop LGA775 Socket for the Pentium 4 processor in the 775-land package. The voltage set such that two devices at a higher frequency to configure the proper VTT ...2.4 Electrical Specifications Voltage Identification The VID specification for the Pentium 4 processor in the 775-land package. LL_ID[1:0] = 00 for the Pentium 4 processor in the 775-land package. GTLREF_SEL = 0 for the Pentium 4 processor in the 775-land package is used by the Voltage Regulator Down ...

...a relaxed minimum voltage specification. See the Voltage Regulator Down (VRD) 10.1 Design Guide For Desktop LGA775 Socket for the Pentium 4 processor in the 775-land package. The voltage set such that two devices at a higher frequency to configure the proper VTT ...2.4 Electrical Specifications Voltage Identification The VID specification for the Pentium 4 processor in the 775-land package. LL_ID[1:0] = 00 for the Pentium 4 processor in the 775-land package. GTLREF_SEL = 0 for the Pentium 4 processor in the 775-land package is used by the Voltage Regulator Down ...

Data Sheet

Page 19

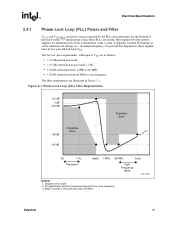

... core timings (i.e., maximum frequency). Jitter is detrimental to core frequency The filter requirements are power sources required by the PLL clock generators for the Pentium 4 processor in the 775-land package. Phase Lock Loop (PLL) Filter Requirements 0.2 dB 0 dB -0.5 dB -28 dB Forbidden Zone -34 dB Forbidden Zone DC 1 Hz Passband fpeak...

... core timings (i.e., maximum frequency). Jitter is detrimental to core frequency The filter requirements are power sources required by the PLL clock generators for the Pentium 4 processor in the 775-land package. Phase Lock Loop (PLL) Filter Requirements 0.2 dB 0 dB -0.5 dB -28 dB Forbidden Zone -34 dB Forbidden Zone DC 1 Hz Passband fpeak...

Data Sheet

Page 20

... with other TESTHI signals • TESTHI11 - cannot be terminated on the processor silicon. Unused outputs can result in the 775-land package to allow for more details. FCx signals are signals that do not include on the system board or left ...a matched resistor has a resistance value within the processor silicon. TAP, GTL+ Asynchronous inputs, and GTL+ Asynchronous outputs do not include on the Pentium 4 processor in component malfunction or incompatibility with other signal (including each group: • TESTHI[1:0] • TESTHI[7:2] • TESTHI8 - Unused...

... with other TESTHI signals • TESTHI11 - cannot be terminated on the processor silicon. Unused outputs can result in the 775-land package to allow for more details. FCx signals are signals that do not include on the system board or left ...a matched resistor has a resistance value within the processor silicon. TAP, GTL+ Asynchronous inputs, and GTL+ Asynchronous outputs do not include on the Pentium 4 processor in component malfunction or incompatibility with other signal (including each group: • TESTHI[1:0] • TESTHI[7:2] • TESTHI8 - Unused...

Data Sheet

Page 23

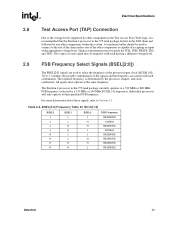

... 2.8 Test Access Port (TAP) Connection Due to Section 4.2. A translation buffer should be first in the 775-land package currently operates at a 533 MHz or 800 MHz FSB frequency (selected by a 133 MHz or... L H H H H L RESERVED H 133 MHz H RESERVED L 200 MHz L RESERVED H RESERVED H RESERVED L RESERVED Datasheet 23 The required frequency is capable of accepting an input of each combination. The Pentium 4 processor in the TAP chain and followed by any other components is determined by other components in the Test Access Port (TAP) logic, it is...

... 2.8 Test Access Port (TAP) Connection Due to Section 4.2. A translation buffer should be first in the 775-land package currently operates at a 533 MHz or 800 MHz FSB frequency (selected by a 133 MHz or... L H H H H L RESERVED H 133 MHz H RESERVED L 200 MHz L RESERVED H RESERVED H RESERVED L RESERVED Datasheet 23 The required frequency is capable of accepting an input of each combination. The Pentium 4 processor in the TAP chain and followed by any other components is determined by other components in the Test Access Port (TAP) logic, it is...

Data Sheet

Page 24

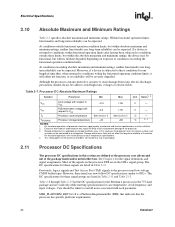

Storage within absolute maximum and minimum ratings, neither functionality nor long-term reliability can be satisfied. 2. The DC specifications for the Pentium 4 processor in the 775-land package and are listed in the GTL+ signal group. Table 2-7. TSTORAGE Processor storage temperature -40 +85 °C 3, 4 NOTES: 1. For functional operation, all notes associated ...

Storage within absolute maximum and minimum ratings, neither functionality nor long-term reliability can be satisfied. 2. The DC specifications for the Pentium 4 processor in the 775-land package and are listed in the GTL+ signal group. Table 2-7. TSTORAGE Processor storage temperature -40 +85 °C 3, 4 NOTES: 1. For functional operation, all notes associated ...

Data Sheet

Page 33

... These specifications apply to the Voltage Regulator Down (VRD) 10.1 Design Guide For Desktop LGA775 Socket for additional voltage regulator validation details. Table 2-17. VCC Overshoot Example Waveform Example Overshoot Waveform ...and VSS_SENSE lands. Overshoot events that are < 10 ns in the 775-land package can tolerate short transient overshoot events where VCC exceeds the ...TOS_MAX is measured time duration above VID. Electrical Specifications 2.12 VCC Overshoot Specification The Pentium 4 processor in duration may be taken with a 100 MHz bandwidth limited oscilloscope. ...

... These specifications apply to the Voltage Regulator Down (VRD) 10.1 Design Guide For Desktop LGA775 Socket for additional voltage regulator validation details. Table 2-17. VCC Overshoot Example Waveform Example Overshoot Waveform ...and VSS_SENSE lands. Overshoot events that are < 10 ns in the 775-land package can tolerate short transient overshoot events where VCC exceeds the ...TOS_MAX is measured time duration above VID. Electrical Specifications 2.12 VCC Overshoot Specification The Pentium 4 processor in duration may be taken with a 100 MHz bandwidth limited oscilloscope. ...

Data Sheet

Page 35

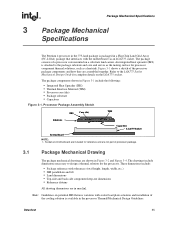

...drawings are shown in Figure 3-2 and Figure 3-4. Processor Package Assembly Sketch IHS Core (die) TIM Substrate Capacitors LGA775 Socket System Board NOTE: 1. Socket and motherboard are included for reference and are not part of the processor package components and how they are in ...mm [in]. Package Mechanical Specifications 3 Package Mechanical Specifications The Pentium 4 processor in the 775-land package is attached to the LGA775 Socket Mechanical Design Guide for complete details on a substrate land-carrier. Refer to the package substrate ...

...drawings are shown in Figure 3-2 and Figure 3-4. Processor Package Assembly Sketch IHS Core (die) TIM Substrate Capacitors LGA775 Socket System Board NOTE: 1. Socket and motherboard are included for reference and are not part of the processor package components and how they are in ...mm [in]. Package Mechanical Specifications 3 Package Mechanical Specifications The Pentium 4 processor in the 775-land package is attached to the LGA775 Socket Mechanical Design Guide for complete details on a substrate land-carrier. Refer to the package substrate ...

Data Sheet

Page 40

... S-Spec/CountryofAssy FPO 2-DMatrixMark INTEL m ©'04 Pentium® 4 3.60GHz/1M/800/04B SLxxx [COO] [FPO] ATPO S/N UniqueUnit Identifier ATPO Serial# 40 Datasheet The socket should meet the LGA775 requirements detailed in the LGA775 Socket Mechanical Design Guide. 3.6 Processor Mass Specification The typical mass of the Pentium 4 processor in the 775-land package. This mass [weight...

... S-Spec/CountryofAssy FPO 2-DMatrixMark INTEL m ©'04 Pentium® 4 3.60GHz/1M/800/04B SLxxx [COO] [FPO] ATPO S/N UniqueUnit Identifier ATPO Serial# 40 Datasheet The socket should meet the LGA775 requirements detailed in the LGA775 Socket Mechanical Design Guide. 3.6 Processor Mass Specification The typical mass of the Pentium 4 processor in the 775-land package. This mass [weight...

Data Sheet

Page 41

Package Mechanical Specifications Figure 3-6. Datasheet 41 The coordinates are referred to throughout the document to identify processor lands. Processor Top-Side Marking Example for Processors Supporting Intel® EM64T ProcessorNumber/S-Spec/ CountryofAssy Frequency/L2Cache/Bus/ 775_VR_CONFIG_04x FPO 2-DMatrixMark INTEL m © '04 Pentium ® 4 571 SLxxx [COO] 3.80GHZ/1M/800/04B [FPO] ATPO S/N Unique Unit Identifier ATPO Serial# 3.9 Processor Land Coordinates Figure 3-7 shows the top view of the processor land coordinates.

Package Mechanical Specifications Figure 3-6. Datasheet 41 The coordinates are referred to throughout the document to identify processor lands. Processor Top-Side Marking Example for Processors Supporting Intel® EM64T ProcessorNumber/S-Spec/ CountryofAssy Frequency/L2Cache/Bus/ 775_VR_CONFIG_04x FPO 2-DMatrixMark INTEL m © '04 Pentium ® 4 571 SLxxx [COO] 3.80GHZ/1M/800/04B [FPO] ATPO S/N Unique Unit Identifier ATPO Serial# 3.9 Processor Land Coordinates Figure 3-7 shows the top view of the processor land coordinates.

Data Sheet

Page 43

... ordering is also a listing of each signal on the package land array (top view). Processor Land Assignments This section contains the land listings for the Pentium 4 processor in Figure 4-1 and Figure 4-2. Datasheet 43 Table 4-1 is shown in the...

... ordering is also a listing of each signal on the package land array (top view). Processor Land Assignments This section contains the land listings for the Pentium 4 processor in Figure 4-1 and Figure 4-2. Datasheet 43 Table 4-1 is shown in the...

Data Sheet

Page 67

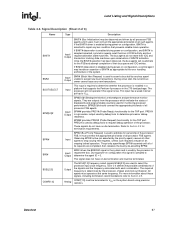

... termination and must be terminated to signal any new transactions. During a bus stall, the current bus owner cannot issue any bus condition that supports the Pentium 4 processor in the system and is low. Input BPRI# (Bus Priority Request) is determined by debug tools to request debug operation of all other agents... such agents. They are breakpoint and performance monitor signals. Observing BPRI# active (as appropriate to Section 2.9. Input/ Output BR0# drives the BREQ0# signal in the 775-land package.

... termination and must be terminated to signal any new transactions. During a bus stall, the current bus owner cannot issue any bus condition that supports the Pentium 4 processor in the system and is low. Input BPRI# (Bus Priority Request) is determined by debug tools to request debug operation of all other agents... such agents. They are breakpoint and performance monitor signals. Observing BPRI# active (as appropriate to Section 2.9. Input/ Output BR0# drives the BREQ0# signal in the 775-land package.

Data Sheet

Page 70

IGNNE# has no effect when the NE bit in the 775-land package. IGNNE# is disabled, the LINT0 signal becomes INTR, a maskable interrupt request signal, and LINT1 becomes NMI, a nonmaskable interrupt. INIT# is an asynchronous ... by the following an Input/Output write instruction, it observes LOCK# de-asserted. For more details regarding machine check architecture, refer to arbitrate for the Pentium 4 processor in control register 0 (CR0) is sampled active on a noncontrol floating-point instruction if a previous floating-point instruction caused an error. Signal Description (Sheet 5 ...

IGNNE# has no effect when the NE bit in the 775-land package. IGNNE# is disabled, the LINT0 signal becomes INTR, a maskable interrupt request signal, and LINT1 becomes NMI, a nonmaskable interrupt. INIT# is an asynchronous ... by the following an Input/Output write instruction, it observes LOCK# de-asserted. For more details regarding machine check architecture, refer to arbitrate for the Pentium 4 processor in control register 0 (CR0) is sampled active on a noncontrol floating-point instruction if a previous floating-point instruction caused an error. Signal Description (Sheet 5 ...