Design Guide

Page 17

Intel® 820 Chipset Platform Performance Desktop Block Diagram Processor 4X AGP Graphics Controller AGP 2.0 82820 Memory Controller Hub (MCH) Main Memory 4 IDE Drives 2 USB Ports Hub Interface PCI Bus PCI Slots AC'97 Codec(s) (optional) AC'97 2.1 82801AA I/O Controller Hub (ICH) Keyboard, Mouse, FD, PP, SP, IR LPC I/F Super I/O FWH Flash BIOS GPIO Intel®820 Chipset Design Guide 1-5 Figure 1-1. Introduction 1.3.3 System Configuration The following figures show typical platform configurations using the Intel® 820 chipset.

Intel® 820 Chipset Platform Performance Desktop Block Diagram Processor 4X AGP Graphics Controller AGP 2.0 82820 Memory Controller Hub (MCH) Main Memory 4 IDE Drives 2 USB Ports Hub Interface PCI Bus PCI Slots AC'97 Codec(s) (optional) AC'97 2.1 82801AA I/O Controller Hub (ICH) Keyboard, Mouse, FD, PP, SP, IR LPC I/F Super I/O FWH Flash BIOS GPIO Intel®820 Chipset Design Guide 1-5 Figure 1-1. Introduction 1.3.3 System Configuration The following figures show typical platform configurations using the Intel® 820 chipset.

Design Guide

Page 34

...on the Direct Rambus* Channel are too wide to work properly. DQB[8:0] - This thinner prepreg allows 18 mil wide traces to the termination. 2-8 Intel®820 Chipset Design Guide Direct Rambus* Layout Guidelines The signals on page 5-1). SIO • Clocking Signals - CFM, CFM# RSL Routing The RSL... groups are essential for the Direct RDRAM interface to break out of the two rows of RSL balls on the right. All unpopulated slots must have continuity modules in place to ensure that the signals propagate to meet the 28 Ω (±10%) nominal impedance requirement...

...on the Direct Rambus* Channel are too wide to work properly. DQB[8:0] - This thinner prepreg allows 18 mil wide traces to the termination. 2-8 Intel®820 Chipset Design Guide Direct Rambus* Layout Guidelines The signals on page 5-1). SIO • Clocking Signals - CFM, CFM# RSL Routing The RSL... groups are essential for the Direct RDRAM interface to break out of the two rows of RSL balls on the right. All unpopulated slots must have continuity modules in place to ensure that the signals propagate to meet the 28 Ω (±10%) nominal impedance requirement...

Design Guide

Page 72

The 82820 MCH should be placed in the center of the bus. For 2-way processor / Intel® 820 chipset designs, a termination card must be placed on the base board. Segment Descriptions and Lengths for the investigated topology shown in Figure 2-36. Segment lengths are met. This ...2-37 shows the topology and trace lengths required for 133 MHz and 100 MHz 2-way processor/Intel® 820 chipset designs. Figure 2-37. The SC242 connectors should be placed electrically in the unused slot when only one processor is necessary to Centerpoint 1.5 L3 Chip set on either end of the ...

The 82820 MCH should be placed in the center of the bus. For 2-way processor / Intel® 820 chipset designs, a termination card must be placed on the base board. Segment Descriptions and Lengths for the investigated topology shown in Figure 2-36. Segment lengths are met. This ...2-37 shows the topology and trace lengths required for 133 MHz and 100 MHz 2-way processor/Intel® 820 chipset designs. Figure 2-37. The SC242 connectors should be placed electrically in the unused slot when only one processor is necessary to Centerpoint 1.5 L3 Chip set on either end of the ...

Design Guide

Page 81

... VREF generation is needed at the MCH component. These signals may violate the ringback specifications. Intel®820 Chipset Design Guide 2-55 Guidelines for VREF distribution and decoupling are contained in "Slot 1 Processor Power Distribution Guidelines." • Special Case AGTL+ signals for VREF generation at the...signals in separate groups to isolate AGTL+ signals from signals that have larger voltage swings, such as 5V PCI. • Select a board stack-up that can create a large undershoot, followed by two agents on the same clock edge, the two falling wave fronts will ...

... VREF generation is needed at the MCH component. These signals may violate the ringback specifications. Intel®820 Chipset Design Guide 2-55 Guidelines for VREF distribution and decoupling are contained in "Slot 1 Processor Power Distribution Guidelines." • Special Case AGTL+ signals for VREF generation at the...signals in separate groups to isolate AGTL+ signals from signals that have larger voltage swings, such as 5V PCI. • Select a board stack-up that can create a large undershoot, followed by two agents on the same clock edge, the two falling wave fronts will ...

Design Guide

Page 90

... provides an AMR connector, it is asserted by setting the shutoff bit to ground. • AMR Slot Special Connections - The motherboard can implement any SDATAIN signal that can be supported in a floating state if the pins are not required. An AMR card using... be routed through a weak (approximately 10 KΩ) pull-down resistors. Care should have an external pull-down . 2-64 Intel®820 Chipset Design Guide If the motherboard implements an active primary codec on the AMR card should not be disabled via a hardware jumper or stuffing option, then its SDATAIN...

... provides an AMR connector, it is asserted by setting the shutoff bit to ground. • AMR Slot Special Connections - The motherboard can implement any SDATAIN signal that can be supported in a floating state if the pins are not required. An AMR card using... be routed through a weak (approximately 10 KΩ) pull-down resistors. Care should have an external pull-down . 2-64 Intel®820 Chipset Design Guide If the motherboard implements an active primary codec on the AMR card should not be disabled via a hardware jumper or stuffing option, then its SDATAIN...

Design Guide

Page 129

... CLK 3.3V LPC Interface Clock LPC CLK Hub Interface/AGP Bus Clock MCH CLK66 4 3V66[0-3] Hub Interface Clock AGP Bus Clock Unused ICH AGP device/ slot N/A CLK66 CLK N/A 66 MHz 3.3V 2 REF[0-1] Internal ICH Logic ICH Internal Super I/O Logic Super I/O CLK14 Vendor Specific 14 MHz 3.3V 1 48 MHz USB ... the clocks listed in the power delivery system for the rest of the output clock are two clock generator components required in an Intel® 820 chipset based system. Table 4-1. These power supplies should be a clean as possible. The MCH uses the same clock for an...

... CLK 3.3V LPC Interface Clock LPC CLK Hub Interface/AGP Bus Clock MCH CLK66 4 3V66[0-3] Hub Interface Clock AGP Bus Clock Unused ICH AGP device/ slot N/A CLK66 CLK N/A 66 MHz 3.3V 2 REF[0-1] Internal ICH Logic ICH Internal Super I/O Logic Super I/O CLK14 Vendor Specific 14 MHz 3.3V 1 48 MHz USB ... the clocks listed in the power delivery system for the rest of the output clock are two clock generator components required in an Intel® 820 chipset based system. Table 4-1. These power supplies should be a clean as possible. The MCH uses the same clock for an...

Design Guide

Page 130

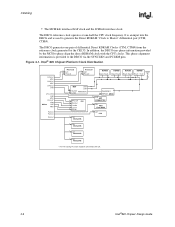

...CTM, CTM#). In addition, the DRCG uses phase information provided by the CK133. The DRCG generates one -half the CPU clock frequency. Intel® 820 Chipset Platform Clock Distribution CPUCLK APIC CPUCLK APIC CPUCLK 3V66 CPU_DIV2 3V66 APIC PCICLK* 3V66 CK133 REF 48Hz PCICLK PCICLK PCICLK ... TERM RCLK TCLK MCH CTM CFM E F HCLKIN CLK66 PHASEINFO G APICCLK ICH H PCICLK I CLK66 J CLK14 K CLK48 L CLK PCI SLOTS L CLK PCI SLOTS L CLK PCI SLOTS L CLK PCI SLOTS PHASEINFO Q REFCLK DRCG P CLK AGP CONNECTOR N CLK FWH Flash BIOS M CLK LPC * The free-running PCI clock should be connected ...

...CTM, CTM#). In addition, the DRCG uses phase information provided by the CK133. The DRCG generates one -half the CPU clock frequency. Intel® 820 Chipset Platform Clock Distribution CPUCLK APIC CPUCLK APIC CPUCLK 3V66 CPU_DIV2 3V66 APIC PCICLK* 3V66 CK133 REF 48Hz PCICLK PCICLK PCICLK ... TERM RCLK TCLK MCH CTM CFM E F HCLKIN CLK66 PHASEINFO G APICCLK ICH H PCICLK I CLK66 J CLK14 K CLK48 L CLK PCI SLOTS L CLK PCI SLOTS L CLK PCI SLOTS L CLK PCI SLOTS PHASEINFO Q REFCLK DRCG P CLK AGP CONNECTOR N CLK FWH Flash BIOS M CLK LPC * The free-running PCI clock should be connected ...

Design Guide

Page 132

... 5.3" ±0" Note: Tie CPUCLK for the MCH to CPUCLK to the SC242 to eliminate pin-to-pin skew. 3V66 Clock for Z AGP Slot PCI Clock for Z PCI Slots 3V66 Clock for Z MCH and ICH Z PCI Clock for ICH 1.5" 4" 4" ±TBD3 ±0" ±0" PCI Clock for the AGP... connector to eliminate pin-to 3V66 clock for On-Board Z Devices (excluding ICH) 4" ±TBD3 Note: 1. The TBD value will be derived from the PCI Revision 2.2 Specification which allows for a maximum of ±2ns clock skew. 820 lk t d 4-4 Intel®820 Chipset Design Guide Figure 4-2.

... 5.3" ±0" Note: Tie CPUCLK for the MCH to CPUCLK to the SC242 to eliminate pin-to-pin skew. 3V66 Clock for Z AGP Slot PCI Clock for Z PCI Slots 3V66 Clock for Z MCH and ICH Z PCI Clock for ICH 1.5" 4" 4" ±TBD3 ±0" ±0" PCI Clock for the AGP... connector to eliminate pin-to 3V66 clock for On-Board Z Devices (excluding ICH) 4" ±TBD3 Note: 1. The TBD value will be derived from the PCI Revision 2.2 Specification which allows for a maximum of ±2ns clock skew. 820 lk t d 4-4 Intel®820 Chipset Design Guide Figure 4-2.

Design Guide

Page 133

...CLK CLK PCICLK-F CLK CLK GCLKIN CLK66 CLK CLK48 BCLK BCLK HCLKIN Refclk PICCLK PICCLK APICCLK CTM/CTM# HCLKOUT RCLKOUT Intel®820 Chipset Design Guide 4-5 Intel® 820 Chipset Platform System Clock Cross-Reference CK133/DRCG Pin Name PCICLK 3V66 48 MHz CPUCLK CPU_div2 APIC Clk/...ClkB1 CFM/CFM#1,2 PclkM SynclkN Component PCI Slot PCI Slot PCI Slot PCI Slot PCI Slot ICH LPC Super I/O FWH Flash BIOS MCH ICH AGP Connector (on-board device) ICH...

...CLK CLK PCICLK-F CLK CLK GCLKIN CLK66 CLK CLK48 BCLK BCLK HCLKIN Refclk PICCLK PICCLK APICCLK CTM/CTM# HCLKOUT RCLKOUT Intel®820 Chipset Design Guide 4-5 Intel® 820 Chipset Platform System Clock Cross-Reference CK133/DRCG Pin Name PCICLK 3V66 48 MHz CPUCLK CPU_div2 APIC Clk/...ClkB1 CFM/CFM#1,2 PclkM SynclkN Component PCI Slot PCI Slot PCI Slot PCI Slot PCI Slot ICH LPC Super I/O FWH Flash BIOS MCH ICH AGP Connector (on-board device) ICH...

Design Guide

Page 155

...a resistive drop through the 5V Dual Switch that during the maximum load-step of : • VRM 8.4 DC-DC Converter Design Guidelines • Slot 1 Power Delivery Guidelines Note: This regulator is powered from the 5V Dual power plane using a switching regulator. Refer to -RAM and therefore, the...connects to the RIMMs. The VCMOS rail requires a maximum of VCMOS are voltage regulators (to regulate to onboard voltage regulators, the Intel® 820 Chipset Reference Board will have a 5V Dual Switch. 5V Dual Switch This switch powers the 5V Dual plane from 2.5VSBY. Note: This switch...

...a resistive drop through the 5V Dual Switch that during the maximum load-step of : • VRM 8.4 DC-DC Converter Design Guidelines • Slot 1 Power Delivery Guidelines Note: This regulator is powered from the 5V Dual power plane using a switching regulator. Refer to -RAM and therefore, the...connects to the RIMMs. The VCMOS rail requires a maximum of VCMOS are voltage regulators (to regulate to onboard voltage regulators, the Intel® 820 Chipset Reference Board will have a 5V Dual Switch. 5V Dual Switch This switch powers the 5V Dual plane from 2.5VSBY. Note: This switch...

Design Guide

Page 157

...2.5VSBY regulator. During full-power operation, the system must not be aware of these initialization steps than during the initialization of PCI slots - 1) In addition to the PCI 3.3V aux, the ICH suspend well power requirements must be considered. As a result of... frequency during suspend, the system must be separate from 2.5VSBY (and controlled by SLP_S3#). Note: This regulator is not required in a Intel® 820 chipset based system that during initialization (Section 6.1.3.1, "Option 1: Reduce the Clock Frequency During Initialization" on page 6-6). Therefore, this...

...2.5VSBY regulator. During full-power operation, the system must not be aware of these initialization steps than during the initialization of PCI slots - 1) In addition to the PCI 3.3V aux, the ICH suspend well power requirements must be considered. As a result of... frequency during suspend, the system must be separate from 2.5VSBY (and controlled by SLP_S3#). Note: This regulator is not required in a Intel® 820 chipset based system that during initialization (Section 6.1.3.1, "Option 1: Reduce the Clock Frequency During Initialization" on page 6-6). Therefore, this...

Design Guide

Page 163

... Memory Interface - 266 MHz, 300 MHz, 356 MHz and 400 MHz Direct RDRAM Support • 4 PCI Add-in Slots - Keyboard Controller • AC'97 Bus Connector and Audio Codec • WfM Support • Integrated System Management •... I /O - Floppy Disk Controller - 1 Parallel Port, 2 Serial Ports - APM Rev. 1.2 Compliant • Pentium III on-board VRM 8.4 compliant regulator • 4 Layer Design Intel®820 Chipset Design Guide A-1 Reference Design Schematics: Uni-Processor Reference Design Schematics: Uni-Processor A A.1 Reference Design Feature Set The reference...

... Memory Interface - 266 MHz, 300 MHz, 356 MHz and 400 MHz Direct RDRAM Support • 4 PCI Add-in Slots - Keyboard Controller • AC'97 Bus Connector and Audio Codec • WfM Support • Integrated System Management •... I /O - Floppy Disk Controller - 1 Parallel Port, 2 Serial Ports - APM Rev. 1.2 Compliant • Pentium III on-board VRM 8.4 compliant regulator • 4 Layer Design Intel®820 Chipset Design Guide A-1 Reference Design Schematics: Uni-Processor Reference Design Schematics: Uni-Processor A A.1 Reference Design Feature Set The reference...

Design Guide

Page 183

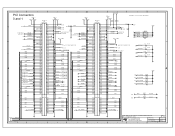

... AD11 AD9 PCLK2 5 PREQ#1 8,32 AD31 AD29 AD27 AD25 C_BE#3 AD23 AD21 AD19 AD17 C_BE#2 IRDY# DEVSEL# PLOCK# PERR# SERR# C_BE#1 AD14 AD12 AD10 PCI Slot 1 J9 PCI3_CON B1 A1 B2 A2 B3 A3 B4 A4 B5 A5 B6 A6 B7 A7 B8 A8 B9 A9 B10 A10 B11 A11 B12... AD13 AD11 AD9 C_BE#0 AD6 AD4 AD16 R120 R_AD16 8,16 20 100 AD17 R119 R_AD17 8,16 20 100 AD2 AD0 A PU2_REQ64# 20 TITLE: INTEL(R) 820 CHIPSET CUSTOMER REFERENCE BOARD REV: PCI CONNECTORS 1 AND 2 1.01 R PCD PLATFORM DESIGN DRAWN BY: PROJECT: 1900 PRAIRIE CITY ROAD FOLSOM, CALIFORNIA 95630 LAST REVISED: SHEET: 11-18...

... AD11 AD9 PCLK2 5 PREQ#1 8,32 AD31 AD29 AD27 AD25 C_BE#3 AD23 AD21 AD19 AD17 C_BE#2 IRDY# DEVSEL# PLOCK# PERR# SERR# C_BE#1 AD14 AD12 AD10 PCI Slot 1 J9 PCI3_CON B1 A1 B2 A2 B3 A3 B4 A4 B5 A5 B6 A6 B7 A7 B8 A8 B9 A9 B10 A10 B11 A11 B12... AD13 AD11 AD9 C_BE#0 AD6 AD4 AD16 R120 R_AD16 8,16 20 100 AD17 R119 R_AD17 8,16 20 100 AD2 AD0 A PU2_REQ64# 20 TITLE: INTEL(R) 820 CHIPSET CUSTOMER REFERENCE BOARD REV: PCI CONNECTORS 1 AND 2 1.01 R PCD PLATFORM DESIGN DRAWN BY: PROJECT: 1900 PRAIRIE CITY ROAD FOLSOM, CALIFORNIA 95630 LAST REVISED: SHEET: 11-18...

Design Guide

Page 184

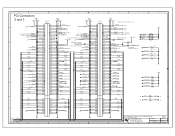

...PCIRST# 6,8,10,11,12,16,19,20,21,22 PGNT#5 8,32 R110 REQ#A 8,32 0K No Stuff R110. FCPGA REFERENCE BOARD REV: PCI CONNECTORS 3 AND 4 1.0 R PCD PLATFORM DESIGN DRAWN BY: PROJECT: 1900 PRAIRIE CITY ROAD FOLSOM, CALIFORNIA 95630 LAST... REVISED: SHEET: 11-9-1999_11:43 21 OF 37 6 5 4 3 2 1 VCC5 PCI Slot 3 J11 PCI3_CON VCC5 VCC12 J9 must be furthest from the processor. PTRST# 20,21 PTMS PTDI 20,21 20,21 20,21 PTCK B1...# 21 PU4_ACK64# 21 B60 A60 B61 A61 PU4_REQ64# 21 B62 A62 TITLE: INTEL(R) 820 CHIPSET -

...PCIRST# 6,8,10,11,12,16,19,20,21,22 PGNT#5 8,32 R110 REQ#A 8,32 0K No Stuff R110. FCPGA REFERENCE BOARD REV: PCI CONNECTORS 3 AND 4 1.0 R PCD PLATFORM DESIGN DRAWN BY: PROJECT: 1900 PRAIRIE CITY ROAD FOLSOM, CALIFORNIA 95630 LAST... REVISED: SHEET: 11-9-1999_11:43 21 OF 37 6 5 4 3 2 1 VCC5 PCI Slot 3 J11 PCI3_CON VCC5 VCC12 J9 must be furthest from the processor. PTRST# 20,21 PTMS PTDI 20,21 20,21 20,21 PTCK B1...# 21 PU4_ACK64# 21 B60 A60 B61 A61 PU4_REQ64# 21 B62 A62 TITLE: INTEL(R) 820 CHIPSET -

Design Guide

Page 198

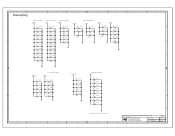

... 0.1UF 0.1UF 0.1UF 0.1UF 0.1UF Termination Decoupling VTT1_5 0.1UF 0.1UF 0.1UF 0.1UF 0.01UF 0.01UF 0.01UF 0.01UF Place caps at VTT pins on Slot 1 connector. 5 4 B A TITLE: INTEL(R) 820 CHIPSET CUSTOMER REFERENCE BOARD REV: BULK DECOUPLING 1.01 R PCD PLATFORM DESIGN DRAWN BY: PROJECT: 1900 PRAIRIE CITY ROAD FOLSOM, CALIFORNIA 95630 LAST REVISED: SHEET: 11-18...

... 0.1UF 0.1UF 0.1UF 0.1UF 0.1UF Termination Decoupling VTT1_5 0.1UF 0.1UF 0.1UF 0.1UF 0.01UF 0.01UF 0.01UF 0.01UF Place caps at VTT pins on Slot 1 connector. 5 4 B A TITLE: INTEL(R) 820 CHIPSET CUSTOMER REFERENCE BOARD REV: BULK DECOUPLING 1.01 R PCD PLATFORM DESIGN DRAWN BY: PROJECT: 1900 PRAIRIE CITY ROAD FOLSOM, CALIFORNIA 95630 LAST REVISED: SHEET: 11-18...

Design Guide

Page 203

... RDRAM Memory Interface - 266 MHz, 300 MHz, 356 MHz and 400 MHz Direct RDRAM Support - 2 RIMM Sockets • 4 PCI Add-in Slots - Keyboard Controller • AC'97 Bus Connector and Audio Codec • WfM Support • Integrated System Management • Integrated Power Management -...Pentium III (SC242) Processors - 100/133 MHz System Bus Frequency - APM Rev. 1.2 Compliant • Pentium III on-board VRM 8.4 compliant regulator • 4 Layer Design Intel®820 Chipset Design Guide B-1 ACPI Rev. 1.0 Compliant - Memory Controller Hub (MCH) - Reference Design Schematics: Dual-...

... RDRAM Memory Interface - 266 MHz, 300 MHz, 356 MHz and 400 MHz Direct RDRAM Support - 2 RIMM Sockets • 4 PCI Add-in Slots - Keyboard Controller • AC'97 Bus Connector and Audio Codec • WfM Support • Integrated System Management • Integrated Power Management -...Pentium III (SC242) Processors - 100/133 MHz System Bus Frequency - APM Rev. 1.2 Compliant • Pentium III on-board VRM 8.4 compliant regulator • 4 Layer Design Intel®820 Chipset Design Guide B-1 ACPI Rev. 1.0 Compliant - Memory Controller Hub (MCH) - Reference Design Schematics: Dual-...

Design Guide

Page 225

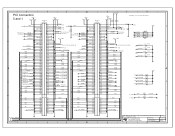

... AD9 PCLK2 7 PREQ#1 10,34 AD31 AD29 AD27 AD25 C_BE#3 AD23 AD21 AD19 AD17 C_BE#2 IRDY# DEVSEL# PLOCK# PERR# SERR# C_BE#1 AD14 AD12 AD10 PCI Slot 1 J11 PCI3_CON B1 A1 B2 A2 B3 A3 B4 A4 B5 A5 B6 A6 B7 A7 B8 A8 B9 A9 B10 A10 B11 A11 B12... R120 R_AD16 10,18,22,23 22 100 AD17 R119 R_AD17 10,18,22,23 22 100 AD2 AD0 A PU2_REQ64# 22 TITLE: INTEL(R) 820 CHIPSET DUAL PROCESSOR CUSTOMER REFERENCE BOARD REV: PCI CONNECTORS 1 AND 2 3.03 R PCD PLATFORM DESIGN DRAWN BY: PROJECT: 1900 PRAIRIE CITY ROAD FOLSOM, CALIFORNIA 95630 LAST REVISED: SHEET: 11...

... AD9 PCLK2 7 PREQ#1 10,34 AD31 AD29 AD27 AD25 C_BE#3 AD23 AD21 AD19 AD17 C_BE#2 IRDY# DEVSEL# PLOCK# PERR# SERR# C_BE#1 AD14 AD12 AD10 PCI Slot 1 J11 PCI3_CON B1 A1 B2 A2 B3 A3 B4 A4 B5 A5 B6 A6 B7 A7 B8 A8 B9 A9 B10 A10 B11 A11 B12... R120 R_AD16 10,18,22,23 22 100 AD17 R119 R_AD17 10,18,22,23 22 100 AD2 AD0 A PU2_REQ64# 22 TITLE: INTEL(R) 820 CHIPSET DUAL PROCESSOR CUSTOMER REFERENCE BOARD REV: PCI CONNECTORS 1 AND 2 3.03 R PCD PLATFORM DESIGN DRAWN BY: PROJECT: 1900 PRAIRIE CITY ROAD FOLSOM, CALIFORNIA 95630 LAST REVISED: SHEET: 11...

Design Guide

Page 226

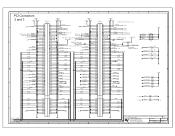

VCC5 PCI Slot 2 J10 PCI3_CON B1 A1 PTCK B2 A2 D 22,23 B3 A3 B4 A4 B5 A5 B6 ...A20 PCIRST# R110 REQ#A 10,34 8,10,12,13,14,18,21,22,23,24 0K No Stuff R110. VCC5 PCI Slot 3 J9 PCI3_CON VCC5 VCC12 J9 must be furthest from the processor. PTRST# 22,23 PTMS PTDI 22,23 22,23 ...AD0 AD1 B58 A58 AD0 B59 A59 A PU3_REQ64# 23 PU4_ACK64# 23 B60 A60 B61 A61 PU4_REQ64# 23 B62 A62 TITLE: INTEL(R) 820 CHIPSET DUAL PROCESSOR CUSTOMER REFERENCE BOARD REV: PCI CONNECTORS 3 AND 4 3.03 R PCD PLATFORM DESIGN DRAWN BY: PROJECT: 1900 PRAIRIE CITY ROAD FOLSOM, CALIFORNIA...

VCC5 PCI Slot 2 J10 PCI3_CON B1 A1 PTCK B2 A2 D 22,23 B3 A3 B4 A4 B5 A5 B6 ...A20 PCIRST# R110 REQ#A 10,34 8,10,12,13,14,18,21,22,23,24 0K No Stuff R110. VCC5 PCI Slot 3 J9 PCI3_CON VCC5 VCC12 J9 must be furthest from the processor. PTRST# 22,23 PTMS PTDI 22,23 22,23 ...AD0 AD1 B58 A58 AD0 B59 A59 A PU3_REQ64# 23 PU4_ACK64# 23 B60 A60 B61 A61 PU4_REQ64# 23 B62 A62 TITLE: INTEL(R) 820 CHIPSET DUAL PROCESSOR CUSTOMER REFERENCE BOARD REV: PCI CONNECTORS 3 AND 4 3.03 R PCD PLATFORM DESIGN DRAWN BY: PROJECT: 1900 PRAIRIE CITY ROAD FOLSOM, CALIFORNIA...

Design Guide

Page 240

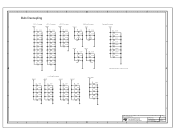

... C65 C89 C106 C108 C114 C64 C345 C344 C343 C342 C364 C363 C357 C351 C346 C365 C149 C150 C151 C152 C153 A A TITLE: INTEL(R) 820 CHIPSET DUAL PROCESSOR CUSTOMER REFERENCE BOARD REV: BULK DECOUPLING 3.03 R PCD PLATFORM DESIGN DRAWN BY: PROJECT: 1900 PRAIRIE CITY ROAD FOLSOM, CALIFORNIA 95630 LAST REVISED: SHEET: 11-29...- 0.01UF 0.1UF 0.1UF 0.1UF 0.1UF 0.01UF C 0.1UF 0.1UF 0.1UF 0.1UF 0.01UF 0.1UF 0.1UF 0.1UF 0.1UF C371 1 2 + 22UF C367 2 1 + 22UF Place caps at VTT pins on Slot 1 connector.

... C65 C89 C106 C108 C114 C64 C345 C344 C343 C342 C364 C363 C357 C351 C346 C365 C149 C150 C151 C152 C153 A A TITLE: INTEL(R) 820 CHIPSET DUAL PROCESSOR CUSTOMER REFERENCE BOARD REV: BULK DECOUPLING 3.03 R PCD PLATFORM DESIGN DRAWN BY: PROJECT: 1900 PRAIRIE CITY ROAD FOLSOM, CALIFORNIA 95630 LAST REVISED: SHEET: 11-29...- 0.01UF 0.1UF 0.1UF 0.1UF 0.1UF 0.01UF C 0.1UF 0.1UF 0.1UF 0.1UF 0.01UF 0.1UF 0.1UF 0.1UF 0.1UF C371 1 2 + 22UF C367 2 1 + 22UF Place caps at VTT pins on Slot 1 connector.