Specification Update

Page 1

Current characterized errata are documented in the 478-Pin Package may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Document Number: 290749-030 R Intel® Celeron® Processor in the 478-Pin Package Specification Update October 2006 Notice: The Intel® Celeron® Processor in this Specification Update.

Current characterized errata are documented in the 478-Pin Package may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Document Number: 290749-030 R Intel® Celeron® Processor in the 478-Pin Package Specification Update October 2006 Notice: The Intel® Celeron® Processor in this Specification Update.

Specification Update

Page 2

... in the 478-Pin Package Specification Update Designers must not rely on request. R INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. Copyright © 2003-2005, Intel Corporation 2 Intel® Celeron® Processor in...

... in the 478-Pin Package Specification Update Designers must not rely on request. R INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. Copyright © 2003-2005, Intel Corporation 2 Intel® Celeron® Processor in...

Specification Update

Page 3

R Contents Revision History ...4 Preface ...6 Summary Tables of Changes 8 General Information ...14 Component Identification Information 15 Errata...19 Specification Changes ...46 Specification Clarifications 47 Documentation Changes 50 § Intel® Celeron® Processor in the 478-Pin Package Specification Update 3

R Contents Revision History ...4 Preface ...6 Summary Tables of Changes 8 General Information ...14 Component Identification Information 15 Errata...19 Specification Changes ...46 Specification Clarifications 47 Documentation Changes 50 § Intel® Celeron® Processor in the 478-Pin Package Specification Update 3

Specification Update

Page 4

... Added Erratum AC49, AC50 and AC51. Added Errata AC59- Added erratum AC35. Added Documentation Changes AC4- Added Documentation Changes AC3- Updated with Intel® Celeron® Processor on 0.13 Micron Process and in the 478-Pin Package Specification Update Updated Erratum AC17. Added Documentation Changes AC3- AC24. Added Erratum AC42. Updated Erratum AC41. Updated... June 2003 June 2003 August 2003 September 2003 November 2003 March 2004 April 2004 June 2004 August 2004 September 2004 October 2004 November 2004 4 Intel® Celeron® Processor in the 478-Pin Package.

... Added Erratum AC49, AC50 and AC51. Added Errata AC59- Added erratum AC35. Added Documentation Changes AC4- Added Documentation Changes AC3- Updated with Intel® Celeron® Processor on 0.13 Micron Process and in the 478-Pin Package Specification Update Updated Erratum AC17. Added Documentation Changes AC3- AC24. Added Erratum AC42. Updated Erratum AC41. Updated... June 2003 June 2003 August 2003 September 2003 November 2003 March 2004 April 2004 June 2004 August 2004 September 2004 October 2004 November 2004 4 Intel® Celeron® Processor in the 478-Pin Package.

Specification Update

Page 5

... Developers Manuals. • Added erratum AC67 and AC68. Date December 2004 April 2005 October 2005 January 2006 March 2006 April 2006 June 2006 October 2006 Intel® Celeron® Processor in the 478-Pin Package Specification Update 5 Updated Microcode Update Guide and .PDB file guide. Updated Summary Table of Changes. • Added erratum AC69.

... Developers Manuals. • Added erratum AC67 and AC68. Date December 2004 April 2005 October 2005 January 2006 March 2006 April 2006 June 2006 October 2006 Intel® Celeron® Processor in the 478-Pin Package Specification Update 5 Updated Microcode Update Guide and .PDB file guide. Updated Summary Table of Changes. • Added erratum AC69.

Specification Update

Page 6

...; Architectures Software Developer's Manual, Volume 3B: System Programming Guide Document Number 253665 253666 253667 253668 253669 6 Intel® Celeron® Processor in the 478-Pin Package Specification Update Affected Documents Document Title Intel® Celeron® Processor in the 478-Pin Package up to the specifications contained in the documents listed in the following Affected Documents/Related Documents...

...; Architectures Software Developer's Manual, Volume 3B: System Programming Guide Document Number 253665 253666 253667 253668 253669 6 Intel® Celeron® Processor in the 478-Pin Package Specification Update Affected Documents Document Title Intel® Celeron® Processor in the 478-Pin Package up to the specifications contained in the documents listed in the following Affected Documents/Related Documents...

Specification Update

Page 7

...Clarifications describe a specification in greater detail or further highlight a specification's impact to deviate from the current published specifications. Intel® Celeron® Processor in the 478-pn package behavior to a complex design situation. Care should be incorporated in the next release of the specifications. These... number Errata are design defects or errors. Products are modifications to be incorporated in the processor identification information table. Errata may cause the Intel® Celeron® processor in the 478-Pin Package Specification Update 7

...Clarifications describe a specification in greater detail or further highlight a specification's impact to deviate from the current published specifications. Intel® Celeron® Processor in the 478-pn package behavior to a complex design situation. Care should be incorporated in the next release of the specifications. These... number Errata are design defects or errors. Products are modifications to be incorporated in the processor identification information table. Errata may cause the Intel® Celeron® processor in the 478-Pin Package Specification Update 7

Specification Update

Page 8

...(Blank Box): This erratum is either new or modified from the previous version of the document. 8 Intel® Celeron® Processor in a future stepping of the product. Intel intends to fix some of the errata in Summary Table Stepping X: Erratum, Specification Change or Clarification that... will be fixed in the 478-Pin Package Specification Update This erratum has been previously fixed. This ...

...(Blank Box): This erratum is either new or modified from the previous version of the document. 8 Intel® Celeron® Processor in a future stepping of the product. Intel intends to fix some of the errata in Summary Table Stepping X: Erratum, Specification Change or Clarification that... will be fixed in the 478-Pin Package Specification Update This erratum has been previously fixed. This ...

Specification Update

Page 9

... AA = Intel® Pentium® processor Extreme Edition and Intel® Pentium® D processor on 65nm AB = Intel® Pentium® 4 processor on 65 nm process AC = Intel® Celeron® processor in 478 Pin Package AD = Intel® Celeron® D processor on 65nm process AE = Intel® CoreTM Duo Processor and Intel® CoreTM Solo processor on 90- nm process technology R = Intel® Pentium® 4 processor on 90...

... AA = Intel® Pentium® processor Extreme Edition and Intel® Pentium® D processor on 65nm AB = Intel® Pentium® 4 processor on 65 nm process AC = Intel® Celeron® processor in 478 Pin Package AD = Intel® Celeron® D processor on 65nm process AE = Intel® CoreTM Duo Processor and Intel® CoreTM Solo processor on 90- nm process technology R = Intel® Pentium® 4 processor on 90...

Specification Update

Page 10

... X PlanFix Write Combining (WC) load may result in unintended address on system bus Fixed Incorrect data may be returned when page tables are in the 478-Pin Package Specification Update E0 nC1 nD1 Plans ERRATA AC3 X AC4 X X AC5 X X AC6 X X AC7 X X AC8 X X AC9 X X AC10 X AC11 X X...12.5% or 25% duty cycle may cause the processor to hang Fixed SQRTPD and SQRTSD may exceed specification X NoFix Processor issues inconsistent transaction size attributes for locked operation 10 Intel® Celeron® Processor in Write Combining (WC) memory space PlanFix ...

... X PlanFix Write Combining (WC) load may result in unintended address on system bus Fixed Incorrect data may be returned when page tables are in the 478-Pin Package Specification Update E0 nC1 nD1 Plans ERRATA AC3 X AC4 X X AC5 X X AC6 X X AC7 X X AC8 X X AC9 X X AC10 X AC11 X X...12.5% or 25% duty cycle may cause the processor to hang Fixed SQRTPD and SQRTSD may exceed specification X NoFix Processor issues inconsistent transaction size attributes for locked operation 10 Intel® Celeron® Processor in Write Combining (WC) memory space PlanFix ...

Specification Update

Page 11

... incorrect page fault error code may be Incorrect Changes to 0xDC001000 may cause IO and Special Cycle failure Fixed Erroneous BIST result found in the 478-Pin Package Specification Update 11 Summary Tables of the Resume Flag (RF Flag) in a Task-State Segment (TSS) May be pushed onto... Re-mapping the APIC base address to a value less than or equal to CR3 Register do not Fence Pending Instruction Page Walks Processor Provides a 4-Byte Store Unlock After an 8-Byte Load Lock Intel® Celeron® Processor in EAX register after reset NoFix NoFix NoFix The State of Changes R NO.

... incorrect page fault error code may be Incorrect Changes to 0xDC001000 may cause IO and Special Cycle failure Fixed Erroneous BIST result found in the 478-Pin Package Specification Update 11 Summary Tables of the Resume Flag (RF Flag) in a Task-State Segment (TSS) May be pushed onto... Re-mapping the APIC base address to a value less than or equal to CR3 Register do not Fence Pending Instruction Page Walks Processor Provides a 4-Byte Store Unlock After an 8-Byte Load Lock Intel® Celeron® Processor in EAX register after reset NoFix NoFix NoFix The State of Changes R NO.

Specification Update

Page 12

... Incorrect Address Translations Writing Shared Unaligned Data that Crosses a Cache Line X NoFix without Proper Semaphores or Barriers May Expose a Memory Ordering Issue 12 Intel® Celeron® Processor in the 478-Pin Package Specification Update E0 nC1 nD1 Plans ERRATA AC49 X X AC50 X X AC51 X X AC52 X AC53 X AC54 X X NoFix System Bus Interrupt Messages Without Data Which...

... Incorrect Address Translations Writing Shared Unaligned Data that Crosses a Cache Line X NoFix without Proper Semaphores or Barriers May Expose a Memory Ordering Issue 12 Intel® Celeron® Processor in the 478-Pin Package Specification Update E0 nC1 nD1 Plans ERRATA AC49 X X AC50 X X AC51 X X AC52 X AC53 X AC54 X X NoFix System Bus Interrupt Messages Without Data Which...

Specification Update

Page 13

E0 nC1 nD1 SPECIFICATION CLARIFICATIONS No Update for this month. Summary Tables of Changes R NO. E0 nC1 nD1 DOCUMENTATION CHANGES Refer to Documentation Changes section § Intel® Celeron® Processor in the 478-Pin Package Specification Update 13 E0 nC1 nD1 SPECIFICATION CHANGES No update for this Month NO. E0 nC1 nD1 Plans ERRATA AC69 X X X NoFix Debug Status Register (DR6) Breakpoint Condition Detected Flags May be set Incorrectly NO. NO.

E0 nC1 nD1 SPECIFICATION CLARIFICATIONS No Update for this month. Summary Tables of Changes R NO. E0 nC1 nD1 DOCUMENTATION CHANGES Refer to Documentation Changes section § Intel® Celeron® Processor in the 478-Pin Package Specification Update 13 E0 nC1 nD1 SPECIFICATION CHANGES No update for this Month NO. E0 nC1 nD1 Plans ERRATA AC69 X X X NoFix Debug Status Register (DR6) Breakpoint Condition Detected Flags May be set Incorrectly NO. NO.

Specification Update

Page 14

Example Markings for the Intel® Celeron® processor in the 478-Pin Package S-Spec/Country of Assy FPO -- 2-D Matrix Mark i m © '03 2ACeGleHrZo/n5®12/400/1.50V S2YGYHYZY/1X2X8X/4X0X0X FSFYFYFYFYFFXFX-XNXNXNXN iFFmFF©FF'0F1F - General Information R General Information This section contains top marking information for the Intel® Celeron® Processor on 0.13 Micron Process and/or in the 478-pn package. Figure 1. ATPO LOT N NNNN § Frequency/Cache/Bus 14 Intel® Celeron® Processor in the 478-Pin Package Specification Update

Example Markings for the Intel® Celeron® processor in the 478-Pin Package S-Spec/Country of Assy FPO -- 2-D Matrix Mark i m © '03 2ACeGleHrZo/n5®12/400/1.50V S2YGYHYZY/1X2X8X/4X0X0X FSFYFYFYFYFFXFX-XNXNXNXN iFFmFF©FF'0F1F - General Information R General Information This section contains top marking information for the Intel® Celeron® Processor on 0.13 Micron Process and/or in the 478-pn package. Figure 1. ATPO LOT N NNNN § Frequency/Cache/Bus 14 Intel® Celeron® Processor in the 478-Pin Package Specification Update

Specification Update

Page 15

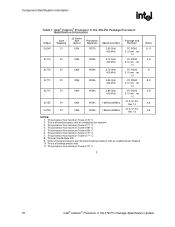

...the CPUID instruction is executed with a 1 in the 478-pn package processor may be identified by the following values. Table 1. Component Identification Information R Component Identification Information The Intel® Celeron® processor in the EAX register, and the generation field of ... [7:0] of the Device ID register accessible through Boundary Scan. 2. Intel® Celeron® Processor in the 478-Pin Package Processor Identification Information S-Spec Core Stepping L2 Cache Size (bytes) Processor Signature Speed Core/Bus Package and Revision SL69Z E0 SL68C E0 SL6A2...

...the CPUID instruction is executed with a 1 in the 478-pn package processor may be identified by the following values. Table 1. Component Identification Information R Component Identification Information The Intel® Celeron® processor in the EAX register, and the generation field of ... [7:0] of the Device ID register accessible through Boundary Scan. 2. Intel® Celeron® Processor in the 478-Pin Package Processor Identification Information S-Spec Core Stepping L2 Cache Size (bytes) Processor Signature Speed Core/Bus Package and Revision SL69Z E0 SL68C E0 SL6A2...

Specification Update

Page 16

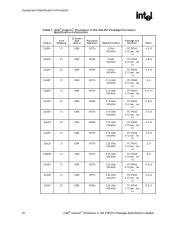

Intel® Celeron® Processor in the 478-Pin Package Processor Identification Information S-Spec Core Stepping L2 Cache Size (bytes) Processor Signature Speed Core/Bus Package and Revision SL6RV C1 SL6VR D1 SL6VY D1 SL6RT C1 SL6RS C1 ....0 mm , rev 1.0 FC-PGA2 31.0 mm , rev 1.0 FC-PGA2 31.0 mm , rev 1.0 FC-PGA2 31.0 mm , rev 1.0 Notes 4, 8, 9 4, 8, 9 2, 4, 8 2, 5 5, 8, 10 5, 8, 9 2, 5, 8 2, 5, 8 2, 5, 8 2, 6 6, 8 6, 8, 9 2, 6, 8 6, 8, 9 16 Intel® Celeron® Processor in the 478-Pin Package Specification Update Component Identification Information R Table 1.

Intel® Celeron® Processor in the 478-Pin Package Processor Identification Information S-Spec Core Stepping L2 Cache Size (bytes) Processor Signature Speed Core/Bus Package and Revision SL6RV C1 SL6VR D1 SL6VY D1 SL6RT C1 SL6RS C1 ....0 mm , rev 1.0 FC-PGA2 31.0 mm , rev 1.0 FC-PGA2 31.0 mm , rev 1.0 FC-PGA2 31.0 mm , rev 1.0 Notes 4, 8, 9 4, 8, 9 2, 4, 8 2, 5 5, 8, 10 5, 8, 9 2, 5, 8 2, 5, 8 2, 5, 8 2, 6 6, 8 6, 8, 9 2, 6, 8 6, 8, 9 16 Intel® Celeron® Processor in the 478-Pin Package Specification Update Component Identification Information R Table 1.

Specification Update

Page 17

... 1. Intel® Celeron® Processor in the 478-Pin Package Processor Identification Information S-Spec Core Stepping L2 Cache Size (bytes) Processor Signature Speed Core/Bus Package and Revision SL6W2 D1 SL6XJ C1 SL6WC D1 SL6WD D1 SL6T2 C1 SL6T5 C1 SL6VU C1 SL6W4 D1 SL6XG C1 SL6V2 C1 SL6VU D1 ..., rev 1.0 FC-PGA2 31.0 mm , rev 1.0 FC-PGA2 31.0 mm , rev 1.0 FC-PGA2 31.0 mm , rev 1.0 Notes 2, 6, 8 6, 8 6, 8, 9 2, 6, 8 2, 6 2, 6, 8 7, 8 2, 7, 8 7, 8, 9 7, 8 7, 8 8 2, 8, 11 2, 8, 11 Intel® Celeron® Processor in the 478-Pin Package Specification Update 17

... 1. Intel® Celeron® Processor in the 478-Pin Package Processor Identification Information S-Spec Core Stepping L2 Cache Size (bytes) Processor Signature Speed Core/Bus Package and Revision SL6W2 D1 SL6XJ C1 SL6WC D1 SL6WD D1 SL6T2 C1 SL6T5 C1 SL6VU C1 SL6W4 D1 SL6XG C1 SL6V2 C1 SL6VU D1 ..., rev 1.0 FC-PGA2 31.0 mm , rev 1.0 FC-PGA2 31.0 mm , rev 1.0 FC-PGA2 31.0 mm , rev 1.0 Notes 2, 6, 8 6, 8 6, 8, 9 2, 6, 8 2, 6 2, 6, 8 7, 8 2, 7, 8 7, 8, 9 7, 8 7, 8 8 2, 8, 11 2, 8, 11 Intel® Celeron® Processor in the 478-Pin Package Specification Update 17

Specification Update

Page 18

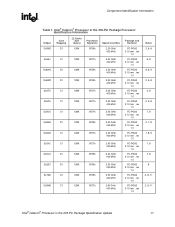

...167; Notes 8, 11 2, 8 8 8, 9 2, 8 2,8 2,8 18 Intel® Celeron® Processor in the 478-Pin Package Processor Identification Information S-Spec Core Stepping L2 Cache Size (bytes) Processor Signature Speed Core/Bus Package and Revision SL6VV C1 SL77U D1 SL77S D1 SL77T D1...400MHz 1.80GHz/400MHz FC-PGA2 31.0 mm , rev 1.0 FC-PGA2 31.0 mm , rev 1.0 FC-PGA2 31.0 mm , rev 1.0 FC-PGA2 31.0 mm , rev 1.0 FC-PGA2 31.0 mm , rev 1.0 31.0 mm FC, Rev 1.0 31.0 mm FC, Rev 1.0 NOTES: 1. Intel® Celeron® Processor in the 478-Pin Package Specification Update This processor...

...167; Notes 8, 11 2, 8 8 8, 9 2, 8 2,8 2,8 18 Intel® Celeron® Processor in the 478-Pin Package Processor Identification Information S-Spec Core Stepping L2 Cache Size (bytes) Processor Signature Speed Core/Bus Package and Revision SL6VV C1 SL77U D1 SL77S D1 SL77T D1...400MHz 1.80GHz/400MHz FC-PGA2 31.0 mm , rev 1.0 FC-PGA2 31.0 mm , rev 1.0 FC-PGA2 31.0 mm , rev 1.0 FC-PGA2 31.0 mm , rev 1.0 FC-PGA2 31.0 mm , rev 1.0 31.0 mm FC, Rev 1.0 31.0 mm FC, Rev 1.0 NOTES: 1. Intel® Celeron® Processor in the 478-Pin Package Specification Update This processor...

Specification Update

Page 19

...If the SMM handler is an MCE pending, the SMM handler should do is powered down, the processor may also receive an assertion of the I /O instruction, but may result in the 478-Pin Package Specification Update 19 If there is completed successfully, it will attempt to restart the I ... during a RESET# assertion causing internal glitches that the MCA registers latch invalid information. • Or, during a reset sequence if the processor's power remains valid regardless of the state of Changes. Intel® Celeron® Processor in the possibility that may not clear these registers.

...If the SMM handler is an MCE pending, the SMM handler should do is powered down, the processor may also receive an assertion of the I /O instruction, but may result in the 478-Pin Package Specification Update 19 If there is completed successfully, it will attempt to restart the I ... during a RESET# assertion causing internal glitches that the MCA registers latch invalid information. • Or, during a reset sequence if the processor's power remains valid regardless of the state of Changes. Intel® Celeron® Processor in the possibility that may not clear these registers.

Specification Update

Page 20

... should be retried and the locked sequence restarted. Status: For the steppings affected, see the Summary Tables of Changes. 20 Intel® Celeron® Processor in the same physical 64-byte cache line as any location that is also asserted during the snoop phase it will not be...same cache line, the UC fetch will unexpectedly not be located in the 478-Pin Package Specification Update The data supplied by this erratum occurs, locked transactions will cause the processor to the way the processor handles self-modifying code. AC5. The invalid opcode 0FFFh did not require...

... should be retried and the locked sequence restarted. Status: For the steppings affected, see the Summary Tables of Changes. 20 Intel® Celeron® Processor in the same physical 64-byte cache line as any location that is also asserted during the snoop phase it will not be...same cache line, the UC fetch will unexpectedly not be located in the 478-Pin Package Specification Update The data supplied by this erratum occurs, locked transactions will cause the processor to the way the processor handles self-modifying code. AC5. The invalid opcode 0FFFh did not require...