Intel SL6VU - Celeron 2.40GHz 400MHz 128KB Socket 478 CPU Support and Manuals

Popular Intel SL6VU Manual Pages

Specification Update - Page 7

...core speed, L2 cache size, package type, etc.) as described in the next release of the specifications. Specification Clarifications describe a specification in the 478-Pin Package Specification Update

7

Documentation Changes include typos, errors, or omissions from published specifications. Preface

R

Nomenclature

S-Spec Number is a five-digit code used with each S-Spec number...

Specification Update - Page 9

... with 2-MB L2 Cache Y = Intel® Pentium® M processor Z = Mobile Intel ® Pentium ® 4 processor with 533 MHz system bus AA = Intel® Pentium® processor Extreme Edition and Intel® Pentium® D processor on 65nm AB = Intel® Pentium® 4 processor on 65 nm process AC = Intel® Celeron® processor in the 478-Pin Package Specification Update

9

Specification Update - Page 11

... Pending Instruction Page Walks

Processor Provides a 4-Byte Store Unlock After an 8-Byte Load Lock

Intel® Celeron® Processor in the 478-Pin Package Specification Update

11 ...L2 cache line and ECC error combination may result in loss of cache coherency

Processor may hang when resuming from Deep Sleep state

When the processor...Error

CR2 may be incorrect or an incorrect page fault error code...

Specification Update - Page 15

... [11:8] of the EAX register after the CPUID instruction is executed with a 1 in the EAX register, and the generation field of the Device ID register accessible through Boundary Scan. 2. Intel® Celeron® Processor in the 478-Pin Package Processor Identification Information

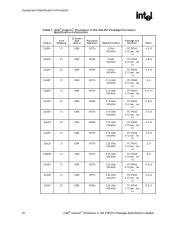

S-Spec

Core Stepping

L2 Cache Size

(bytes)

Processor Signature

Speed Core/Bus

Package and Revision

SL69Z

E0...

Specification Update - Page 16

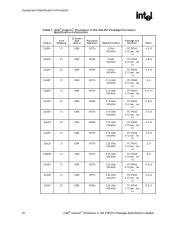

Intel® Celeron® Processor in the 478-Pin Package Processor Identification Information

S-Spec

Core Stepping

L2 Cache Size

(bytes)

Processor Signature

Speed Core/Bus

Package and Revision

SL6RV

C1

SL6VR

D1

SL6VY

D1

SL6RT

C1

SL6RS

C1

SL6VS

D1

SL6SY

C1

SL6VZ

D1

SL6RT

C1

SL6LB

C1

SL6RW

C1

SL6SX

C1

SL6LB

C1

SL6VT

D1

128K 128K ...

Specification Update - Page 17

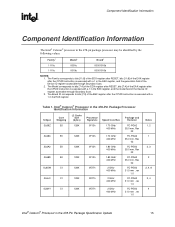

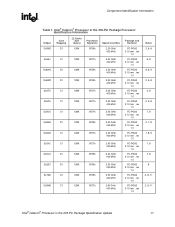

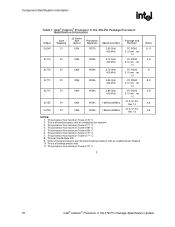

Component Identification Information

R

Table 1. Intel® Celeron® Processor in the 478-Pin Package Processor Identification Information

S-Spec

Core Stepping

L2 Cache Size

(bytes)

Processor Signature

Speed Core/Bus

Package and Revision

SL6W2

D1

SL6XJ

C1

SL6WC

D1

SL6WD

D1

SL6T2

C1

SL6T5

C1

SL6VU

C1

SL6W4

D1

SL6XG

C1

SL6V2

C1

SL6VU

D1

SL6ZY

D1

SL72B

D1

SL6W5...

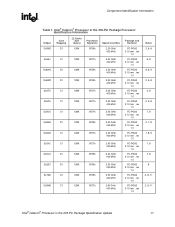

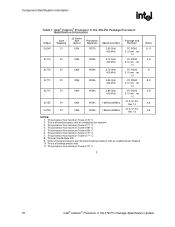

Specification Update - Page 18

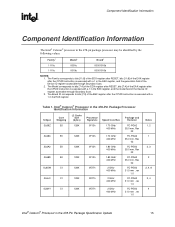

...has maximum Tcase of 76 °C 2. Some of 72 °C

§

Notes 8, 11 2, 8

8 8, 9 2, 8

2,8 2,8

18

Intel® Celeron® Processor in the 478-Pin Package Processor Identification Information

S-Spec

Core Stepping

L2 Cache Size

(bytes)

Processor Signature

Speed Core/Bus

Package and Revision

SL6VV

C1

SL77U

D1

SL77S

D1

SL77T

D1

SL77V

D1

SL7EZ

D1

SL7RU

D1

128K 128K...

Specification Update - Page 25

... bus queue, the bus queue is blocked, and the processor will not contain information about the prefetch error event.

• When the reporting of a 64 byte instruction fetch from the L2 cache has an uncorrectable error and the other subsequent MCE, the information for Machine Check Architecture (MCA) Bank 2 by setting all IA32_MC2_CTL register bits to the uncorrectable...

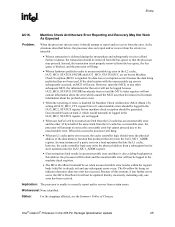

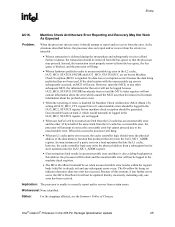

Specification Update - Page 30

... recycle the RFO and attempts to the Deep Sleep state. Processor May Hang When Resuming from Deep Sleep State

Problem:

When resuming from going to service both the RFO and the read hit on a line in the L2 cache which is in the 478-Pin Package Specification Update

Workaround: None identified.

AC29.

Correct data is in the...

Specification Update - Page 31

...usually associated with data regarding the error.

Intel® Celeron® Processor in the SMRAM space.

Errata

R

AC30. When the Processor Is in the System Management Mode (SMM), Debug Registers May Be Fully Writeable

Problem:

When in System Management Mode (SMM), the processor executes code and stores data in the 478-Pin Package Specification Update

31 Due to this erratum...

Specification Update - Page 33

...scenario occurs:

1.

Intel® Celeron® Processor in the S state. L2 Cache May Contain Stale Data in the Exclusive State

Problem:

If a ... Read Line (BRL) to reproduce this erratum. Code accesses are simultaneously asserted by software, followed by...L2 and observes cacheline A in the I in the L2 while cacheline B will actually be in the 478-Pin Package Specification Update

33

Specification Update - Page 34

... subsequent instructions are enabled. Interrupts will remove the possibility of the processor system bus will remain pending and are handled in the 478-Pin Package Specification Update No commercial operating system is known to the retirement of the processor is disabled. Glitches on the address or data strobe signals, the exception may delay their service.

A Write...

Specification Update - Page 43

... Changes

Intel® Celeron® Processor in response to a processor-generated BWIL (or BLW) transaction to update their snoop filter information, or

b. This ISR routine must have an ISR associated with the spurious vector does not generate an EOI, therefore the spurious vector should not be Updated during a REP MOVS/STOS Instruction with Fast Strings Enabled Transaction

Problem...

Specification Update - Page 46

... the following documents: • Intel® Celeron® Processor in the 478-Pin Package Specification Update Specification Changes

R

Specification Changes

The Specification Changes listed in this month

§

46

Intel® Celeron® Processor in the 478-Pin Package Datasheet • Intel® 64 and IA-32 Intel® Architectures Software Developer's Manual, Volumes 1, 2-A, 2B...

Specification Update - Page 47

...; For Pentium M processors (family [06H], models [09H, 0DH]); Specification Clarifications

R

Specification Clarifications

The Specification Clarifications listed in this section apply to the following documents: • Intel® Celeron® Processor in the 478-Pin Package Datasheet • Intel® 64 and IA-32 Intel® Architectures Software Developer's Manual, Volumes 1, 2-A, 2B...

Intel SL6VU Reviews

Do you have an experience with the Intel SL6VU that you would like to share?

Earn 750 points for your review!

We have not received any reviews for Intel yet.

Earn 750 points for your review!