Product Specification

Page 15

...Processors with the VRM 10.1 specification and provides a maximum of 210 Amps, which is capable of installed processors. No manual processor speed setting options exist either in sequential order. The board hardware must monitor the processor VTTEN (Output enable for VTT)... pin of the two processors are not supported. ƒ No terminator is required in a DP configuration. Intel® Server Board SE7320EP2 / Intel® Server Board SE7525RP2 TPS Functional Architecture Notes: ƒ Processors must be populated before turning on the VRD. 3.1.1.2 Reset Configuration Logic...

...Processors with the VRM 10.1 specification and provides a maximum of 210 Amps, which is capable of installed processors. No manual processor speed setting options exist either in sequential order. The board hardware must monitor the processor VTTEN (Output enable for VTT)... pin of the two processors are not supported. ƒ No terminator is required in a DP configuration. Intel® Server Board SE7320EP2 / Intel® Server Board SE7525RP2 TPS Functional Architecture Notes: ƒ Processors must be populated before turning on the VRD. 3.1.1.2 Reset Configuration Logic...

Product Specification

Page 52

... modes. In single mode, the onboard video controller is disabled when an add-in the PCI BIOS Specification. Intel® Server Board SE7320EP2 / Intel® Server Board SE7525RP2 TPS BIOS 6.2.3.2 Resource Assignment The resource manager assigns the PIC-mode interrupt for disabling of legacy ROM posting via...enabled) and the user binary (if present and configured for devices. 6.2.3.4 Option ROMs The BIOS dispatches the option ROMs to manually configure IRQs for runtime usage). The option ROM space is the primary video device. The option to PCI Express devices. 52 Revision...

... modes. In single mode, the onboard video controller is disabled when an add-in the PCI BIOS Specification. Intel® Server Board SE7320EP2 / Intel® Server Board SE7525RP2 TPS BIOS 6.2.3.2 Resource Assignment The resource manager assigns the PIC-mode interrupt for disabling of legacy ROM posting via...enabled) and the user binary (if present and configured for devices. 6.2.3.4 Option ROMs The BIOS dispatches the option ROMs to manually configure IRQs for runtime usage). The option ROM space is the primary video device. The option to PCI Express devices. 52 Revision...

Product Specification

Page 90

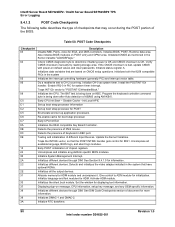

...being done after Auto detection of KB/MS using AMI KB-5. Uncompress and initialize any OEM specific information. Verify CMOS checksum manually by reading storage area. Traps the INT09h vector, so that the POST INT09h handler gets control for ADM module and uncompress...33 37 38 39 3A Description Disable NMI, Parity, video for initialization. Initializes different devices through DIM. Intel® Server Board SE7320EP2 / Intel® Server Board SE7525RP2 TPS Error Logging 9.4.1.2 POST Code Checkpoints The following table describes the type of checkpoints that may occur ...

...being done after Auto detection of KB/MS using AMI KB-5. Uncompress and initialize any OEM specific information. Verify CMOS checksum manually by reading storage area. Traps the INT09h vector, so that the POST INT09h handler gets control for ADM module and uncompress...33 37 38 39 3A Description Disable NMI, Parity, video for initialization. Initializes different devices through DIM. Intel® Server Board SE7320EP2 / Intel® Server Board SE7525RP2 TPS Error Logging 9.4.1.2 POST Code Checkpoints The following table describes the type of checkpoints that may occur ...

Product Specification

Page 94

... that are output to port 80h as follows: HIGH BYTE XY The upper nibble 'X' indicates the function number that include manual configured onboard peripherals, memory and I/O decode windows in PCI-PCI bridges, and noncompliant PCI devices. Static resources are as ... to initialize different system buses. The low byte value indicates the main POST Code Checkpoint. Table 53. Intel® Server Board SE7320EP2 / Intel® Server Board SE7525RP2 TPS Error Logging 9.4.1.5 DIM Code Checkpoints The Device Initialization Manager (DIM) gets control at various times during...

... that are output to port 80h as follows: HIGH BYTE XY The upper nibble 'X' indicates the function number that include manual configured onboard peripherals, memory and I/O decode windows in PCI-PCI bridges, and noncompliant PCI devices. Static resources are as ... to initialize different system buses. The low byte value indicates the main POST Code Checkpoint. Table 53. Intel® Server Board SE7320EP2 / Intel® Server Board SE7525RP2 TPS Error Logging 9.4.1.5 DIM Code Checkpoints The Device Initialization Manager (DIM) gets control at various times during...