Product Specification

Page 4

...29 3.3.2 Serial Ports...29 3.3.3 BIOS Flash...30 4. Table of Contents Intel® Server Board SE7505VB2 Table of Contents 1. Introduction ...13 2. SE7505VB2 Server Board Overview 14 2.1 Intel® Server Board SE7505VB2 Feature Set 14 3. or 66-MHz PCI Subsystem 34 5.2 Serial ... 5.5.2 APIC Interrupt Routing 40 5.5.3 Serialized IRQ Support 41 iv Revision 1.2 Intel part number C32194-002 Functional Architecture ...16 3.1 Processor and Memory Subsystem 16 3.1.1 Processor Support 16 3.1.2 Memory Subsystem 17 3.2 The Intel® E7505 Chipset 21 3.2.1 MCH Memory Architecture...

...29 3.3.2 Serial Ports...29 3.3.3 BIOS Flash...30 4. Table of Contents Intel® Server Board SE7505VB2 Table of Contents 1. Introduction ...13 2. SE7505VB2 Server Board Overview 14 2.1 Intel® Server Board SE7505VB2 Feature Set 14 3. or 66-MHz PCI Subsystem 34 5.2 Serial ... 5.5.2 APIC Interrupt Routing 40 5.5.3 Serialized IRQ Support 41 iv Revision 1.2 Intel part number C32194-002 Functional Architecture ...16 3.1 Processor and Memory Subsystem 16 3.1.1 Processor Support 16 3.1.2 Memory Subsystem 17 3.2 The Intel® E7505 Chipset 21 3.2.1 MCH Memory Architecture...

Product Specification

Page 9

..., J2B2 56 Table 28. P32-A Arbitration Connections 34 Table 10. P64-B Arbitration Connections 35 Table 13. Monitored Components 45 Table 19. Socket 604 Processor Socket Pin-out (U8C1, U5C1 52 Table 25. P32-A 5V 32-bit/33-MHz PCI Slot Pin-out (J4B1, J3B1 55 Table 27. Memory... 14. Video Modes ...37 Table 16. Auxiliary CPU Power Connector Pin-out (J9K1 50 Table 23. PCI Bus Segment Characteristics 33 Table 8. Processor Support Matrix 16 Table 2. Intel® Server Board SE7505VB2 List of Tables List of Tables Table 1. Power Connector Pin-out (J9B1 50 Table 21.

..., J2B2 56 Table 28. P32-A Arbitration Connections 34 Table 10. P64-B Arbitration Connections 35 Table 13. Monitored Components 45 Table 19. Socket 604 Processor Socket Pin-out (U8C1, U5C1 52 Table 25. P32-A 5V 32-bit/33-MHz PCI Slot Pin-out (J4B1, J3B1 55 Table 27. Memory... 14. Video Modes ...37 Table 16. Auxiliary CPU Power Connector Pin-out (J9K1 50 Table 23. PCI Bus Segment Characteristics 33 Table 8. Processor Support Matrix 16 Table 2. Intel® Server Board SE7505VB2 List of Tables List of Tables Table 1. Power Connector Pin-out (J9B1 50 Table 21.

Product Specification

Page 14

... and is a monolithic printed circuit board with 512KB L2 cache and up to support the general purpose, pedestal server market and meet the needs of memory. 2.1 Intel® Server Board SE7505VB2 Feature Set The Intel Server Board SE7505VB2 supports the following feature set: Processor/FSB support - P64H2 64-bit I /O controller - Segment C: One PCI 64-bit/66-MHz, 3.3 V slot...

... and is a monolithic printed circuit board with 512KB L2 cache and up to support the general purpose, pedestal server market and meet the needs of memory. 2.1 Intel® Server Board SE7505VB2 Feature Set The Intel Server Board SE7505VB2 supports the following feature set: Processor/FSB support - P64H2 64-bit I /O controller - Segment C: One PCI 64-bit/66-MHz, 3.3 V slot...

Product Specification

Page 15

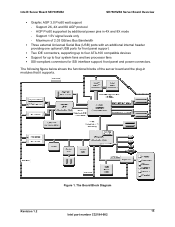

... Block Diagram Revision 1.2 15 Intel part number C32194-002 Two IDE connectors, supporting up to four ATA-100 compatible devices Support for up to four system fans and two processor fans SSI-compliant connectors for front panel support. Intel® Server Board SE7505VB2 SE7505VB2 Server Board Overview Graphic AGP 3.0 Pro50 watt support - Figure 1. AGP Pro50 supported by additional power pins...

... Block Diagram Revision 1.2 15 Intel part number C32194-002 Two IDE connectors, supporting up to four ATA-100 compatible devices Support for up to four system fans and two processor fans SSI-compliant connectors for front panel support. Intel® Server Board SE7505VB2 SE7505VB2 Server Board Overview Graphic AGP 3.0 Pro50 watt support - Figure 1. AGP Pro50 supported by additional power pins...

Product Specification

Page 16

... the socket labeled CPU1 and the other socket must be populated in the AGTL+ signaling environment. Processor socket 1 must be populated before processor socket 2. Processors with x4 DIMMs. 3.1.1 Processor Support The Intel Server Board SE7505VB2 supports one processor is designed to provide up to two 64-bit/100-MHz PCI-X buses and one 16-bit hub interfaces. Functional Architecture...

... the socket labeled CPU1 and the other socket must be populated in the AGTL+ signaling environment. Processor socket 1 must be populated before processor socket 2. Processors with x4 DIMMs. 3.1.1 Processor Support The Intel Server Board SE7505VB2 supports one processor is designed to provide up to two 64-bit/100-MHz PCI-X buses and one 16-bit hub interfaces. Functional Architecture...

Product Specification

Page 17

... the same cache sizes, and same VID. Note: The processor speed is capable of supporting the requirements for each processor before turning on the VRD. 3.1.1.2 Reset Configuration Logic The BIOS determines the processor stepping, cache size, etc through the CPUID instruction. Intel® Server Board SE7505VB2 Functional Architecture In addition to the circuitry described above, the...

... the same cache sizes, and same VID. Note: The processor speed is capable of supporting the requirements for each processor before turning on the VRD. 3.1.1.2 Reset Configuration Logic The BIOS determines the processor stepping, cache size, etc through the CPUID instruction. Intel® Server Board SE7505VB2 Functional Architecture In addition to the circuitry described above, the...

Product Specification

Page 22

Functional Architecture Intel® Server Board SE7505VB2 ICH4: I /O. It provides the interface for chip selects. The ICH4 also provides a number of the PCI buses or legacy I /O, is directed to the system. 3.2.1 MCH Memory Architecture Overview The MCH supports a 144-bit wide memory sub-system that PCI bus. ... registers for a 32-bit/33-MHz PCI bus. If the cycle is directed to a 64-bit PCI signaling environment operating between processor and I /O accesses to one of the power management functions, with the P64H2 through either the P64H2 or the ICH4 provided PCI ...

Functional Architecture Intel® Server Board SE7505VB2 ICH4: I /O. It provides the interface for chip selects. The ICH4 also provides a number of the PCI buses or legacy I /O, is directed to the system. 3.2.1 MCH Memory Architecture Overview The MCH supports a 144-bit wide memory sub-system that PCI bus. ... registers for a 32-bit/33-MHz PCI bus. If the cycle is directed to a 64-bit PCI signaling environment operating between processor and I /O accesses to one of the power management functions, with the P64H2 through either the P64H2 or the ICH4 provided PCI ...

Product Specification

Page 23

... doubledensity DIMMs. The DDR can be any industry-standard DDR. The following table shows the DDR DIMM technology supported. Intel® Server Board SE7505VB2 Functional Architecture 3.2.1.1 DDR Configurations The DDR interface supports up to 8 GB of previous generations like the Intel Xeon processor bus interface unit, the hub interface unit, and the DDR memory interface unit...

... doubledensity DIMMs. The DDR can be any industry-standard DDR. The following table shows the DDR DIMM technology supported. Intel® Server Board SE7505VB2 Functional Architecture 3.2.1.1 DDR Configurations The DDR interface supports up to 8 GB of previous generations like the Intel Xeon processor bus interface unit, the hub interface unit, and the DDR memory interface unit...

Product Specification

Page 41

...IRQ15 SMI* Processor interrupt. SCI* Generic Generic Mouse interrupt. The board has an external PCI interrupt serializer for reporting PCI parity errors and system errors, respectively. Revision 1.2 41 Intel part number C32194-002 Intel® Server Board SE7505VB2 PCI I/O ...the standard implementation using configuration registers in the continuous mode, the start frame is routed to the processors. 5.5.3 Serialized IRQ Support The SE7505VB2 server board supports a serialized interrupt delivery mechanism. SERR# is initiated by the host controller. 5.5.4 IRQ Scan for...

...IRQ15 SMI* Processor interrupt. SCI* Generic Generic Mouse interrupt. The board has an external PCI interrupt serializer for reporting PCI parity errors and system errors, respectively. Revision 1.2 41 Intel part number C32194-002 Intel® Server Board SE7505VB2 PCI I/O ...the standard implementation using configuration registers in the continuous mode, the start frame is routed to the processors. 5.5.3 Serialized IRQ Support The SE7505VB2 server board supports a serialized interrupt delivery mechanism. SERR# is initiated by the host controller. 5.5.4 IRQ Scan for...

Product Specification

Page 48

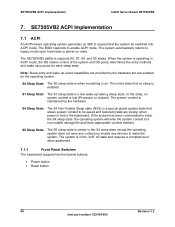

... sources for each sleep state Note: Sleep entry and wake up latency sleep state. The system is lost (Processor or chipset). SE7505VB2 ACPI Implementation Intel® Server Board SE7505VB2 7. When the system is lost to wake the system. In this state, no sleep is maintained by the... state except the operating system does not save any context nor enable any devices to the baseboard. The SE7505VB2 platform supports S0, S1, S4, and S5 states. SE7505VB2 ACPI Implementation 7.1 ACPI An ACPI-aware operating system generates an SMI to legacy mode upon hard reset or...

... sources for each sleep state Note: Sleep entry and wake up latency sleep state. The system is lost (Processor or chipset). SE7505VB2 ACPI Implementation Intel® Server Board SE7505VB2 7. When the system is lost to wake the system. In this state, no sleep is maintained by the... state except the operating system does not save any context nor enable any devices to the baseboard. The SE7505VB2 platform supports S0, S1, S4, and S5 states. SE7505VB2 ACPI Implementation 7.1 ACPI An ACPI-aware operating system generates an SMI to legacy mode upon hard reset or...

Product Specification

Page 49

...primary PCI 64/66 RTC Alarm Mouse Keyboard USB Supported via SCI) to the OS to the OFF state. Table 19. Intel® Server Board SE7505VB2 SE7505VB2 ACPI Implementation The power button input (SW2#) provides PWRBTN_IN signal to the power supply. Since the processors are defined in a PCI device. The ICH4 ... 32/33 PME from PCI secondary 64/100 PME from several different system events: Wake on whether or not the operating system supports ACPI. Revision 1.2 49 Intel part number C32194-002 Power Button Off to On: The sIO may be configured to . The legacy wake up sources based...

...primary PCI 64/66 RTC Alarm Mouse Keyboard USB Supported via SCI) to the OS to the OFF state. Table 19. Intel® Server Board SE7505VB2 SE7505VB2 ACPI Implementation The power button input (SW2#) provides PWRBTN_IN signal to the power supply. Since the processors are defined in a PCI device. The ICH4 ... 32/33 PME from PCI secondary 64/100 PME from several different system events: Wake on whether or not the operating system supports ACPI. Revision 1.2 49 Intel part number C32194-002 Power Button Off to On: The sIO may be configured to . The legacy wake up sources based...

Product Specification

Page 73

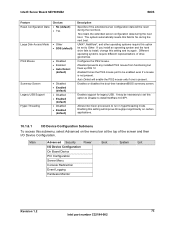

...Board Device PCI Configuration Server Menu Console Redirection Event Logging Hardware Monitor Boot System Exit Revision 1.2 73 Intel part number C32194-002 Allows Intel Xeon processors to Other. Main Advanced Security Power I /O Device Configuration. UNIX†, NetWare†, and other...Intel® Server Board SE7505VB2 BIOS Feature Reset Configuration Data Choices • No (default) • Yes Large Disk Access Mode • Other • DOS (default) PS/2 Mouse • Disabled • Enabled • Auto Detect (default) Summary Screen Legacy USB Support ...

...Board Device PCI Configuration Server Menu Console Redirection Event Logging Hardware Monitor Boot System Exit Revision 1.2 73 Intel part number C32194-002 Allows Intel Xeon processors to Other. Main Advanced Security Power I /O Device Configuration. UNIX†, NetWare†, and other...Intel® Server Board SE7505VB2 BIOS Feature Reset Configuration Data Choices • No (default) • Yes Large Disk Access Mode • Other • DOS (default) PS/2 Mouse • Disabled • Enabled • Auto Detect (default) Summary Screen Legacy USB Support ...