Data Sheet

Page 17

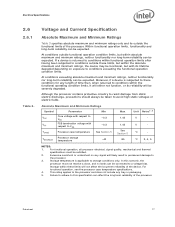

...functional operation condition limits, but with respect to avoid high static voltages or electric fields. Absolute Maximum and Minimum Ratings Symbol Parameter Min VCC Core voltage with respect to VSS -0.3 VTT FSB termination voltage with its reliability will be functional, ...Datasheet 17 This rating applies to the processor. 3. At conditions exceeding absolute maximum and minimum ratings, neither functionality nor long-term reliability can be expected. For functional operation, see the processor case temperature specifications. 4. Within functional operation limits,...

...functional operation condition limits, but with respect to avoid high static voltages or electric fields. Absolute Maximum and Minimum Ratings Symbol Parameter Min VCC Core voltage with respect to VSS -0.3 VTT FSB termination voltage with its reliability will be functional, ...Datasheet 17 This rating applies to the processor. 3. At conditions exceeding absolute maximum and minimum ratings, neither functionality nor long-term reliability can be expected. For functional operation, see the processor case temperature specifications. 4. Within functional operation limits,...

Data Sheet

Page 69

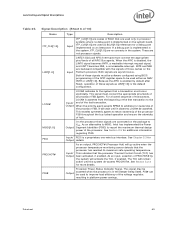

...for ownership of these signals must occur atomically. When the priority agent asserts BPRI# to the system that the processor has reached its maximum safe operating temperature. Input/ PECI is implemented in the system, ITP_CLK[1:0] are used either as BCLK[1:0] references for additional information ...LOCK# is implemented on the Pentium processor. Both of the processor FSB, it observes LOCK# de-asserted. This signal must connect the appropriate pins/lands of these signals are used to VSS. As an alternative to MSID, Intel has implemented the Power Segment Identifier...

...for ownership of these signals must occur atomically. When the priority agent asserts BPRI# to the system that the processor has reached its maximum safe operating temperature. Input/ PECI is implemented in the system, ITP_CLK[1:0] are used either as BCLK[1:0] references for additional information ...LOCK# is implemented on the Pentium processor. Both of the processor FSB, it observes LOCK# de-asserted. This signal must connect the appropriate pins/lands of these signals are used to VSS. As an alternative to MSID, Intel has implemented the Power Segment Identifier...

Data Sheet

Page 72

...the PWRGOOD, VTT or VCC signal will de-assert THERMTRIP#, if the processor's junction temperature remains at or above the maximum TC. It may also be driven low during power on previous generation processors. While the deassertion of PWRGOOD (if VTT or VCC are valid). Input... the target to indicate that it is a JTAG specification support signal used to processor Output core power (VCC). Upon assertion of THERMTRIP#, the processor will automatically shut down when the silicon has reached a temperature approximately 20 °C above the trip level, THERMTRIP# will again be asserted ...

...the PWRGOOD, VTT or VCC signal will de-assert THERMTRIP#, if the processor's junction temperature remains at or above the maximum TC. It may also be driven low during power on previous generation processors. While the deassertion of PWRGOOD (if VTT or VCC are valid). Input... the target to indicate that it is a JTAG specification support signal used to processor Output core power (VCC). Upon assertion of THERMTRIP#, the processor will automatically shut down when the silicon has reached a temperature approximately 20 °C above the trip level, THERMTRIP# will again be asserted ...

Data Sheet

Page 75

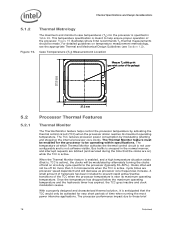

...not alter the fan speed only need to ensure the case temperature meets the thermal profile specifications. Intel has developed a methodology for accurate power measurement that the processor remains within the minimum and maximum case temperature (TC) specifications when operating at or below the onset of... 1.2). If the value reported using PECI is less than or equal to TCONTROL, then the processor case temperature must be designed such that correlates to Intel test temperature and voltage conditions. Typical system level thermal solutions may affect the long-term reliability of the ...

...not alter the fan speed only need to ensure the case temperature meets the thermal profile specifications. Intel has developed a methodology for accurate power measurement that the processor remains within the minimum and maximum case temperature (TC) specifications when operating at or below the onset of... 1.2). If the value reported using PECI is less than or equal to TCONTROL, then the processor case temperature must be designed such that correlates to Intel test temperature and voltage conditions. Typical system level thermal solutions may affect the long-term reliability of the ...

Data Sheet

Page 76

...Design Considerations The case temperature is defined at the geometric top center of the maximum processor power consumption. Processor Thermal Specifications Processor Number Core Frequency (GHz) ...E6300 2.80 65.0 8 E6500 2.93 65.0 8 E6600 3.06 65.0 8 E6700 3.20 65.0 8 E6800 3.33 65.0 8 6 5 4 5 4 5 4 5 6 775_VR_CONFIG 5 6 _06 5 6 (65 W) 5 6 5 6 5 6 5 6 5 See Table 27 and Figure 14 NOTES: 1. Intel recommends that complete thermal solution designs target the Thermal Design Power (TDP) indicated in the unlikely event that the processor...

...Design Considerations The case temperature is defined at the geometric top center of the maximum processor power consumption. Processor Thermal Specifications Processor Number Core Frequency (GHz) ...E6300 2.80 65.0 8 E6500 2.93 65.0 8 E6600 3.06 65.0 8 E6700 3.20 65.0 8 E6800 3.33 65.0 8 6 5 4 5 4 5 4 5 6 775_VR_CONFIG 5 6 _06 5 6 (65 W) 5 6 5 6 5 6 5 6 5 See Table 27 and Figure 14 NOTES: 1. Intel recommends that complete thermal solution designs target the Thermal Design Power (TDP) indicated in the unlikely event that the processor...

Data Sheet

Page 78

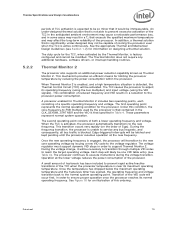

... by activating the thermal control circuit (TCC) when the processor silicon reaches its maximum operating temperature. Bus traffic is specified in the normal manner, and interrupt requests are latched (and serviced during the time that the clocks are processor speed dependent and will decrease as processor core frequencies increase. When the Thermal Monitor feature is enabled...

... by activating the thermal control circuit (TCC) when the processor silicon reaches its maximum operating temperature. Bus traffic is specified in the normal manner, and interrupt requests are latched (and serviced during the time that the clocks are processor speed dependent and will decrease as processor core frequencies increase. When the Thermal Monitor feature is enabled...

Data Sheet

Page 79

...processor reaches its normal operating frequency. During the voltage change, it would be modified. Each step will be one VID table entry (see Section 1.2) for an illustration of this condition, the core-frequency-to-FSB multiple used by issuing a new VID code to the voltage regulator. Once the temperature has dropped below the maximum... The voltage regulator must support dynamic VID steps in a TC that exceeds the specified maximum temperature and may not be capable of cooling the processor even when the TCC is active continuously. In addition, a thermal solution that is ...

...processor reaches its normal operating frequency. During the voltage change, it would be modified. Each step will be one VID table entry (see Section 1.2) for an illustration of this condition, the core-frequency-to-FSB multiple used by issuing a new VID code to the voltage regulator. Once the temperature has dropped below the maximum... The voltage regulator must support dynamic VID steps in a TC that exceeds the specified maximum temperature and may not be capable of cooling the processor even when the TCC is active continuously. In addition, a thermal solution that is ...

Data Sheet

Page 81

...to activate the TCC using PROCHOT# can either signal when the processor (either core) has reached its maximum operating temperature. See the Voltage Regulator Design Guide for the processor to prevent excessive assertion of PROCHOT#. The TCC will automatically ... Considerations 5.2.4 Note: 5.2.5 PROCHOT# Signal An external signal, PROCHOT# (Processor Hot), is asserted when the processor core temperature has reached its maximum operating temperature or be driven from over-temperature situations. PROCHOT# will remain asserted until the system de-asserts PROCHOT#. ...

...to activate the TCC using PROCHOT# can either signal when the processor (either core) has reached its maximum operating temperature. See the Voltage Regulator Design Guide for the processor to prevent excessive assertion of PROCHOT#. The TCC will automatically ... Considerations 5.2.4 Note: 5.2.5 PROCHOT# Signal An external signal, PROCHOT# (Processor Hot), is asserted when the processor core temperature has reached its maximum operating temperature or be driven from over-temperature situations. PROCHOT# will remain asserted until the system de-asserts PROCHOT#. ...

Data Sheet

Page 97

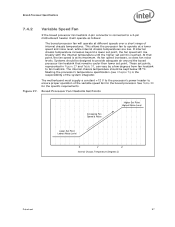

...maximum. Meeting the processor's temperature specification (see Chapter 5) is connected to a 3-pin motherboard header it will operate as follows: The boxed processor fan will rise linearly with the internal temperature until the higher set point. Boxed Processor Specifications 7.4.2 Variable Speed Fan If the boxed processor... short range of the variable speed fan for the specific requirements. The internal chassis temperature should be kept below 38 ºC. See Table 30 for the boxed processor. As fan speed increases, so does fan noise levels. The motherboard must supply a...

...maximum. Meeting the processor's temperature specification (see Chapter 5) is connected to a 3-pin motherboard header it will operate as follows: The boxed processor fan will rise linearly with the internal temperature until the higher set point. Boxed Processor Specifications 7.4.2 Variable Speed Fan If the boxed processor... short range of the variable speed fan for the specific requirements. The internal chassis temperature should be kept below 38 ºC. See Table 30 for the boxed processor. As fan speed increases, so does fan noise levels. The motherboard must supply a...

Data Sheet

Page 98

... through the processor's Digital Thermal Sensors (DTS) and PECI. Fan RPM is connected to an older 3-pin baseboard processor fan header, it will operate as CONTROL. Intel has added an option to the boxed processor that sends out a PWM control signal to fan heatsink. Recommended 1 maximum internal chassis temperature for worst-case operating - Boxed Processor Specifications Table...

... through the processor's Digital Thermal Sensors (DTS) and PECI. Fan RPM is connected to an older 3-pin baseboard processor fan header, it will operate as CONTROL. Intel has added an option to the boxed processor that sends out a PWM control signal to fan heatsink. Recommended 1 maximum internal chassis temperature for worst-case operating - Boxed Processor Specifications Table...