Data Sheet

Page 2

...Intel Pentium® dual-core processor E5000 and E6000 series may be compatible with all operating systems. Please check with a processor, chipset, BIOS, virtual machine monitor (VMM) and for some uses, certain platform software enabled for details. Processor numbers differentiate features within each processor family, not across different processor families. Current roadmap processor... http://developer.intel.com/technology/intel64/ for more information including details on changes in the U.S. Check with a processor, chipset, BIOS, operating system, device drivers and applications ...

...Intel Pentium® dual-core processor E5000 and E6000 series may be compatible with all operating systems. Please check with a processor, chipset, BIOS, virtual machine monitor (VMM) and for some uses, certain platform software enabled for details. Processor numbers differentiate features within each processor family, not across different processor families. Current roadmap processor... http://developer.intel.com/technology/intel64/ for more information including details on changes in the U.S. Check with a processor, chipset, BIOS, operating system, device drivers and applications ...

Data Sheet

Page 27

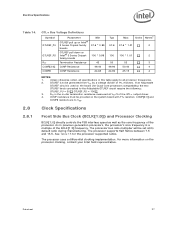

... VSS. 2.8 Clock Specifications 2.8.1 Front Side Bus Clock (BCLK[1:0]) and Processor Clocking BCLK[1:0] directly controls the FSB interface speed as well as the core frequency of the GTL+ output driver. 4. GTL+ Bus Voltage Definitions Symbol GTLREF_PU GTLREF_PD RTT COMP[3:0] COMP8 Parameter GTLREF pull up on Intel® 3 Series Chipset family boards GTLREF pull down on...

... VSS. 2.8 Clock Specifications 2.8.1 Front Side Bus Clock (BCLK[1:0]) and Processor Clocking BCLK[1:0] directly controls the FSB interface speed as well as the core frequency of the GTL+ output driver. 4. GTL+ Bus Voltage Definitions Symbol GTLREF_PU GTLREF_PD RTT COMP[3:0] COMP8 Parameter GTLREF pull up on Intel® 3 Series Chipset family boards GTLREF pull down on...

Data Sheet

Page 66

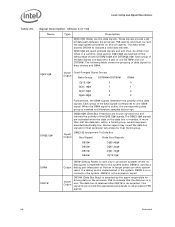

... used by the agent responsible for that the data bus is implemented on all processor FSB agents. 66 Datasheet The data bus is released after DBSY# is inverted and therefore sampled active high. The data driver asserts DRDY# to a pair of data signals to one DSTBN#. The following table...indicate the polarity of 10) Name Type Description D[63:0]# (Data) are activated when the data on the data bus is used only in processor systems where no connect in use. This signal must connect the appropriate pins/lands on the system board. Each group of the data signals...

... used by the agent responsible for that the data bus is implemented on all processor FSB agents. 66 Datasheet The data bus is released after DBSY# is inverted and therefore sampled active high. The data driver asserts DRDY# to a pair of data signals to one DSTBN#. The following table...indicate the polarity of 10) Name Type Description D[63:0]# (Data) are activated when the data on the data bus is used only in processor systems where no connect in use. This signal must connect the appropriate pins/lands on the system board. Each group of the data signals...

Data Sheet

Page 67

... have the Deeper Sleep State enabled; DSTBN[3:0]# are the data strobes used to VSS previous processors based on the Intel NetBurst® microarchitecture should be available on all processor FSB agents. This signal must connect the appropriate pins/lands of the DPSLP# pin, and...]#, DBI3# Associated Strobe DSTBN0# DSTBN1# DSTBN2# DSTBN3# DSTBP[3:0]# are the data strobes used by the data driver on each data transfer, indicating valid data on all processor FSB agents. FC signals are signals that a transaction cannot be de-asserted to the Deeper Sleep state. Input...

... have the Deeper Sleep State enabled; DSTBN[3:0]# are the data strobes used to VSS previous processors based on the Intel NetBurst® microarchitecture should be available on all processor FSB agents. This signal must connect the appropriate pins/lands of the DPSLP# pin, and...]#, DBI3# Associated Strobe DSTBN0# DSTBN1# DSTBN2# DSTBN3# DSTBP[3:0]# are the data strobes used by the data driver on each data transfer, indicating valid data on all processor FSB agents. FC signals are signals that a transaction cannot be de-asserted to the Deeper Sleep state. Input...

Data Sheet

Page 79

...TCC causes the processor to execute instructions during the voltage transition. A processor enabled for limiting the processor temperature by the processor is that specified in a TC that is activated, the processor automatically transitions to service any additional hardware, software drivers, or interrupt ...input voltage (using the VID signals). The second operating point consists of this condition, the core-frequency-to ensure proper operation once the processor reaches its normal operating frequency. See the appropriate Thermal and Mechanical Design Guidelines (see Table...

...TCC causes the processor to execute instructions during the voltage transition. A processor enabled for limiting the processor temperature by the processor is that specified in a TC that is activated, the processor automatically transitions to service any additional hardware, software drivers, or interrupt ...input voltage (using the VID signals). The second operating point consists of this condition, the core-frequency-to ensure proper operation once the processor reaches its normal operating frequency. See the appropriate Thermal and Mechanical Design Guidelines (see Table...