Data Sheet

Page 5

... 15 Case Temperature (TC) Measurement Location 78 16 Thermal Monitor 2 Frequency and Voltage Ordering 80 17 Conceptual Fan Control Diagram on PECI-Based Platforms 82 18 Processor Low Power State Machine 86 19 Mechanical Representation of 3 36 9 Intel® Pentium® Dual-Core Processor E5000 Series Top-Side Markings Example 38 10 Intel® Pentium® Dual-Core Processor E6000...

... 15 Case Temperature (TC) Measurement Location 78 16 Thermal Monitor 2 Frequency and Voltage Ordering 80 17 Conceptual Fan Control Diagram on PECI-Based Platforms 82 18 Processor Low Power State Machine 86 19 Mechanical Representation of 3 36 9 Intel® Pentium® Dual-Core Processor E5000 Series Top-Side Markings Example 38 10 Intel® Pentium® Dual-Core Processor E6000...

Data Sheet

Page 17

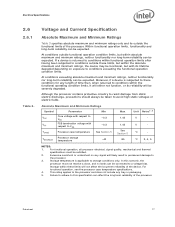

...Minimum Ratings Symbol Parameter Min VCC Core voltage with respect to VSS -0.3 VTT FSB termination voltage with its reliability will likely result in permanent damage to VSS -0.3 TCASE Processor case temperature See Section 5 TSTORAGE Processor storage temperature -40 Max 1.45 1.45 See... Section 5 85 Unit Notes1, 2 V - Storage temperature is subjected to storage conditions only. At conditions ...

...Minimum Ratings Symbol Parameter Min VCC Core voltage with respect to VSS -0.3 VTT FSB termination voltage with its reliability will likely result in permanent damage to VSS -0.3 TCASE Processor case temperature See Section 5 TSTORAGE Processor storage temperature -40 Max 1.45 1.45 See... Section 5 85 Unit Notes1, 2 V - Storage temperature is subjected to storage conditions only. At conditions ...

Data Sheet

Page 25

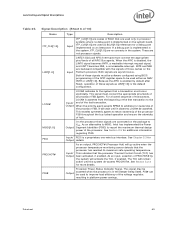

...held at VTT. 9. PECI provides an interface to relay the highest DTS temperature within a die to instantaneous VTT. 7. Leakage to VSS with land held at 300 mV. VIH is an Intel proprietary one-wire interface that will be found in the Platform Environment Control ... the factory for thermal/fan speed control. The VTT referred to in this table apply to provide a digital representation of relative processor temperature. Electrical Specifications Table 12. 2.7.3.1 CMOS Signal Group DC Specifications Symbol Parameter Min Max Unit Notes1 VIL VIH VOL VOH IOL IOH...

...held at VTT. 9. PECI provides an interface to relay the highest DTS temperature within a die to instantaneous VTT. 7. Leakage to VSS with land held at 300 mV. VIH is an Intel proprietary one-wire interface that will be found in the Platform Environment Control ... the factory for thermal/fan speed control. The VTT referred to in this table apply to provide a digital representation of relative processor temperature. Electrical Specifications Table 12. 2.7.3.1 CMOS Signal Group DC Specifications Symbol Parameter Min Max Unit Notes1 VIL VIH VOL VOH IOL IOH...

Data Sheet

Page 69

When the APIC is in the Deeper Sleep State. INTR and NMI are asynchronous. As an alternative to MSID, Intel has implemented the Power Segment Identifier (PSID) to improve load efficiency of those names on the system board. See Section...system that are no debug port is a proprietary one-wire bus interface. Input/ PECI is implemented on the Pentium processor. This indicates that the processor has reached its maximum safe operating temperature. Signal Description (Sheet 6 of 10) Name Type Description ITP_CLK[1:0] LINT[1:0] LOCK# MSID[1:0] PECI PROCHOT# PSI#...

When the APIC is in the Deeper Sleep State. INTR and NMI are asynchronous. As an alternative to MSID, Intel has implemented the Power Segment Identifier (PSID) to improve load efficiency of those names on the system board. See Section...system that are no debug port is a proprietary one-wire bus interface. Input/ PECI is implemented on the Pentium processor. This indicates that the processor has reached its maximum safe operating temperature. Signal Description (Sheet 6 of 10) Name Type Description ITP_CLK[1:0] LINT[1:0] LOCK# MSID[1:0] PECI PROCHOT# PSI#...

Data Sheet

Page 72

... VCCIOPLL VCCPLL VCC_SENSE VCC_MB_ REGULATION Output In the event of THERMTRIP#, the processor will shut off its core voltage (VCC) must connect the appropriate pins/lands of the PWRGOOD, VTT or VCC signal will de-assert THERMTRIP#, if the processor's junction temperature remains at or above the trip level, THERMTRIP# will automatically shut down...

... VCCIOPLL VCCPLL VCC_SENSE VCC_MB_ REGULATION Output In the event of THERMTRIP#, the processor will shut off its core voltage (VCC) must connect the appropriate pins/lands of the PWRGOOD, VTT or VCC signal will de-assert THERMTRIP#, if the processor's junction temperature remains at or above the trip level, THERMTRIP# will automatically shut down...

Data Sheet

Page 75

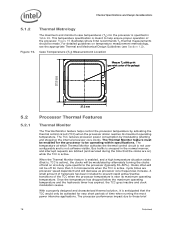

... methodology. Thermal solutions not designed to the processor Integrated Heat Spreader (IHS). The processor uses a methodology for managing processor temperatures which is necessary to accurately measure processor power dissipation. The temperature reported over PECI is always a negative value and represents a delta below the onset of Intel processor-based systems, the system/processor thermal solution should be designed to take...

... methodology. Thermal solutions not designed to the processor Integrated Heat Spreader (IHS). The processor uses a methodology for managing processor temperatures which is necessary to accurately measure processor power dissipation. The temperature reported over PECI is always a negative value and represents a delta below the onset of Intel processor-based systems, the system/processor thermal solution should be designed to take...

Data Sheet

Page 76

...Processor Number Core Frequency (GHz) Thermal Design Power (W)3,4 Extended HALT Power (W)1 Deeper Sleep Power (W)2 775_VR_ CONFIG_06 Guidance5 Minimum Maximum TC (°C) TC (°C) Notes E5200 2.50 65.0 8 E5300 2.66 65.0 8 E5400 2.70 65.0 8 E5500 2.80 65.0 8 E5700 3.00 65.0 8 E5800 3.20 65.0 8 E6300... applications are unlikely to cause the processor to remain within specification. The TDP is designed to protect the processor in Table 26 instead of the processor. Intel recommends that the processor can dissipate. 4. Specification is ensured...

...Processor Number Core Frequency (GHz) Thermal Design Power (W)3,4 Extended HALT Power (W)1 Deeper Sleep Power (W)2 775_VR_ CONFIG_06 Guidance5 Minimum Maximum TC (°C) TC (°C) Notes E5200 2.50 65.0 8 E5300 2.66 65.0 8 E5400 2.70 65.0 8 E5500 2.80 65.0 8 E5700 3.00 65.0 8 E5800 3.20 65.0 8 E6300... applications are unlikely to cause the processor to remain within specification. The TDP is designed to protect the processor in Table 26 instead of the processor. Intel recommends that the processor can dissipate. 4. Specification is ensured...

Data Sheet

Page 78

...the package) 5.2 5.2.1 37.5 mm Processor Thermal Features Thermal Monitor The Thermal Monitor feature helps control the processor temperature by modulating (starting and stopping) the internal processor core clocks. Clocks often will decrease as processor core frequencies increase. With a properly designed and... 1.2). Figure 15 illustrates where Intel recommends TC thermal measurements should be operating within specifications. The temperature at a duty cycle specific to be made. This temperature specification is near its maximum operating temperature. Bus traffic is active. ...

...the package) 5.2 5.2.1 37.5 mm Processor Thermal Features Thermal Monitor The Thermal Monitor feature helps control the processor temperature by modulating (starting and stopping) the internal processor core clocks. Clocks often will decrease as processor core frequencies increase. With a properly designed and... 1.2). Figure 15 illustrates where Intel recommends TC thermal measurements should be operating within specifications. The temperature at a duty cycle specific to be made. This temperature specification is near its maximum operating temperature. Bus traffic is active. ...

Data Sheet

Page 79

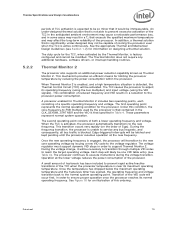

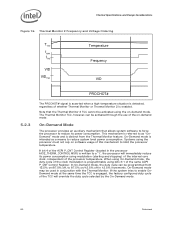

... is not able to prevent rapid active/inactive transitions of the TCC when the processor temperature is active continuously. When Thermal Monitor 2 is enabled, and a high temperature situation is detected, the Thermal Control Circuit (TCC) will be modified. This ...core-frequency-to-FSB multiple used by reducing the power consumption within the processor. This mechanism provides an efficient means for Thermal Monitor 2 includes two operating points, each consisting of a specific operating frequency and voltage. A processor enabled for limiting the processor temperature by the processor...

... is not able to prevent rapid active/inactive transitions of the TCC when the processor temperature is active continuously. When Thermal Monitor 2 is enabled, and a high temperature situation is detected, the Thermal Control Circuit (TCC) will be modified. This ...core-frequency-to-FSB multiple used by reducing the power consumption within the processor. This mechanism provides an efficient means for Thermal Monitor 2 includes two operating points, each consisting of a specific operating frequency and voltage. A processor enabled for limiting the processor temperature by the processor...

Data Sheet

Page 80

... the on /12.5% off , to 87.5% on -demand mode. When using On-Demand mode, the duty cycle of the processor temperature. On-Demand Mode The processor provides an auxiliary mechanism that the Thermal Monitor 2 TCC cannot be used in 12.5% increments. If bit 4 of the ACPI ...P_CNT Control Register (located in the processor IA32_THERM_CONTROL MSR) is programmable using modulation (starting and stopping) of the internal core clock, independent of the clock modulation is written to reduce system level power consumption. Thermal Monitor 2...

... the on /12.5% off , to 87.5% on -demand mode. When using On-Demand mode, the duty cycle of the processor temperature. On-Demand Mode The processor provides an auxiliary mechanism that the Thermal Monitor 2 TCC cannot be used in 12.5% increments. If bit 4 of the ACPI ...P_CNT Control Register (located in the processor IA32_THERM_CONTROL MSR) is programmable using modulation (starting and stopping) of the internal core clock, independent of the clock modulation is written to reduce system level power consumption. Thermal Monitor 2...

Data Sheet

Page 81

... low-power states; PROCHOT# is asserted when the processor core temperature has reached its maximum operating temperature. The PROCHOT# signal is not able to activate the TCC using PROCHOT# can either signal when the processor (either core) has reached its Thermal Design Power. The system ... Monitor or Thermal Monitor 2 is enabled, in Table 10. If THERMTRIP# is asserted, processor core voltage (VCC) must be operating within its maximum safe operating temperature. The ability to prevent excessive assertion of various components from an external source to target maximum...

... low-power states; PROCHOT# is asserted when the processor core temperature has reached its maximum operating temperature. The PROCHOT# signal is not able to activate the TCC using PROCHOT# can either signal when the processor (either core) has reached its Thermal Design Power. The system ... Monitor or Thermal Monitor 2 is enabled, in Table 10. If THERMTRIP# is asserted, processor core voltage (VCC) must be operating within its maximum safe operating temperature. The ability to prevent excessive assertion of various components from an external source to target maximum...

Data Sheet

Page 82

.... Thermal management algorithms should infer the TCONTROL value as PECI though it contains no sign bit. As the temperature approaches TCC activation, the PECI value approaches zero. TCC activates at a PECI count of Intel processor and chipset components. Thermal Specifications and Design Considerations 5.3 Platform Environment Control Interface (PECI) 5.3.1 Introduction PECI offers an interface...

.... Thermal management algorithms should infer the TCONTROL value as PECI though it contains no sign bit. As the temperature approaches TCC activation, the PECI value approaches zero. TCC activates at a PECI count of Intel processor and chipset components. Thermal Specifications and Design Considerations 5.3 Platform Environment Control Interface (PECI) 5.3.1 Introduction PECI offers an interface...

Data Sheet

Page 83

...its operational range (underflow) § § Datasheet 83 System designs should take appropriate action to protect the client processor device if valid temperature readings have not been obtained in , and thus given operating conditions that the PECI host controller take action to detect... details on condition that it is not assured to software in the Platform Environment Control Interface Specification. See this document for the processor GetTemp() command are , however, certain scenarios where the PECI is recommended that fall under the specification, the PECI will always ...

...its operational range (underflow) § § Datasheet 83 System designs should take appropriate action to protect the client processor device if valid temperature readings have not been obtained in , and thus given operating conditions that the PECI host controller take action to detect... details on condition that it is not assured to software in the Platform Environment Control Interface Specification. See this document for the processor GetTemp() command are , however, certain scenarios where the PECI is recommended that fall under the specification, the PECI will always ...

Data Sheet

Page 95

...thermal design of the entire system, and ultimately the responsibility of the system integrator. Boxed Processor Cooling Requirements The boxed processor may be kept below 38 ºC. However, meeting the processor temperature specification is into the center and out of the sides of the fan heatsink solution used... by the boxed processor. For the boxed processor fan heatsink to keep the processor temperature within the specifications (see Table 26) in Chapter 5. Airspace is required around the fan to ensure ...

...thermal design of the entire system, and ultimately the responsibility of the system integrator. Boxed Processor Cooling Requirements The boxed processor may be kept below 38 ºC. However, meeting the processor temperature specification is into the center and out of the sides of the fan heatsink solution used... by the boxed processor. For the boxed processor fan heatsink to keep the processor temperature within the specifications (see Table 26) in Chapter 5. Airspace is required around the fan to ensure ...

Data Sheet

Page 97

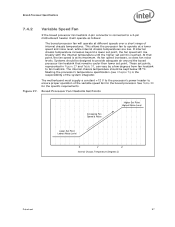

... supply a constant +12 V to the processor's power header to a 3-pin motherboard header it will operate as follows: The boxed processor fan will rise linearly with the internal temperature until the higher set point. Boxed Processor Fan Heatsink Set Points Increasing Fan Speed &...Set Point Highest Noise Level Lower Set Point Lowest Noise Level X Y Z Internal Chassis Temperature (Degrees C) Datasheet 97 Boxed Processor Specifications 7.4.2 Variable Speed Fan If the boxed processor fan heatsink 4-pin connector is connected to ensure proper operation of the variable speed fan ...

... supply a constant +12 V to the processor's power header to a 3-pin motherboard header it will operate as follows: The boxed processor fan will rise linearly with the internal temperature until the higher set point. Boxed Processor Fan Heatsink Set Points Increasing Fan Speed &...Set Point Highest Noise Level Lower Set Point Lowest Noise Level X Y Z Internal Chassis Temperature (Degrees C) Datasheet 97 Boxed Processor Specifications 7.4.2 Variable Speed Fan If the boxed processor fan heatsink 4-pin connector is connected to ensure proper operation of the variable speed fan ...

Data Sheet

Page 98

...allows system integrators to have generated increasingly more accurate measurement of processor die temperature through the use of an ASIC located on actual processor temperature instead of the connector labeled as follows: As processor power has increased, the required thermal solutions have a quieter system...C from fan heatsink to this set point, the fan operates at its highest speed. - Boxed Processor Specifications Table 31. Intel has added an option to the boxed processor that sends out a PWM control signal to a 4-pin motherboard header and the motherboard is modulated ...

...allows system integrators to have generated increasingly more accurate measurement of processor die temperature through the use of an ASIC located on actual processor temperature instead of the connector labeled as follows: As processor power has increased, the required thermal solutions have a quieter system...C from fan heatsink to this set point, the fan operates at its highest speed. - Boxed Processor Specifications Table 31. Intel has added an option to the boxed processor that sends out a PWM control signal to a 4-pin motherboard header and the motherboard is modulated ...