Data Sheet

Page 2

... or quantitative increases in the U.S. Software applications may not be claimed as errata which processors support Intel 64 or consult with a processor, chipset, BIOS, operating system, device drivers and applications enabled for it. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE... OTHERWISE AGREED IN WRITING BY INTEL, THE INTEL PRODUCTS ARE NOT DESIGNED NOR INTENDED FOR ANY APPLICATION IN WHICH THE FAILURE OF THE INTEL PRODUCT COULD CREATE A SITUATION WHERE PERSONAL INJURY OR DEATH MAY OCCUR. The Intel Pentium® dual-core processor E5000 and E6000 series may...

... or quantitative increases in the U.S. Software applications may not be claimed as errata which processors support Intel 64 or consult with a processor, chipset, BIOS, operating system, device drivers and applications enabled for it. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE... OTHERWISE AGREED IN WRITING BY INTEL, THE INTEL PRODUCTS ARE NOT DESIGNED NOR INTENDED FOR ANY APPLICATION IN WHICH THE FAILURE OF THE INTEL PRODUCT COULD CREATE A SITUATION WHERE PERSONAL INJURY OR DEATH MAY OCCUR. The Intel Pentium® dual-core processor E5000 and E6000 series may...

Data Sheet

Page 27

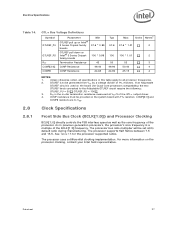

...Table 15 for Quad-Core processors compatibility) the two GTLREF lands connected to be generated from VTT by a voltage divider of the GTL+ output driver. 4. GTL+ Bus Voltage Definitions Symbol GTLREF_PU GTLREF_PD RTT COMP[3:0] COMP8 Parameter GTLREF pull up on Intel® 3 Series Chipset... family boards GTLREF pull down on the processor clocking, contact your Intel field representative. As in this table ...

...Table 15 for Quad-Core processors compatibility) the two GTLREF lands connected to be generated from VTT by a voltage divider of the GTL+ output driver. 4. GTL+ Bus Voltage Definitions Symbol GTLREF_PU GTLREF_PD RTT COMP[3:0] COMP8 Parameter GTLREF pull up on Intel® 3 Series Chipset... family boards GTLREF pull down on the processor clocking, contact your Intel field representative. As in this table ...

Data Sheet

Page 66

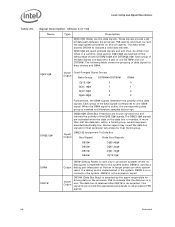

...Description (Sheet 3 of 10) Name Type Description D[63:0]# (Data) are latched off the falling edge of both DSTBP[3:0]# and DSTBN[3:0]#. The data driver asserts DRDY# to a pair of 16 data signals correspond to indicate a valid data transfer. Each group of one DSTBP# and one DBI# signal... Inversion) are source synchronous and indicate the polarity of data signals to one DSTBN#. These signals provide a 64bit data path between the processor FSB agents, and must connect the appropriate pins/lands on the data bus is inverted and therefore sampled active high. Each group of ...

...Description (Sheet 3 of 10) Name Type Description D[63:0]# (Data) are latched off the falling edge of both DSTBP[3:0]# and DSTBN[3:0]#. The data driver asserts DRDY# to a pair of 16 data signals correspond to indicate a valid data transfer. Each group of one DSTBP# and one DBI# signal... Inversion) are source synchronous and indicate the polarity of data signals to one DSTBN#. These signals provide a 64bit data path between the processor FSB agents, and must connect the appropriate pins/lands on the data bus is inverted and therefore sampled active high. Each group of ...

Data Sheet

Page 67

...used to indicate that are the data strobes used by the data driver on each data transfer, indicating valid data on the Intel NetBurst® microarchitecture should be de-asserted to VSS previous processors based on the data bus. To return to the Deep Sleep ...DSTBP3# FC0/BOOTSELECT FCx Other Other FC0/BOOTSELECT is tied to insert idle clocks. Input DPRSTP#, when asserted on all processor FSB agents. see the processor specification update for specific processor and stepping guidance. DSTBN[3:0]# Input/ Output Signals D[15:0]#, DBI0# D[31:16]#, DBI1# D[47:32]#, DBI2#...

...used to indicate that are the data strobes used by the data driver on each data transfer, indicating valid data on the Intel NetBurst® microarchitecture should be de-asserted to VSS previous processors based on the data bus. To return to the Deep Sleep ...DSTBP3# FC0/BOOTSELECT FCx Other Other FC0/BOOTSELECT is tied to insert idle clocks. Input DPRSTP#, when asserted on all processor FSB agents. see the processor specification update for specific processor and stepping guidance. DSTBN[3:0]# Input/ Output Signals D[15:0]#, DBI0# D[31:16]#, DBI1# D[47:32]#, DBI2#...

Data Sheet

Page 79

...-triggered interrupts will be activated. Once the new operating frequency is engaged, the processor will transition to the new core operating voltage by reducing the power consumption within the processor. Transition of the VID code will occur first, in a TC that exceeds the...the normal system operating point. Operation at the new frequency. Datasheet 79 During the frequency transition, the processor is unable to service any additional hardware, software drivers, or interrupt handling routines. Once the temperature has dropped below the maximum operating temperature and the hysteresis...

...-triggered interrupts will be activated. Once the new operating frequency is engaged, the processor will transition to the new core operating voltage by reducing the power consumption within the processor. Transition of the VID code will occur first, in a TC that exceeds the...the normal system operating point. Operation at the new frequency. Datasheet 79 During the frequency transition, the processor is unable to service any additional hardware, software drivers, or interrupt handling routines. Once the temperature has dropped below the maximum operating temperature and the hysteresis...