User Manual

Page 194

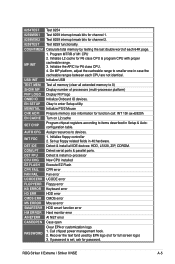

... values into the run time area in CMOS circuitry. Initial interrupts vector table. Measure CPU speed. 5. Put information on screen display, including BIOS logo, CPU type, CPU speed . A.4 Debug code table Code CPU INIT DET CPU CHIPINIT DET DRAM DC FCODE EFSHADOW INIT IO INIT HWM CLR SCRN INIT8042 ENABLEKB DIS MS R/W FSEG DET FLASH TESTCMOS PRG CHIP...

... values into the run time area in CMOS circuitry. Initial interrupts vector table. Measure CPU speed. 5. Put information on screen display, including BIOS logo, CPU type, CPU speed . A.4 Debug code table Code CPU INIT DET CPU CHIPINIT DET DRAM DC FCODE EFSHADOW INIT IO INIT HWM CLR SCRN INIT8042 ENABLEKB DIS MS R/W FSEG DET FLASH TESTCMOS PRG CHIP...

User Manual

Page 195

... MEM SHOW MP PNP LOGO ONBD IO EN SETUP MSINSTAL CHK ACPI EN CACHE SET CHIP AUTO CFG INIT FDC DET IDE COM/LPT DET FPU CPU CHG EZ FLASH CPR FAIL FAN FAIL UCODEERR FLOPYERR KB ERROR HD ERR CMOS ERR MS ERROR SMARTERR HM ERROR AINETERR ...CASEOPEN PASSWORD Test 8254 Test 8259 interrupt mask bits for P6 class CPU & program CPU with proper cacheable range. 3. Initialize the APIC for channel 2. Initialize floppy controller 2. ROG Striker II Extreme / Striker II NSE A-5 Initialize USB Test all memory (clear all IDE devices: HDD, LS120, ZIP, CDROM. Okay to ...

... MEM SHOW MP PNP LOGO ONBD IO EN SETUP MSINSTAL CHK ACPI EN CACHE SET CHIP AUTO CFG INIT FDC DET IDE COM/LPT DET FPU CPU CHG EZ FLASH CPR FAIL FAN FAIL UCODEERR FLOPYERR KB ERROR HD ERR CMOS ERR MS ERROR SMARTERR HM ERROR AINETERR ...CASEOPEN PASSWORD Test 8254 Test 8259 interrupt mask bits for P6 class CPU & program CPU with proper cacheable range. 3. Initialize the APIC for channel 2. Initialize floppy controller 2. ROG Striker II Extreme / Striker II NSE A-5 Initialize USB Test all memory (clear all IDE devices: HDD, LS120, ZIP, CDROM. Okay to ...

User Manual

Page 196

...ROMs. 1. NET PC: Build SYSID structure 3. Initialize APM 8. Clear noise of memory. 5. USB final Initialization 2. Boot attempt (INT 19h) A-6 Appendix: CPU features Build & update ESCD 3. Invoke ISA adapter ROMs 6. Load CMOS time into DOS timer tick 5. Build MSIRQ routing table. Switch screen back to PCI ...devices 7. Program daylight saving 2. USB FINAL INIT ROM NUM LOCK UPDT DMI INT 19H Initialize PnP boot devices 1. Assign IRQs to text mode 4. Set CMOS century to 20h or 19h 4....

...ROMs. 1. NET PC: Build SYSID structure 3. Initialize APM 8. Clear noise of memory. 5. USB final Initialization 2. Boot attempt (INT 19h) A-6 Appendix: CPU features Build & update ESCD 3. Invoke ISA adapter ROMs 6. Load CMOS time into DOS timer tick 5. Build MSIRQ routing table. Switch screen back to PCI ...devices 7. Program daylight saving 2. USB FINAL INIT ROM NUM LOCK UPDT DMI INT 19H Initialize PnP boot devices 1. Assign IRQs to text mode 4. Set CMOS century to 20h or 19h 4....