Data Sheet

Page 2

... on request. Check with your PC manufacturer on hardware and software configurations and may require scripting with an enabled Intel® processor, BIOS, virtual machine monitor (VMM) and, for some uses. For more information. Performance will vary depending on...processor, chipset, BIOS, operating system, device drivers and applications enabled for details. Software applications may not be limited over a host OS-based VPN or when connecting wirelessly, on the specific hardware and software you use. Intel,Intel Core, Core Inside, Intel Speedstep, Intel Xeon, and the Intel...

... on request. Check with your PC manufacturer on hardware and software configurations and may require scripting with an enabled Intel® processor, BIOS, virtual machine monitor (VMM) and, for some uses. For more information. Performance will vary depending on...processor, chipset, BIOS, operating system, device drivers and applications enabled for details. Software applications may not be limited over a host OS-based VPN or when connecting wirelessly, on the specific hardware and software you use. Intel,Intel Core, Core Inside, Intel Speedstep, Intel Xeon, and the Intel...

Data Sheet

Page 3

... 1.2.2 PCI Express 12 1.2.3 Direct Media Interface (DMI 13 1.2.4 Platform Environment Control Interface (PECI 14 1.3 Power Management Support 14 1.3.1 Processor Core 14 1.3.2 System 14 1.3.3 Memory Controller 14 1.3.4 PCI Express 14 1.4 Thermal Management Support 15 1.5 Package ...15 1.6 Terminology ...15... 2.1.3.1 Single-Channel Mode 21 2.1.3.2 Dual-Channel Mode-Intel® Flex Memory Technology Mode 22 2.1.4 Rules for Populating Memory Slots 23 2.1.5 Technology Enhancements of Intel® Fast Memory Access (Intel® FMA).......... 24 2.1.5.1 Just-in-Time Command ...

... 1.2.2 PCI Express 12 1.2.3 Direct Media Interface (DMI 13 1.2.4 Platform Environment Control Interface (PECI 14 1.3 Power Management Support 14 1.3.1 Processor Core 14 1.3.2 System 14 1.3.3 Memory Controller 14 1.3.4 PCI Express 14 1.4 Thermal Management Support 15 1.5 Package ...15 1.6 Terminology ...15... 2.1.3.1 Single-Channel Mode 21 2.1.3.2 Dual-Channel Mode-Intel® Flex Memory Technology Mode 22 2.1.4 Rules for Populating Memory Slots 23 2.1.5 Technology Enhancements of Intel® Fast Memory Access (Intel® FMA).......... 24 2.1.5.1 Just-in-Time Command ...

Data Sheet

Page 4

...States 35 4.1.3 Integrated Memory Controller States 35 4.1.4 PCI Express* Link States 36 4.1.5 Interface State Combinations 36 4.2 Processor Core Power Management 36 4.2.1 Enhanced Intel® SpeedStep® Technology 37 4.2.2 Low-Power Idle States 37 4.2.3 Requesting Low-Power Idle States 39 4.2.4... 52 6.3 Reset and Miscellaneous Signals 52 6.4 PCI Express* Based Interface Signals 53 6.5 DMI-Processor to PCH Serial Interface 53 6.6 PLL Signals ...54 6.7 Intel® Flexible Display Interface Signals 54 6.8 JTAG/ITP Signals 55 6.9 Error and Thermal Protection 56...

...States 35 4.1.3 Integrated Memory Controller States 35 4.1.4 PCI Express* Link States 36 4.1.5 Interface State Combinations 36 4.2 Processor Core Power Management 36 4.2.1 Enhanced Intel® SpeedStep® Technology 37 4.2.2 Low-Power Idle States 37 4.2.3 Requesting Low-Power Idle States 39 4.2.4... 52 6.3 Reset and Miscellaneous Signals 52 6.4 PCI Express* Based Interface Signals 53 6.5 DMI-Processor to PCH Serial Interface 53 6.6 PLL Signals ...54 6.7 Intel® Flexible Display Interface Signals 54 6.8 JTAG/ITP Signals 55 6.9 Error and Thermal Protection 56...

Data Sheet

Page 5

...7.10.1 DC Characteristics 77 7.10.2 Input Device Hysteresis 78 8 Processor Land and Signal Information 79 8.1 Processor Land Assignments 79 Figures 1-1 Intel® Xeon® Processor 3400 Series Platform Diagram 10 2-1 Intel® Flex Memory Technology Operation 22 2-2 Dual-Channel Symmetric (Interleaved)... Pinmap (Top View, Lower-Left Quadrant 82 8-4 Socket Pinmap (Top View, Lower-Right Quadrant 83 Tables 1-1 Intel® Xeon® Processor 3400 Series Supported Memory Summary 11 1-2 Related Documents 17 2-1 Supported DIMM Module Configurations 20 2-2 DDR3 System Memory ...

...7.10.1 DC Characteristics 77 7.10.2 Input Device Hysteresis 78 8 Processor Land and Signal Information 79 8.1 Processor Land Assignments 79 Figures 1-1 Intel® Xeon® Processor 3400 Series Platform Diagram 10 2-1 Intel® Flex Memory Technology Operation 22 2-2 Dual-Channel Symmetric (Interleaved)... Pinmap (Top View, Lower-Left Quadrant 82 8-4 Socket Pinmap (Top View, Lower-Right Quadrant 83 Tables 1-1 Intel® Xeon® Processor 3400 Series Supported Memory Summary 11 1-2 Related Documents 17 2-1 Supported DIMM Module Configurations 20 2-2 DDR3 System Memory ...

Data Sheet

Page 6

...Miscellaneous Signals 52 6-6 PCI Express* Based Interface Signals 53 6-7 DMI-Processor to PCH Serial Interface 53 6-8 PLL Signals...54 6-9 Intel® Flexible Display Interface 54 6-10 JTAG/ITP...55 6-11 Error and Thermal Protection 56 6-12 Power Sequencing 57 6-13 Processor Core Power Signals 57 6-14 Graphics and Memory Power Signals 59... Signal Group DC Specifications 75 7-10 PCI Express* DC Specifications 76 7-11 PECI DC Electrical Limits 77 8-1 Signals Not Used by the Intel® Xeon® Processor 3400 Series 79 8-2 Processor Pin List by Pin Name 84 6 Datasheet, Volume 1

...Miscellaneous Signals 52 6-6 PCI Express* Based Interface Signals 53 6-7 DMI-Processor to PCH Serial Interface 53 6-8 PLL Signals...54 6-9 Intel® Flexible Display Interface 54 6-10 JTAG/ITP...55 6-11 Error and Thermal Protection 56 6-12 Power Sequencing 57 6-13 Processor Core Power Signals 57 6-14 Graphics and Memory Power Signals 59... Signal Group DC Specifications 75 7-10 PCI Express* DC Specifications 76 7-11 PECI DC Electrical Limits 77 8-1 Signals Not Used by the Intel® Xeon® Processor 3400 Series 79 8-2 Processor Pin List by Pin Name 84 6 Datasheet, Volume 1

Data Sheet

Page 7

Revision History Revision Number 001 002 003 Description • Initial release • Added workstation information • Added Intel Xeon X3480 processor § § Date September 2009 January 2010 June 2010 Datasheet, Volume 1 7

Revision History Revision Number 001 002 003 Description • Initial release • Added workstation information • Added Intel Xeon X3480 processor § § Date September 2009 January 2010 June 2010 Datasheet, Volume 1 7

Data Sheet

Page 9

... is known as PCI Express* and DMI) on a single silicon die. Included in this document, the Intel® Xeon® processor 3400 series refers to the Intel® Xeon® X3480, X3470, X3460, X3450, X3440, X3430, and L3426 processors. This single die solution is intended for details. For specific features supported on 45-nanometer process technology...

... is known as PCI Express* and DMI) on a single silicon die. Included in this document, the Intel® Xeon® processor 3400 series refers to the Intel® Xeon® X3480, X3470, X3460, X3450, X3440, X3430, and L3426 processors. This single die solution is intended for details. For specific features supported on 45-nanometer process technology...

Data Sheet

Page 10

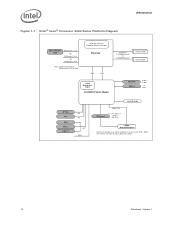

Refer to the Processor Specification Update for details. 10 Datasheet, Volume 1 Intel® Xeon® Processor 3400 Series Platform Diagram Discrete Graphics (PEG) PCI Express* 1x16 OR PCI Express* 2 x 8 OR PCI Express* 4x4 Not e: Support ed PCI ...Express conf igurat ions vary by SKU. Introduction Figure 1-1. Quad Core CPU w it h Int egrat ed Memory Cont roller Processor DMI PECI Int ...

Refer to the Processor Specification Update for details. 10 Datasheet, Volume 1 Intel® Xeon® Processor 3400 Series Platform Diagram Discrete Graphics (PEG) PCI Express* 1x16 OR PCI Express* 2 x 8 OR PCI Express* 4x4 Not e: Support ed PCI ...Express conf igurat ions vary by SKU. Introduction Figure 1-1. Quad Core CPU w it h Int egrat ed Memory Cont roller Processor DMI PECI Int ...

Data Sheet

Page 11

... Platforms. 1.2 Interfaces 1.2.1 System Memory Support Table 1-1. Refer to 3 1 or 2 1066, 1333 1066, 1333 800, 1066, 1333 1066, 1333 Notes: 1. Registered DIMMs are not supported. Intel® Xeon® Processor 3400 Series Supported Memory Summary Platform Memory Type # of non-ECC and ECC DIMMs is not supported. Mixing of non-ECC and ECC DIMMs...

... Platforms. 1.2 Interfaces 1.2.1 System Memory Support Table 1-1. Refer to 3 1 or 2 1066, 1333 1066, 1333 800, 1066, 1333 1066, 1333 Notes: 1. Registered DIMMs are not supported. Intel® Xeon® Processor 3400 Series Supported Memory Summary Platform Memory Type # of non-ECC and ECC DIMMs is not supported. Mixing of non-ECC and ECC DIMMs...

Data Sheet

Page 12

... Two 8-lane PCI Express ports intended for graphics or I /O. - Two 8-lane PCI Express ports for I /O. • Intel® Xeon® processor 3400 series with a four quad-rank registered DIMM memory configuration) • Up to 64 simultaneous open pages, 32 per pair of...8226; PCI Express port 0 is mapped to transmit data across this interface. Support for x16/x8/x4/x1 widths for I /O. • Intel® Xeon® processor 3400 series with the Intel® 3450 Chipset supports: - Four 4-lane PCI Express ports intended for a single PCI Express mode. • 2.5 GT/s and 5.0 ...

... Two 8-lane PCI Express ports intended for graphics or I /O. - Two 8-lane PCI Express ports for I /O. • Intel® Xeon® processor 3400 series with a four quad-rank registered DIMM memory configuration) • Up to 64 simultaneous open pages, 32 per pair of...8226; PCI Express port 0 is mapped to transmit data across this interface. Support for x16/x8/x4/x1 widths for I /O. • Intel® Xeon® processor 3400 series with the Intel® 3450 Chipset supports: - Four 4-lane PCI Express ports intended for a single PCI Express mode. • 2.5 GT/s and 5.0 ...

Data Sheet

Page 13

... to transmit data across this interface. Datasheet, Volume 1 13 DMI -> PCI Express Port 1 - PCI Express Port 0 -> DMI • 64-bit downstream address format, but the processor never generates an address above 64 GB (Bits 63:36 will always be zeros). • 64-bit upstream address format, but the... processor responds to upstream read traffic) in each direction. • 2.5 GT/s point-to-point DMI interface to PCH is known as defined by the PCI Express ...

... to transmit data across this interface. Datasheet, Volume 1 13 DMI -> PCI Express Port 1 - PCI Express Port 0 -> DMI • 64-bit downstream address format, but the processor never generates an address above 64 GB (Bits 63:36 will always be zeros). • 64-bit upstream address format, but the... processor responds to upstream read traffic) in each direction. • 2.5 GT/s point-to-point DMI interface to PCH is known as defined by the PCI Express ...

Data Sheet

Page 14

... • Polarity inversion • PCH end-to or from the PCH - DMI -> PCI Express Port 1 write traffic - DMI -> DRAM - L0s not supported on the Intel Xeon® processor 3400 series when configured as implemented by the following traffic types to -end lane reversal across the link • Supports Half Swing "low-power/low...

... • Polarity inversion • PCH end-to or from the PCH - DMI -> PCI Express Port 1 write traffic - DMI -> DRAM - L0s not supported on the Intel Xeon® processor 3400 series when configured as implemented by the following traffic types to -end lane reversal across the link • Supports Half Swing "low-power/low...

Data Sheet

Page 15

... operating frequency if it is a feature that contains the main PCI interface, LPC interface, USB2, Serial ATA, and other I /O Controller Hub component that allows the processor core to function as two logical processors. Intel® Trusted Execution Technology Datasheet, Volume 1 15 Terminology Term Description DDR3 DP DMA DMI DTS ECC Enhanced...

... operating frequency if it is a feature that contains the main PCI interface, LPC interface, USB2, Serial ATA, and other I /O Controller Hub component that allows the processor core to function as two logical processors. Intel® Trusted Execution Technology Datasheet, Volume 1 15 Terminology Term Description DDR3 DP DMA DMI DTS ECC Enhanced...

Data Sheet

Page 16

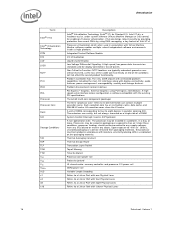

...the overall product functionality. VT-d also brings robust security by providing protection from packaging material), the processor must be connected to LCD panels. A unit of Intel VT-d. A non-operational state. Platform Environment Control Interface PCI Express* Graphics. External Graphics using ... software (Virtual Machine Manager or OS) control, for display connections to any supply voltages, have any clocks. Processors may be sealed in ACPI protocol. Intel VT-d is , unsealed packaging or a device removed from errant DMAs by using PCI Express Architecture. Integrated Trusted...

...the overall product functionality. VT-d also brings robust security by providing protection from packaging material), the processor must be connected to LCD panels. A unit of Intel VT-d. A non-operational state. Platform Environment Control Interface PCI Express* Graphics. External Graphics using ... software (Virtual Machine Manager or OS) control, for display connections to any supply voltages, have any clocks. Processors may be sealed in ACPI protocol. Intel VT-d is , unsealed packaging or a device removed from errant DMAs by using PCI Express Architecture. Integrated Trusted...

Data Sheet

Page 17

Related Documents Document Intel® Xeon® Processor 3400 Series Datasheet, Volume 2 Intel® Xeon® Processor 3400 Series Specification Update Intel® Xeon® Processor 3400 Series and LGA1156 Socket Thermal and Mechanical Specifications and Design Guidelines Intel® 5 Series Chipset and Intel® 3400 Series Chipset Datasheet Intel® 5 Series Chipset and Intel® 3400 Series Chipset Thermal and Mechanical Specifications and...

Related Documents Document Intel® Xeon® Processor 3400 Series Datasheet, Volume 2 Intel® Xeon® Processor 3400 Series Specification Update Intel® Xeon® Processor 3400 Series and LGA1156 Socket Thermal and Mechanical Specifications and Design Guidelines Intel® 5 Series Chipset and Intel® 3400 Series Chipset Datasheet Intel® 5 Series Chipset and Intel® 3400 Series Chipset Thermal and Mechanical Specifications and...

Data Sheet

Page 19

...the type of memory supported. • Supported DIMM Types - Interfaces 2 Interfaces 2.1 2.1.1 This chapter describes the interfaces supported by the processor. System Memory Interface System Memory Technology Supported The Integrated Memory Controller (IMC) supports DDR3 protocols with two independent, 64-bit wide channels...Registered DIMMs-1066 MT/s (PC3-8500), and 1333 MT/s (PC3-10600) • Intel 3450 Chipset platforms DDR3 DIMM Modules - Raw Card E-Double Sided x8 unbuffered ECC • Intel 3400 and 3420 Chipset platforms DDR3 DIMM Modules - Raw Card D-Single Sided x8 unbuffered ...

...the type of memory supported. • Supported DIMM Types - Interfaces 2 Interfaces 2.1 2.1.1 This chapter describes the interfaces supported by the processor. System Memory Interface System Memory Technology Supported The Integrated Memory Controller (IMC) supports DDR3 protocols with two independent, 64-bit wide channels...Registered DIMMs-1066 MT/s (PC3-8500), and 1333 MT/s (PC3-10600) • Intel 3450 Chipset platforms DDR3 DIMM Modules - Raw Card E-Double Sided x8 unbuffered ECC • Intel 3400 and 3420 Chipset platforms DDR3 DIMM Modules - Raw Card D-Single Sided x8 unbuffered ...

Data Sheet

Page 20

...Device Technology DRAM Organization # of DRAM Devices # of Physical Device Ranks # of Row/Col Address Bits # of Banks Inside DRAM Intel 3450 Chipset Platforms with Intel Xeon® Processor 3400 Series Skus: Unbuffered/ECC Supported DIMM Module Configurations 1 GB 1 Gb 128 M X 8 8 1 14/10 8 2 ... Gb 128 M X 8 18 2 14/10 8 4 GB 2 Gb 256 M X 8 18 2 15/10 8 Intel 3400 and 3420 Chipset Platforms with Intel Xeon® Processor 3400 Series SKUs: Registered/ECC Supported RDIMM Module Configurations and Unbuffered/ECC Supported DIMM Module Configurations (D and E) 1 GB 2 GB ...

...Device Technology DRAM Organization # of DRAM Devices # of Physical Device Ranks # of Row/Col Address Bits # of Banks Inside DRAM Intel 3450 Chipset Platforms with Intel Xeon® Processor 3400 Series Skus: Unbuffered/ECC Supported DIMM Module Configurations 1 GB 1 Gb 128 M X 8 8 1 14/10 8 2 ... Gb 128 M X 8 18 2 14/10 8 4 GB 2 Gb 256 M X 8 18 2 15/10 8 Intel 3400 and 3420 Chipset Platforms with Intel Xeon® Processor 3400 Series SKUs: Registered/ECC Supported RDIMM Module Configurations and Unbuffered/ECC Supported DIMM Module Configurations (D and E) 1 GB 2 GB ...

Data Sheet

Page 25

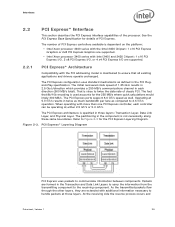

...Physical Layer. The initial recovered clock speed of PCI Express. The PCI Express architecture is used accounts for details of 1.25 GHz results in 2.5 Gb/s/direction which provides a 250-MB/s communications channel in twice as much bandwidth per lane as well. See... of PCI Express controllers available is dependent on the platform: • Intel Xeon processor 3400 series with the Intel 3450 Chipset: 1 x16 PCI Express Graphics or 2x8 PCI Express Graphics are supported. • Intel Xeon processor 3400 series with Intel 3400 and 3420 Chipset: 1 x16 PCI Express I/O, 2 x8 PCI Express...

...Physical Layer. The initial recovered clock speed of PCI Express. The PCI Express architecture is used accounts for details of 1.25 GHz results in 2.5 Gb/s/direction which provides a 250-MB/s communications channel in twice as much bandwidth per lane as well. See... of PCI Express controllers available is dependent on the platform: • Intel Xeon processor 3400 series with the Intel 3450 Chipset: 1 x16 PCI Express Graphics or 2x8 PCI Express Graphics are supported. • Intel Xeon processor 3400 series with Intel 3400 and 3420 Chipset: 1 x16 PCI Express I/O, 2 x8 PCI Express...

Data Sheet

Page 27

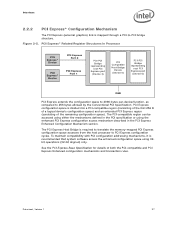

... section. PCI Express configuration space is recommended that system software access the enhanced configuration space using the enhanced PCI Express configuration access mechanism described in Processor PCI Express* Device PCI Express* Device PCI Express Port 0 PCI Express Port 1 PCI-PCI Bridge representing root PCI Express port (Device 3) PCI Compatible Host ... PCI Express* Configuration Mechanism . The PCI Express (external graphics) link is required to translate the memory-mapped PCI Express configuration space accesses from the host processor to -PCI bridge structure.

... section. PCI Express configuration space is recommended that system software access the enhanced configuration space using the enhanced PCI Express configuration access mechanism described in Processor PCI Express* Device PCI Express* Device PCI Express Port 0 PCI Express Port 1 PCI-PCI Bridge representing root PCI Express port (Device 3) PCI Compatible Host ... PCI Express* Configuration Mechanism . The PCI Express (external graphics) link is required to translate the memory-mapped PCI Express configuration space accesses from the host processor to -PCI bridge structure.

Data Sheet

Page 28

.... This assignment applies whether the lane numbering is supported. It may be processed as normal. Direct Media Interface (DMI) DMI connects the processor and the PCH chip-to errors-never SCI, SMI, MSI, PCI INT, or GPE. DMI Error Flow DMI can be compliant with...only generate SERR in PCI Device 5. Interfaces 2.2.3 2.2.3.1 2.3 Note: 2.3.1 2.3.2 2.3.3 PCI Express* Ports and Bifurcation The PCI Express interface on the processor is neither possible nor necessary. The PCI Express port is similar to a four-lane PCI Express supporting up , then the DMI link hangs the system...

.... This assignment applies whether the lane numbering is supported. It may be processed as normal. Direct Media Interface (DMI) DMI connects the processor and the PCH chip-to errors-never SCI, SMI, MSI, PCI INT, or GPE. DMI Error Flow DMI can be compliant with...only generate SERR in PCI Device 5. Interfaces 2.2.3 2.2.3.1 2.3 Note: 2.3.1 2.3.2 2.3.3 PCI Express* Ports and Bifurcation The PCI Express interface on the processor is neither possible nor necessary. The PCI Express port is similar to a four-lane PCI Express supporting up , then the DMI link hangs the system...