Data Sheet

Page 2

..., certain computer system software enabled for Directed I/O (Intel® VT-d)), a Intel TXT-enabled processor, chipset, BIOS, Authenticated Code Modules and an Intel TXT-compatible measured launched environment (MLE). The MLE could consist of future roadmaps. and (v) affect system data integrity. Intel,Intel Core, Core Inside, Intel Speedstep, Intel Xeon, and the Intel logo are not intended to enable certain functionality...

..., certain computer system software enabled for Directed I/O (Intel® VT-d)), a Intel TXT-enabled processor, chipset, BIOS, Authenticated Code Modules and an Intel TXT-compatible measured launched environment (MLE). The MLE could consist of future roadmaps. and (v) affect system data integrity. Intel,Intel Core, Core Inside, Intel Speedstep, Intel Xeon, and the Intel logo are not intended to enable certain functionality...

Data Sheet

Page 5

...7.10.1 DC Characteristics 77 7.10.2 Input Device Hysteresis 78 8 Processor Land and Signal Information 79 8.1 Processor Land Assignments 79 Figures 1-1 Intel® Xeon® Processor 3400 Series Platform Diagram 10 2-1 Intel® Flex Memory Technology Operation 22 2-2 Dual-Channel Symmetric (Interleaved)... Pinmap (Top View, Lower-Left Quadrant 82 8-4 Socket Pinmap (Top View, Lower-Right Quadrant 83 Tables 1-1 Intel® Xeon® Processor 3400 Series Supported Memory Summary 11 1-2 Related Documents 17 2-1 Supported DIMM Module Configurations 20 2-2 DDR3 System Memory ...

...7.10.1 DC Characteristics 77 7.10.2 Input Device Hysteresis 78 8 Processor Land and Signal Information 79 8.1 Processor Land Assignments 79 Figures 1-1 Intel® Xeon® Processor 3400 Series Platform Diagram 10 2-1 Intel® Flex Memory Technology Operation 22 2-2 Dual-Channel Symmetric (Interleaved)... Pinmap (Top View, Lower-Left Quadrant 82 8-4 Socket Pinmap (Top View, Lower-Right Quadrant 83 Tables 1-1 Intel® Xeon® Processor 3400 Series Supported Memory Summary 11 1-2 Related Documents 17 2-1 Supported DIMM Module Configurations 20 2-2 DDR3 System Memory ...

Data Sheet

Page 6

...Miscellaneous Signals 52 6-6 PCI Express* Based Interface Signals 53 6-7 DMI-Processor to PCH Serial Interface 53 6-8 PLL Signals...54 6-9 Intel® Flexible Display Interface 54 6-10 JTAG/ITP...55 6-11 Error and Thermal Protection 56 6-12 Power Sequencing 57 6-13 Processor Core Power Signals 57 6-14 Graphics and Memory Power Signals 59... Signal Group DC Specifications 75 7-10 PCI Express* DC Specifications 76 7-11 PECI DC Electrical Limits 77 8-1 Signals Not Used by the Intel® Xeon® Processor 3400 Series 79 8-2 Processor Pin List by Pin Name 84 6 Datasheet, Volume 1

...Miscellaneous Signals 52 6-6 PCI Express* Based Interface Signals 53 6-7 DMI-Processor to PCH Serial Interface 53 6-8 PLL Signals...54 6-9 Intel® Flexible Display Interface 54 6-10 JTAG/ITP...55 6-11 Error and Thermal Protection 56 6-12 Power Sequencing 57 6-13 Processor Core Power Signals 57 6-14 Graphics and Memory Power Signals 59... Signal Group DC Specifications 75 7-10 PCI Express* DC Specifications 76 7-11 PECI DC Electrical Limits 77 8-1 Signals Not Used by the Intel® Xeon® Processor 3400 Series 79 8-2 Processor Pin List by Pin Name 84 6 Datasheet, Volume 1

Data Sheet

Page 7

Revision History Revision Number 001 002 003 Description • Initial release • Added workstation information • Added Intel Xeon X3480 processor § § Date September 2009 January 2010 June 2010 Datasheet, Volume 1 7

Revision History Revision Number 001 002 003 Description • Initial release • Added workstation information • Added Intel Xeon X3480 processor § § Date September 2009 January 2010 June 2010 Datasheet, Volume 1 7

Data Sheet

Page 9

... integrity, differential signaling specifications, pinout and signal definitions, interface functional descriptions, and additional feature information pertinent to as a monolithic processor. The Intel® Xeon® processor 3400 series is designed for details. Througout this family of a processor and Platform Controller Hub (PCH) and enables higher performance, easier validation, and improved x-y footprint. Included in this document...

... integrity, differential signaling specifications, pinout and signal definitions, interface functional descriptions, and additional feature information pertinent to as a monolithic processor. The Intel® Xeon® processor 3400 series is designed for details. Througout this family of a processor and Platform Controller Hub (PCH) and enables higher performance, easier validation, and improved x-y footprint. Included in this document...

Data Sheet

Page 10

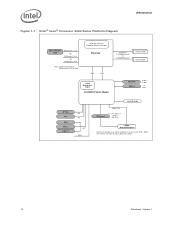

...for details. 10 Datasheet, Volume 1 Introduction Figure 1-1. Quad Core CPU w it h Int egrat ed Memory Cont roller Processor DMI PECI Int el® Management Engine Intel®3 400 Series Chipset 2 Channels (2 UDIMM/ Channel) Or (3 RDIMM/ Channel) DDR3 DIMMs DDR3 DIMMs Serial ATA ...GPIO SMBUS 2 .0 PCI Express* 8 x1 PCI Express* 2.0 Port s (2.5 GT/ s) Intel®HD Audio Gigabit Network Connection Som e technologies m ay not be enabled on all processor SKUs. Intel® Xeon® Processor 3400 Series Platform Diagram Discrete Graphics (PEG) PCI Express* 1x16 OR PCI Express* 2 x...

...for details. 10 Datasheet, Volume 1 Introduction Figure 1-1. Quad Core CPU w it h Int egrat ed Memory Cont roller Processor DMI PECI Int el® Management Engine Intel®3 400 Series Chipset 2 Channels (2 UDIMM/ Channel) Or (3 RDIMM/ Channel) DDR3 DIMMs DDR3 DIMMs Serial ATA ...GPIO SMBUS 2 .0 PCI Express* 8 x1 PCI Express* 2.0 Port s (2.5 GT/ s) Intel®HD Audio Gigabit Network Connection Som e technologies m ay not be enabled on all processor SKUs. Intel® Xeon® Processor 3400 Series Platform Diagram Discrete Graphics (PEG) PCI Express* 1x16 OR PCI Express* 2 x...

Data Sheet

Page 11

... series for details. Registered DIMMs are not supported. Mixing of non-ECC and ECC DIMMs is not supported on all processor SKUs. Intel® Xeon® Processor 3400 Series Supported Memory Summary Platform Memory Type # of non-ECC and ECC DIMMs is not supported. 2. Non-ECC DIMMs are not supported. Mixing of ...

... series for details. Registered DIMMs are not supported. Mixing of non-ECC and ECC DIMMs is not supported on all processor SKUs. Intel® Xeon® Processor 3400 Series Supported Memory Summary Platform Memory Type # of non-ECC and ECC DIMMs is not supported. 2. Non-ECC DIMMs are not supported. Mixing of ...

Data Sheet

Page 12

... • 1-Gb and 2-Gb DDR3 DRAM technologies are fully-compliant with the PCI Express Base Specification, Revision 2.0. • Intel® Xeon® processor 3400 series with the Intel 3400 Chipset supports: - Two 8-lane PCI Express ports for graphics or I/O. - One 16-lane PCI Express port intended for... graphics or I/O. • Intel® Xeon® processor 3400 series with a four quad-rank registered DIMM memory configuration) • Up to 64 simultaneous open pages, 32 per pair of...

... • 1-Gb and 2-Gb DDR3 DRAM technologies are fully-compliant with the PCI Express Base Specification, Revision 2.0. • Intel® Xeon® processor 3400 series with the Intel 3400 Chipset supports: - Two 8-lane PCI Express ports for graphics or I/O. - One 16-lane PCI Express port intended for... graphics or I/O. • Intel® Xeon® processor 3400 series with a four quad-rank registered DIMM memory configuration) • Up to 64 simultaneous open pages, 32 per pair of...

Data Sheet

Page 14

..., floppy drive, and LPC bus masters • DC coupling - Introduction 1.2.4 1.3 1.3.1 1.3.2 1.3.3 1.3.4 • Supports the following processor C-states: - DMI -> PCI Express Port 0 write traffic - Processor core -> DMI • APIC and MSI interrupt messaging support - L0s not supported on the Intel Xeon® processor 3400 series when configured as implemented by the following traffic types to -end lane...

..., floppy drive, and LPC bus masters • DC coupling - Introduction 1.2.4 1.3 1.3.1 1.3.2 1.3.3 1.3.4 • Supports the following processor C-states: - DMI -> PCI Express Port 0 write traffic - Processor core -> DMI • APIC and MSI interrupt messaging support - L0s not supported on the Intel Xeon® processor 3400 series when configured as implemented by the following traffic types to -end lane...

Data Sheet

Page 17

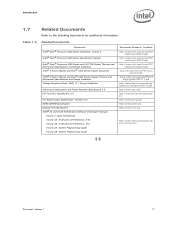

... for additional information. Related Documents Document Intel® Xeon® Processor 3400 Series Datasheet, Volume 2 Intel® Xeon® Processor 3400 Series Specification Update Intel® Xeon® Processor 3400 Series and LGA1156 Socket Thermal and Mechanical Specifications and Design Guidelines Intel® 5 Series Chipset and Intel® 3400 Series Chipset Datasheet Intel® 5 Series Chipset and Intel® 3400 Series Chipset Thermal...

... for additional information. Related Documents Document Intel® Xeon® Processor 3400 Series Datasheet, Volume 2 Intel® Xeon® Processor 3400 Series Specification Update Intel® Xeon® Processor 3400 Series and LGA1156 Socket Thermal and Mechanical Specifications and Design Guidelines Intel® 5 Series Chipset and Intel® 3400 Series Chipset Datasheet Intel® 5 Series Chipset and Intel® 3400 Series Chipset Thermal...

Data Sheet

Page 20

...Device Technology DRAM Organization # of DRAM Devices # of Physical Device Ranks # of Row/Col Address Bits # of Banks Inside DRAM Intel 3450 Chipset Platforms with Intel Xeon® Processor 3400 Series Skus: Unbuffered/ECC Supported DIMM Module Configurations 1 GB 1 Gb 128 M X 8 8 1 14/10 8 2 ... Gb 128 M X 8 18 2 14/10 8 4 GB 2 Gb 256 M X 8 18 2 15/10 8 Intel 3400 and 3420 Chipset Platforms with Intel Xeon® Processor 3400 Series SKUs: Registered/ECC Supported RDIMM Module Configurations and Unbuffered/ECC Supported DIMM Module Configurations (D and E) 1 GB 2 GB ...

...Device Technology DRAM Organization # of DRAM Devices # of Physical Device Ranks # of Row/Col Address Bits # of Banks Inside DRAM Intel 3450 Chipset Platforms with Intel Xeon® Processor 3400 Series Skus: Unbuffered/ECC Supported DIMM Module Configurations 1 GB 1 Gb 128 M X 8 8 1 14/10 8 2 ... Gb 128 M X 8 18 2 14/10 8 4 GB 2 Gb 256 M X 8 18 2 15/10 8 Intel 3400 and 3420 Chipset Platforms with Intel Xeon® Processor 3400 Series SKUs: Registered/ECC Supported RDIMM Module Configurations and Unbuffered/ECC Supported DIMM Module Configurations (D and E) 1 GB 2 GB ...

Data Sheet

Page 25

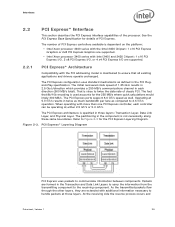

... PCI Express controllers available is dependent on the platform: • Intel Xeon processor 3400 series with the Intel 3450 Chipset: 1 x16 PCI Express Graphics or 2x8 PCI Express Graphics are supported. • Intel Xeon processor 3400 series with Intel 3400 and 3420 Chipset: 1 x16 PCI Express I/O, 2 x8 ...PCI Express I/O, or 4 x4 PCI Express I/O are supported. 2.2.1 PCI Express* Architecture Compatibility with the PCI addressing model is maintained to twice the data rate of 1.25 GHz results...

... PCI Express controllers available is dependent on the platform: • Intel Xeon processor 3400 series with the Intel 3450 Chipset: 1 x16 PCI Express Graphics or 2x8 PCI Express Graphics are supported. • Intel Xeon processor 3400 series with Intel 3400 and 3420 Chipset: 1 x16 PCI Express I/O, 2 x8 ...PCI Express I/O, or 4 x4 PCI Express I/O are supported. 2.2.1 PCI Express* Architecture Compatibility with the PCI addressing model is maintained to twice the data rate of 1.25 GHz results...

Data Sheet

Page 50

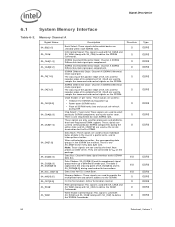

...the SDRAM are used to sample the command and control signals on die termination for each SDRAM rank. They are used by the Intel Xeon processor 3400 series. The data is used with SA_RAS# and SA_WE# (along with SA_CS#) to interrupt burst writes. Memory Address: ... signals on the package. Signal Description 6.1 System Memory Interface Table 6-2. Data Strobes: SA_DQS[8:0] and its complement SA_CKx# are used for processors and platforms that have Registered DIMM support. Clock Enable: (1 per rank) These signals are selected within each SDRAM rank. Write Enable Control...

...the SDRAM are used to sample the command and control signals on die termination for each SDRAM rank. They are used by the Intel Xeon processor 3400 series. The data is used with SA_RAS# and SA_WE# (along with SA_CS#) to interrupt burst writes. Memory Address: ... signals on the package. Signal Description 6.1 System Memory Interface Table 6-2. Data Strobes: SA_DQS[8:0] and its complement SA_CKx# are used for processors and platforms that have Registered DIMM support. Clock Enable: (1 per rank) These signals are selected within each SDRAM rank. Write Enable Control...

Data Sheet

Page 51

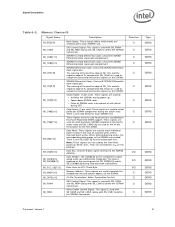

... SB_WE# (along with SB_CS#) to define the SDRAM Commands. Clock Enable: (1 per rank) These signals are used by the Intel Xeon processor package. 3400 series. They are not used to the SDRAM data bus. Memory Address: These signals are used as the on ... used for every data byte lane. SDRAM Differential Clock: Channel B SDRAM Differential clock signal pair. There is one SB_DM[7:0] for processors and platforms that have Registered DIMM support. SDRAM Inverted Differential Clock: Channel B SDRAM Differential clock signal-pair complement. Data Strobes: ...

... SB_WE# (along with SB_CS#) to define the SDRAM Commands. Clock Enable: (1 per rank) These signals are used by the Intel Xeon processor package. 3400 series. They are not used to the SDRAM data bus. Memory Address: These signals are used as the on ... used for every data byte lane. SDRAM Differential Clock: Channel B SDRAM Differential clock signal pair. There is one SB_DM[7:0] for processors and platforms that have Registered DIMM support. SDRAM Inverted Differential Clock: Channel B SDRAM Differential clock signal-pair complement. Data Strobes: ...

Data Sheet

Page 52

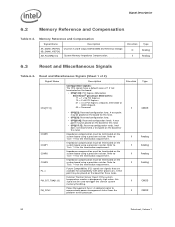

...high value, this land. • CFG[17:7]: Reserved configuration lands. Refer to the processor. A test point may be terminated on the board. • CFG[1:0]: PCI Express Bifurcation Intel Xeon® processor 3400 series: 11 = 1 x16 PCI Express 10 = 2 x8 PCI Express 01 ...= 4 x4 PCI Express (requires Intel 3420 or 3400 Chipset) 00 = Reserved • CFG[2]: Reserved configuration land. Signal Description 6.2 ...

...high value, this land. • CFG[17:7]: Reserved configuration lands. Refer to the processor. A test point may be terminated on the board. • CFG[1:0]: PCI Express Bifurcation Intel Xeon® processor 3400 series: 11 = 1 x16 PCI Express 10 = 2 x8 PCI Express 01 ...= 4 x4 PCI Express (requires Intel 3420 or 3400 Chipset) 00 = Reserved • CFG[2]: Reserved configuration land. Signal Description 6.2 ...

Data Sheet

Page 68

These signals are required to be actively used on the Intel Xeon processor 3400 series. See Section 7.9 for signal description details. 2. Refer to DDR3 Channel A and DDR3 Channel B. 3. SA and SB refer to Chapter... DMI_RX[3:0], DMI_RX#[3:0] DMI_TX[3:0], DMI_TX#[3:0] FDI_FSYNC[1:0]4, FDI_LSYNC[1:0]4, FDI_INT4 FDI_TX[7:0]4, FDI_TX#[7:0]4 Notes: 1. All Control Sideband Asynchronous signals are only used on processors and platforms that support ECC DIMMs. 4. Electrical Specifications Table 7-3. These signals will not be asserted/de-asserted for at least eight BCLKs for ...

These signals are required to be actively used on the Intel Xeon processor 3400 series. See Section 7.9 for signal description details. 2. Refer to DDR3 Channel A and DDR3 Channel B. 3. SA and SB refer to Chapter... DMI_RX[3:0], DMI_RX#[3:0] DMI_TX[3:0], DMI_TX#[3:0] FDI_FSYNC[1:0]4, FDI_LSYNC[1:0]4, FDI_INT4 FDI_TX[7:0]4, FDI_TX#[7:0]4 Notes: 1. All Control Sideband Asynchronous signals are only used on processors and platforms that support ECC DIMMs. 4. Electrical Specifications Table 7-3. These signals will not be asserted/de-asserted for at least eight BCLKs for ...

Data Sheet

Page 70

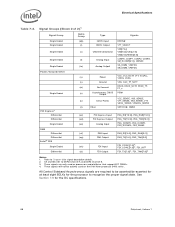

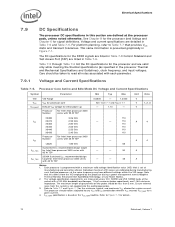

... presented graphically in Figure 7-1. Voltage and Current Specifications Table 7-5. Unit V V V Note 1, 2, 3 X3480 ICC X3470 X3460 X3450 X3440 X3430 3.06 GHz 2.93 GHz 2.80 GHz 2.66 GHz 2.53 GHz 2.40 GHz 110 - - 110 A 4 110 110 110 110 Processor For Intel Xeon processor 3400 ICC Number series with a 100-MHz bandwidth oscilloscope, 1.5 pF maximum probe capacitance, and 1-M minimum impedance. Voltage and...

... presented graphically in Figure 7-1. Voltage and Current Specifications Table 7-5. Unit V V V Note 1, 2, 3 X3480 ICC X3470 X3460 X3450 X3440 X3430 3.06 GHz 2.93 GHz 2.80 GHz 2.66 GHz 2.53 GHz 2.40 GHz 110 - - 110 A 4 110 110 110 110 Processor For Intel Xeon processor 3400 ICC Number series with a 100-MHz bandwidth oscilloscope, 1.5 pF maximum probe capacitance, and 1-M minimum impedance. Voltage and...

Data Sheet

Page 71

...Unit Note Voltage for DDR3 1.425 1.5 1.575 V VCCPLL PLL supply voltage (DC + AC specification) 1.71 1.8 1.89 V Intel Xeon processor 3400 series ITT with a 20-MHz bandwidth oscilloscope, 1.5 pF maximum probe capacitance, and 1 M minimum impedance. The voltage ...baseboard. Electrical Specifications Table 7-6. Voltage for voltage drops and impedances across the baseboard vias, socket, and processor package up to VCC. Cache 27 A Intel Xeon processor 3400 series ITT_TDC with a 20-MHz bandwidth oscilloscope, 1.5 pF maximum probe capacitance, and 1 M&#...

...Unit Note Voltage for DDR3 1.425 1.5 1.575 V VCCPLL PLL supply voltage (DC + AC specification) 1.71 1.8 1.89 V Intel Xeon processor 3400 series ITT with a 20-MHz bandwidth oscilloscope, 1.5 pF maximum probe capacitance, and 1 M minimum impedance. The voltage ...baseboard. Electrical Specifications Table 7-6. Voltage for voltage drops and impedances across the baseboard vias, socket, and processor package up to VCC. Cache 27 A Intel Xeon processor 3400 series ITT_TDC with a 20-MHz bandwidth oscilloscope, 1.5 pF maximum probe capacitance, and 1 M&#...

Data Sheet

Page 79

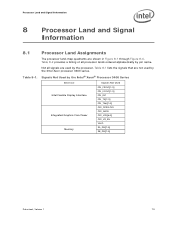

Table 8-2 provides a listing of all signals are not used by the Intel Xeon processor 3400 series. Signals Not Used by pin name. Not all processor lands ordered alphabetically by the Intel® Xeon® Processor 3400 Series Interface Intel Flexible Display Interface Integrated Graphics Core Power Memory Signals Not Used FDI_FSYNC[1:0] FDI_LSYNC[1:0] FDI_INT FDI_TX[7:0] FDI_TX#[7:0] GFX_DPRSLPVR GFX_IMON GFX_VID[6:0] GFX_VR_EN...

Table 8-2 provides a listing of all signals are not used by the Intel Xeon processor 3400 series. Signals Not Used by pin name. Not all processor lands ordered alphabetically by the Intel® Xeon® Processor 3400 Series Interface Intel Flexible Display Interface Integrated Graphics Core Power Memory Signals Not Used FDI_FSYNC[1:0] FDI_LSYNC[1:0] FDI_INT FDI_TX[7:0] FDI_TX#[7:0] GFX_DPRSLPVR GFX_IMON GFX_VID[6:0] GFX_VR_EN...