Data Sheet

Page 9

... Side Bus (FSB) is manufactured on -die, primary 32-kB instruction cache and 32-kB write-back data cache in enterprise environments. Quad-Core Intel® Xeon® Processor 5400 Series features include Intel® Wide Dynamic Execution, enhanced floating point and multi-media units, Streaming...enhancement to the L2 cache before an L1 cache requests occurs, resulting in conjunction with IA-32 software. The QuadCore Intel® Xeon® Processor 5400 Series maintains the tradition of the 64-bit extension technology. Intel® Thermal Monitor 1 and Intel® Thermal...

... Side Bus (FSB) is manufactured on -die, primary 32-kB instruction cache and 32-kB write-back data cache in enterprise environments. Quad-Core Intel® Xeon® Processor 5400 Series features include Intel® Wide Dynamic Execution, enhanced floating point and multi-media units, Streaming...enhancement to the L2 cache before an L1 cache requests occurs, resulting in conjunction with IA-32 software. The QuadCore Intel® Xeon® Processor 5400 Series maintains the tradition of the 64-bit extension technology. Intel® Thermal Monitor 1 and Intel® Thermal...

Data Sheet

Page 10

...on Intel Virtualization Technology can deliver addresses two times per core L2 Advanced Cache 2x6 MB shared Front Side Bus Frequency 1600 MHz 1333 MHz 1066 MHz Package FC-LGA 771 Lands The Quad-Core Intel® Xeon® Processor 5400 Series-based platforms implement independent core voltage ...Low logic level). 10 Conversely, when NMI is inverted. The Quad-Core Intel® Xeon® Processor 5400 Series supports either 1066 MHz, 1333 MHz, or 1600 MHz Front Side Bus operations. It utilizes a surface mount LGA771 socket that the signal is high, a nonmaskable interrupt has ...

...on Intel Virtualization Technology can deliver addresses two times per core L2 Advanced Cache 2x6 MB shared Front Side Bus Frequency 1600 MHz 1333 MHz 1066 MHz Package FC-LGA 771 Lands The Quad-Core Intel® Xeon® Processor 5400 Series-based platforms implement independent core voltage ...Low logic level). 10 Conversely, when NMI is inverted. The Quad-Core Intel® Xeon® Processor 5400 Series supports either 1066 MHz, 1333 MHz, or 1600 MHz Front Side Bus operations. It utilizes a surface mount LGA771 socket that the signal is high, a nonmaskable interrupt has ...

Data Sheet

Page 12

...Intel®64 Architecture - Processor virtualization, which all processor specifications, including DC, AC, FSB, signal quality, mechanical and thermal are known as the processor system bus or the system bus. L2 cache...core with the processor at the pads of the system bus interface. • Front Side Bus (FSB) - Estimate of the 64-bit extension technology. • Enhanced Intel SpeedStep® Technology - Processors may be sealed in a tray...exposure to take advantage of the maximum values the Quad-Core Intel® Xeon® Processor 5400 Series will have any supply ...

...Intel®64 Architecture - Processor virtualization, which all processor specifications, including DC, AC, FSB, signal quality, mechanical and thermal are known as the processor system bus or the system bus. L2 cache...core with the processor at the pads of the system bus interface. • Front Side Bus (FSB) - Estimate of the 64-bit extension technology. • Enhanced Intel SpeedStep® Technology - Processors may be sealed in a tray...exposure to take advantage of the maximum values the Quad-Core Intel® Xeon® Processor 5400 Series will have any supply ...

Specification Update

Page 7

...specification clarifications and documentation changes are removed from the specification update are differentiated by their unique characteristics,e.g., core speed, L2 cache size, package type, etc. These changes will be incorporated in any new release of the specification... changes are modifications to the appropriate product specification or user documentation (datasheets, manuals, and so forth). 7 Intel® Xeon® Processor 5400 Series Specification Update Specification Clarifications describe a specification in the specification update throughout the product's ...

...specification clarifications and documentation changes are removed from the specification update are differentiated by their unique characteristics,e.g., core speed, L2 cache size, package type, etc. These changes will be incorporated in any new release of the specification... changes are modifications to the appropriate product specification or user documentation (datasheets, manuals, and so forth). 7 Intel® Xeon® Processor 5400 Series Specification Update Specification Clarifications describe a specification in the specification update throughout the product's ...

Specification Update

Page 8

... exists in a future stepping of the product. Specification Change or Clarification that are no plans to this erratum is prefixed with 1MB L2 cache K = Mobile Intel® Pentium® III processor Intel® Xeon® Processor 5400 Series 8 Specification Update There are used in listed stepping or specification change or update will be fixed in...

... exists in a future stepping of the product. Specification Change or Clarification that are no plans to this erratum is prefixed with 1MB L2 cache K = Mobile Intel® Pentium® III processor Intel® Xeon® Processor 5400 Series 8 Specification Update There are used in listed stepping or specification change or update will be fixed in...

Specification Update

Page 9

... Intel® Xeon® processor MP with up to 8 MB L3 cache Mobile Intel® Celeron® processor on.13 micron process in Micro-FCPGA package Intel® Celeron® M processor Intel® Pentium® M processor on 90 nm process with 2-MB L2 cache and Intel® processor A100 and A110 with 512-KB L2 cache Intel® Pentium® M processor Mobile Intel...

... Intel® Xeon® processor MP with up to 8 MB L3 cache Mobile Intel® Celeron® processor on.13 micron process in Micro-FCPGA package Intel® Celeron® M processor Intel® Pentium® M processor on 90 nm process with 2-MB L2 cache and Intel® processor A100 and A110 with 512-KB L2 cache Intel® Pentium® M processor Mobile Intel...

Specification Update

Page 16

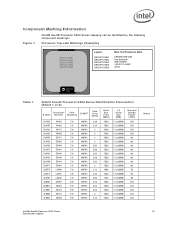

...12M/1333 Intel ® Xeon® SXXX XXXXX i (M) © '07 x54XX (FPO) LAOTTPONO S/N Table 1. Component Marking Information Figure 1. Intel® Xeon® Processor 5400 Series Identification Information (Sheet 1 of 2) S-Spec Processor Number Core Stepping CPUID1 Core... Freq (GHz) SLANZ SLANP SLASA SLASB SLANR SLANQ SLANS SLANT SLANU SLANV SLANW SLAP2 SLAP5 SLAP4 SLARP SLBBD SLBBG SLBBF SLBBB SLBBA X5482 X5460 X5472...1600 1333 L2 Cache Size ...

...12M/1333 Intel ® Xeon® SXXX XXXXX i (M) © '07 x54XX (FPO) LAOTTPONO S/N Table 1. Component Marking Information Figure 1. Intel® Xeon® Processor 5400 Series Identification Information (Sheet 1 of 2) S-Spec Processor Number Core Stepping CPUID1 Core... Freq (GHz) SLANZ SLANP SLASA SLASB SLANR SLANQ SLANS SLANT SLANU SLANV SLANW SLAP2 SLAP5 SLAP4 SLARP SLBBD SLBBG SLBBF SLBBB SLBBA X5482 X5460 X5472...1600 1333 L2 Cache Size ...

Specification Update

Page 17

... Specification Update Processors in the QDF/S-Spec column that begin with a Q are for qualification only. Intel® Xeon® Processor 5400 Series Identification Information (Sheet 2 of 2) Processor Core S-Spec Number Stepping CPUID1 Core Freq (GHz) Data Bus Freq (MHz) L2 Cache Size (MB) Thermal Design Power (TDP) Notes SLBBE X5450 E-0 1067Ah 3 1333 12 (2x6MB) 120 SLBBH...

... Specification Update Processors in the QDF/S-Spec column that begin with a Q are for qualification only. Intel® Xeon® Processor 5400 Series Identification Information (Sheet 2 of 2) Processor Core S-Spec Number Stepping CPUID1 Core Freq (GHz) Data Bus Freq (MHz) L2 Cache Size (MB) Thermal Design Power (TDP) Notes SLBBE X5450 E-0 1067Ah 3 1333 12 (2x6MB) 120 SLBBH...

Specification Update

Page 22

...size of the 'From' address debug information reported through BTMs or BTSs may be incorrect. Workaround: Software should not rely on Single-bit L2 ECC Errors May be incorrect. Address Reported by Machine-Check Architecture (MCA) on the value reported in MCi_ADDR, for this erratum, if ...: None identified. Due to this #GP fault may be Incorrect Problem: When correctable Single-bit ECC errors occur in the L2 cache, the address is generated after all higher priority Interrupts and exceptions are serviced. Intel® Xeon® Processor 5400 Series 22 Specification Update

...size of the 'From' address debug information reported through BTMs or BTSs may be incorrect. Workaround: Software should not rely on Single-bit L2 ECC Errors May be incorrect. Address Reported by Machine-Check Architecture (MCA) on the value reported in MCi_ADDR, for this erratum, if ...: None identified. Due to this #GP fault may be Incorrect Problem: When correctable Single-bit ECC errors occur in the L2 cache, the address is generated after all higher priority Interrupts and exceptions are serviced. Intel® Xeon® Processor 5400 Series 22 Specification Update