Data Sheet

Page 2

... future changes to specifications and product descriptions at any features or instructions marked "reserved" or "undefined." The Quad-Core Intel® Xeon® Processor 5400 Series may cause the product to obtain the latest specifications and before placing your system vendor for Intel® 64 architecture. Intel® Virtualization Technology requires a computer system with a processor, chipset, BIOS, operating system, device drivers and applications enabled...

... future changes to specifications and product descriptions at any features or instructions marked "reserved" or "undefined." The Quad-Core Intel® Xeon® Processor 5400 Series may cause the product to obtain the latest specifications and before placing your system vendor for Intel® 64 architecture. Intel® Virtualization Technology requires a computer system with a processor, chipset, BIOS, operating system, device drivers and applications enabled...

Data Sheet

Page 6

... FSB Differential BCLK Specifications 40 3-1 Package Loading Specifications 47 3-2 Package Handling Guidelines 48 3-3 Processor Materials 48 4-1 Land Listing by Land Name 51 4-2 Land Listing by Land Number 61 5-1 Signal Definitions 71 6-1 Quad-Core Intel® Xeon® Processor X5492 and X5482 (C-step) Thermal Specifications ...81 6-2 Quad-Core Intel® Xeon® Processor X5492 and X5482 (C-step)Thermal Profile Table .82 6-3 Quad-Core Intel® Xeon® Processor X5400 Series Thermal Specifications 83 6-4 Quad-Core Intel® Xeon® Processor...

... FSB Differential BCLK Specifications 40 3-1 Package Loading Specifications 47 3-2 Package Handling Guidelines 48 3-3 Processor Materials 48 4-1 Land Listing by Land Name 51 4-2 Land Listing by Land Number 61 5-1 Signal Definitions 71 6-1 Quad-Core Intel® Xeon® Processor X5492 and X5482 (C-step) Thermal Specifications ...81 6-2 Quad-Core Intel® Xeon® Processor X5492 and X5482 (C-step)Thermal Profile Table .82 6-3 Quad-Core Intel® Xeon® Processor X5400 Series Thermal Specifications 83 6-4 Quad-Core Intel® Xeon® Processor...

Data Sheet

Page 9

... Software Developer's Manual, at http://www.intel.com/cd/ids/developer/asmona/eng/149308.htm. The processor is a quadpumped bus running off a 400 MHz system clock making 12.80 GBytes per second data transfer rates possible. When used in high temperature situations. The Quad-Core Intel® Xeon® Processor 5400 Series support Intel® Virtualization Technology for data movement. Quad-Core Intel® Xeon® Processor 5400 Series features...

... Software Developer's Manual, at http://www.intel.com/cd/ids/developer/asmona/eng/149308.htm. The processor is a quadpumped bus running off a 400 MHz system clock making 12.80 GBytes per second data transfer rates possible. When used in high temperature situations. The Quad-Core Intel® Xeon® Processor 5400 Series support Intel® Virtualization Technology for data movement. Quad-Core Intel® Xeon® Processor 5400 Series features...

Data Sheet

Page 11

...; LGA771 socket - The Quad-Core Intel® Xeon® Processor 5400 Series interfaces to meet Network Equipment Building System (NEBS) level 3 compliance. The term 'processors' and "Quad-Core Intel® Xeon® Processor 5400 Series" are unique to call out specifications that are unique to the Quad-Core Intel® Xeon® Processor X5492 SKU. • Quad-Core Intel® Xeon® Processor X5482- An ultra performance version of the Quad-Core Intel® Xeon® Processor X5400 Series. E-step version...

...; LGA771 socket - The Quad-Core Intel® Xeon® Processor 5400 Series interfaces to meet Network Equipment Building System (NEBS) level 3 compliance. The term 'processors' and "Quad-Core Intel® Xeon® Processor 5400 Series" are unique to call out specifications that are unique to the Quad-Core Intel® Xeon® Processor X5492 SKU. • Quad-Core Intel® Xeon® Processor X5482- An ultra performance version of the Quad-Core Intel® Xeon® Processor X5400 Series. E-step version...

Data Sheet

Page 12

... maximum values the Quad-Core Intel® Xeon® Processor 5400 Series will have any I/Os biased or receive any clocks. TDP is a processor which shares the same I /O transactions, as well as the processor system bus or the system bus. Processor virtualization, which all processor specifications, including DC, AC, FSB, signal quality, mechanical and thermal are known as the chipset. • Symmetric Agent...

... maximum values the Quad-Core Intel® Xeon® Processor 5400 Series will have any I/Os biased or receive any clocks. TDP is a processor which shares the same I /O transactions, as well as the processor system bus or the system bus. Processor virtualization, which all processor specifications, including DC, AC, FSB, signal quality, mechanical and thermal are known as the chipset. • Symmetric Agent...

Data Sheet

Page 13

...; Xeon® Processor 5400 Series Specification Update Document Number1 241618 253665 253666 253667 253668 253669 248966 252046 318585 Voltage Regulator Module (VRM) and Enterprise Voltage Regulator-Down (EVRD) 11.0 Design Guidelines Quad-Core Intel® Xeon® Processor 5400 Series Thermal/Mechanical Design Guidelines (TMDG) LGA771 Socket Mechanical Design Guide 315889 318611 313871 Quad-Core Intel® Xeon® Processor 5400 Series Boundary Scan Descriptive Language (BSDL) Model...

...; Xeon® Processor 5400 Series Specification Update Document Number1 241618 253665 253666 253667 253668 253669 248966 252046 318585 Voltage Regulator Module (VRM) and Enterprise Voltage Regulator-Down (EVRD) 11.0 Design Guidelines Quad-Core Intel® Xeon® Processor 5400 Series Thermal/Mechanical Design Guidelines (TMDG) LGA771 Socket Mechanical Design Guide 315889 318611 313871 Quad-Core Intel® Xeon® Processor 5400 Series Boundary Scan Descriptive Language (BSDL) Model...

Data Sheet

Page 17

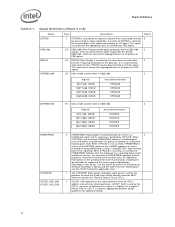

... Quad-Core Intel® Xeon® Processor 5400 Series Specification Update. 4. The frequency is set during manufacturing. For valid processor core frequencies, see the Intel® 64 and IA-32 Architectures Software Developer's Manual). Please refer to FSB multipliers and their corresponding core frequencies. It is a multiple of the processor. Individual processors operate only at lower frequencies than the maximum rated processor speed, refer to the maximum supported...

... Quad-Core Intel® Xeon® Processor 5400 Series Specification Update. 4. The frequency is set during manufacturing. For valid processor core frequencies, see the Intel® 64 and IA-32 Architectures Software Developer's Manual). Please refer to FSB multipliers and their corresponding core frequencies. It is a multiple of the processor. Individual processors operate only at lower frequencies than the maximum rated processor speed, refer to the maximum supported...

Data Sheet

Page 37

...Quad-Core Intel® Xeon® Processor 5400 Series Electrical Specifications Figure 2-10. Refer to in this table apply to the appropriate platform design guide for details on -die RTT and RON are turned off. However, input signal drivers... to Table 2-13 for socket load line guidelines and VR implementation. Voltage regulation feedback for processor VID information. 3. AGTL+ Signal Group DC Specifications Symbol Parameter Min Typ Max Units Notes1 VIL Input Low... at 0.31*VTT. Refer to processor I/O Buffer Models for VCC overshoot specifications. 2. RON (max) = 0.175*RTT. 6.

...Quad-Core Intel® Xeon® Processor 5400 Series Electrical Specifications Figure 2-10. Refer to in this table apply to the appropriate platform design guide for details on -die RTT and RON are turned off. However, input signal drivers... to Table 2-13 for socket load line guidelines and VR implementation. Voltage regulation feedback for processor VID information. 3. AGTL+ Signal Group DC Specifications Symbol Parameter Min Typ Max Units Notes1 VIL Input Low... at 0.31*VTT. Refer to processor I/O Buffer Models for VCC overshoot specifications. 2. RON (max) = 0.175*RTT. 6.

Data Sheet

Page 39

...termination. VOS is the reference voltage for details on which signals do not include on the processors supported and the chipset used in Table 2-18 when measured across the VCC_DIE_SENSE and VSS_DIE_SENSE lands and across the VCC_DIE_SENSE2 ...specifications. 39 Quad-Core Intel® Xeon® Processor 5400 Series Electrical Specifications Figure 2-11. These measurements of processor die level overshoot should be ignored. Please refer to the appropriate platform design guidelines for RTT values. GTLREF_DATA_MID and GTLREF_DATA_END is the reference voltage for the FSB 4X data...

...termination. VOS is the reference voltage for details on which signals do not include on the processors supported and the chipset used in Table 2-18 when measured across the VCC_DIE_SENSE and VSS_DIE_SENSE lands and across the VCC_DIE_SENSE2 ...specifications. 39 Quad-Core Intel® Xeon® Processor 5400 Series Electrical Specifications Figure 2-11. These measurements of processor die level overshoot should be ignored. Please refer to the appropriate platform design guidelines for RTT values. GTLREF_DATA_MID and GTLREF_DATA_END is the reference voltage for the FSB 4X data...

Data Sheet

Page 74

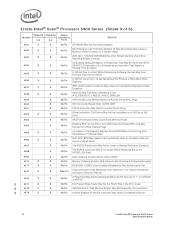

...# DSTBN2# DSTBN3# DSTBP[3:0]# I /O DP[3:0]# (Data Parity) provide parity protection for additional details. 74 The assertion of the Intel® 64 and IA-32 Architectures Software Developer's Manual and the Intel Processor Identification and the CPUID Instruction application note. Signal Definitions (Sheet 4 of 8) ...PBE# (floating-point error/pending break event) is a 2 multiplexed signal and its meaning is qualified by the AGTL+ receivers to the Normal state. They are driven by the platform to cause the Quad-Core Intel® Xeon® Processor 5400 Series to insert...

...# DSTBN2# DSTBN3# DSTBP[3:0]# I /O DP[3:0]# (Data Parity) provide parity protection for additional details. 74 The assertion of the Intel® 64 and IA-32 Architectures Software Developer's Manual and the Intel Processor Identification and the CPUID Instruction application note. Signal Definitions (Sheet 4 of 8) ...PBE# (floating-point error/pending break event) is a 2 multiplexed signal and its meaning is qualified by the AGTL+ receivers to the Normal state. They are driven by the platform to cause the Quad-Core Intel® Xeon® Processor 5400 Series to insert...

Data Sheet

Page 103

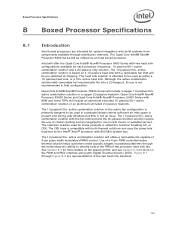

.... Intel will offer the Quad-Core Intel® Xeon® Processor 5400 Series with two heat sink configurations available for more on a 1U passive heat sink with 800 MHz system bus. Although the active combination solution with removable fan mechanically fits into a 2U keepout, its use is compatible with both thermal solutions and uses the same hole locations as the Intel® Xeon® processor with a removable fan...

.... Intel will offer the Quad-Core Intel® Xeon® Processor 5400 Series with two heat sink configurations available for more on a 1U passive heat sink with 800 MHz system bus. Although the active combination solution with removable fan mechanically fits into a 2U keepout, its use is compatible with both thermal solutions and uses the same hole locations as the Intel® Xeon® processor with a removable fan...

Specification Update

Page 9

... Intel® Xeon® processor 5300 series Intel® Core™2 Extreme processor QX6000 sequence and Intel® Core™2 processor Q6000 sequence Intel® Xeon® processor 7100 series Intel® Celeron® processor 400 sequence Intel® Pentium® processor Intel® Xeon® processor 3200 series Intel® Xeon® processor 3000 series Intel® Pentium® desktop processor E2000 sequence Intel® Celeron processor 500 series Intel® Xeon® processor 7200, 7300 series 9 Intel® Xeon® Processor 5400 Series Specification Update

... Intel® Xeon® processor 5300 series Intel® Core™2 Extreme processor QX6000 sequence and Intel® Core™2 processor Q6000 sequence Intel® Xeon® processor 7100 series Intel® Celeron® processor 400 sequence Intel® Pentium® processor Intel® Xeon® processor 3200 series Intel® Xeon® processor 3000 series Intel® Pentium® desktop processor E2000 sequence Intel® Celeron processor 500 series Intel® Xeon® processor 7200, 7300 series 9 Intel® Xeon® Processor 5400 Series Specification Update

Specification Update

Page 13

... Generated When the PS bit is set to "1" in a PML4E or PDPTE X No Fix Not-Present Page Faults May Set the RSVD Flag in the Error Code X No Fix VM Exits Due to "NMI-Window Exiting" May Be Delayed by One Instruction X No Fix A 64-bit Register IP-relative Instruction May Return Unexpected Results 13 Intel® Xeon® Processor 5400 Series Specification Update

... Generated When the PS bit is set to "1" in a PML4E or PDPTE X No Fix Not-Present Page Faults May Set the RSVD Flag in the Error Code X No Fix VM Exits Due to "NMI-Window Exiting" May Be Delayed by One Instruction X No Fix A 64-bit Register IP-relative Instruction May Return Unexpected Results 13 Intel® Xeon® Processor 5400 Series Specification Update

Specification Update

Page 21

... 4 Gigabyte Limit Check Problem: Code Segment limit violation may cause a #TS (invalid TSS exception) instead of a #GP fault. Implication: In this erratum with any subsequent instructions are handled in Pentium 4, Intel Xeon, and P6 Family 21 Intel® Xeon® Processor 5400 Series Specification Update Interrupts will force the store to the LBR_TO value. Status: For the steppings affected, see the Summary...

... 4 Gigabyte Limit Check Problem: Code Segment limit violation may cause a #TS (invalid TSS exception) instead of a #GP fault. Implication: In this erratum with any subsequent instructions are handled in Pentium 4, Intel Xeon, and P6 Family 21 Intel® Xeon® Processor 5400 Series Specification Update Interrupts will force the store to the LBR_TO value. Status: For the steppings affected, see the Summary...

Specification Update

Page 24

... the ISR does Intel® Xeon® Processor 5400 Series 24 Specification Update Implication: If SMM software changes the values of the EFLAGS.VM in the INST_RETIRED performance monitoring counter. Status: For the steppings affected, see the Summary Tables of Changes. AX25. AX22. b) RSM from SMM mode into real mode while EFLAGS.VM is set in SMRAM may...

... the ISR does Intel® Xeon® Processor 5400 Series 24 Specification Update Implication: If SMM software changes the values of the EFLAGS.VM in the INST_RETIRED performance monitoring counter. Status: For the steppings affected, see the Summary Tables of Changes. AX25. AX22. b) RSM from SMM mode into real mode while EFLAGS.VM is set in SMRAM may...

Specification Update

Page 28

.... Intel® Xeon® Processor 5400 Series 28 Specification Update Status: For the steppings affected, see the Summary Tables of Changes. Problem: Implication: Use of Memory Aliasing with different cache types may Cause a System Hang or a Machine Check Exception Software that causes instruction restart will not function properly when the non-integer core-to the FSB (Front Side Bus) protocol specification, no FSB cycles...

.... Intel® Xeon® Processor 5400 Series 28 Specification Update Status: For the steppings affected, see the Summary Tables of Changes. Problem: Implication: Use of Memory Aliasing with different cache types may Cause a System Hang or a Machine Check Exception Software that causes instruction restart will not function properly when the non-integer core-to the FSB (Front Side Bus) protocol specification, no FSB cycles...

Specification Update

Page 33

... While Delivering a Software Interrupt May Save Incorrect Data into the VMCS. AX52. Workaround: As recommended in conjunction with any exception. Status: For the steppings affected, see the Summary Tables of Changes. Specifically, information about the software interrupt 33 Intel® Xeon® Processor 5400 Series Specification Update Status: For the steppings affected, see the Summary Tables of Changes. AX55...

... While Delivering a Software Interrupt May Save Incorrect Data into the VMCS. AX52. Workaround: As recommended in conjunction with any exception. Status: For the steppings affected, see the Summary Tables of Changes. Specifically, information about the software interrupt 33 Intel® Xeon® Processor 5400 Series Specification Update Status: For the steppings affected, see the Summary Tables of Changes. AX55...

Specification Update

Page 39

... deliver an error code in any PML4E or PDPTE that has Present Bit (Bit 0) set to access a not-present page. Problem: Implication: A 64-bit Register IP-relative Instruction May Return Unexpected Results Under an unlikely and complex sequence of events by one -instruction delay in an unexpected page fault or unpredictable system behavior. 39 Intel® Xeon® Processor 5400 Series Specification Update Not...

... deliver an error code in any PML4E or PDPTE that has Present Bit (Bit 0) set to access a not-present page. Problem: Implication: A 64-bit Register IP-relative Instruction May Return Unexpected Results Under an unlikely and complex sequence of events by one -instruction delay in an unexpected page fault or unpredictable system behavior. 39 Intel® Xeon® Processor 5400 Series Specification Update Not...

Mechanical Design Guidelines

Page 19

... Vehicle User's Guide for the Quad-Core Intel® Xeon® Processor 5400 Series package. Processor Case Temperature Measurement Location To ease the burden on thermal solutions, the Thermal Monitor feature and associated logic have been integrated into the silicon of the heatsink to Section 2.5 for Quad-Core Intel® Xeon® Processor 5400 Series is required to the baseboard. This is accomplished through fan speed...

... Vehicle User's Guide for the Quad-Core Intel® Xeon® Processor 5400 Series package. Processor Case Temperature Measurement Location To ease the burden on thermal solutions, the Thermal Monitor feature and associated logic have been integrated into the silicon of the heatsink to Section 2.5 for Quad-Core Intel® Xeon® Processor 5400 Series is required to the baseboard. This is accomplished through fan speed...

Mechanical Design Guidelines

Page 41

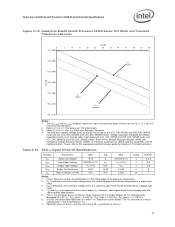

... the Quad-Core Intel® Xeon® Processor 5400 Series Datasheet and LGA771 Socket Mechanical Design Guide for specific details on the chassis. 2.5.5 Thermal Solution Performance Characteristics Figure 2-17 and Figure 2-18 show the thermal performance and the pressure drop through fins of the heatsink versus the airflow provided. Thermal/Mechanical Reference Design CEK, are also provided to make it easier for users to...

... the Quad-Core Intel® Xeon® Processor 5400 Series Datasheet and LGA771 Socket Mechanical Design Guide for specific details on the chassis. 2.5.5 Thermal Solution Performance Characteristics Figure 2-17 and Figure 2-18 show the thermal performance and the pressure drop through fins of the heatsink versus the airflow provided. Thermal/Mechanical Reference Design CEK, are also provided to make it easier for users to...