Data Sheet

Page 2

... from future changes to obtain the latest specifications and before placing your product order. Copyright © 2007-2008, Intel Corporation. 2 Quad-Core Intel® Xeon® Processor 5400 Series Datasheet NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY... (including 32-bit operation) without notice. Intel may contain design defects or errors known as the property of Intel Corporation or its subsidiaries in medical, life saving, or life sustaining applications. The Quad-Core Intel® Xeon® Processor 5400 Series may make changes ...

... from future changes to obtain the latest specifications and before placing your product order. Copyright © 2007-2008, Intel Corporation. 2 Quad-Core Intel® Xeon® Processor 5400 Series Datasheet NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY... (including 32-bit operation) without notice. Intel may contain design defects or errors known as the property of Intel Corporation or its subsidiaries in medical, life saving, or life sustaining applications. The Quad-Core Intel® Xeon® Processor 5400 Series may make changes ...

Data Sheet

Page 3

Contents 1 Introduction ...9 1.1 Terminology ...10 1.2 State of Data ...13 1.3 References ...13 2 Quad-Core Intel® Xeon® Processor 5400 Series Electrical Specifications 15 2.1 Front Side Bus and GTLREF 15 2.2 Power and Ground Lands 16... Specifications 48 3.6 Processor Mass Specifications 48 3.7 Processor Materials 48 3.8 Processor Markings 48 3.9 Processor Land Coordinates 49 4 Land Listing...51 4.1 Quad-Core Intel® Xeon® Processor 5400 Series Pin Assignments 51 4.1.1 Land Listing by Land Name 51 4.1.2 Land Listing by Land Number 61 5 Signal Definitions ......

Contents 1 Introduction ...9 1.1 Terminology ...10 1.2 State of Data ...13 1.3 References ...13 2 Quad-Core Intel® Xeon® Processor 5400 Series Electrical Specifications 15 2.1 Front Side Bus and GTLREF 15 2.2 Power and Ground Lands 16... Specifications 48 3.6 Processor Mass Specifications 48 3.7 Processor Materials 48 3.8 Processor Markings 48 3.9 Processor Land Coordinates 49 4 Land Listing...51 4.1 Quad-Core Intel® Xeon® Processor 5400 Series Pin Assignments 51 4.1.1 Land Listing by Land Name 51 4.1.2 Land Listing by Land Number 61 5 Signal Definitions ......

Data Sheet

Page 4

... HALT or Extended HALT State 98 7.2.3 Stop-Grant State 100 7.2.4 Extended HALT Snoop or HALT Snoop State, Stop Grant Snoop State 101 7.3 Enhanced Intel SpeedStep® Technology 101 8 Boxed Processor Specifications 103 8.1 Introduction ...103 8.2 Mechanical Specifications 105 8.2.1 Boxed Processor Heat Sink Dimensions (CEK 105 8.2.2 ...117 9.2 Target System Implementation 117 9.2.1 System Implementation 117 9.3 Logic Analyzer Interface (LAI 117 9.3.1 Mechanical Considerations 118 9.3.2 Electrical Considerations 118 4 Quad-Core Intel® Xeon® Processor 5400 Series Datasheet

... HALT or Extended HALT State 98 7.2.3 Stop-Grant State 100 7.2.4 Extended HALT Snoop or HALT Snoop State, Stop Grant Snoop State 101 7.3 Enhanced Intel SpeedStep® Technology 101 8 Boxed Processor Specifications 103 8.1 Introduction ...103 8.2 Mechanical Specifications 105 8.2.1 Boxed Processor Heat Sink Dimensions (CEK 105 8.2.2 ...117 9.2 Target System Implementation 117 9.2.1 System Implementation 117 9.3 Logic Analyzer Interface (LAI 117 9.3.1 Mechanical Considerations 118 9.3.2 Electrical Considerations 118 4 Quad-Core Intel® Xeon® Processor 5400 Series Datasheet

Data Sheet

Page 5

... 49 3-7 Processor Land Coordinates, Bottom View 50 6-1 Quad-Core Intel® Xeon® Processor X5492 and X5482 (C-step)Thermal Profile ......... 81 6-2 Quad-Core Intel® Xeon® Processor X5400 Series Thermal Profiles A and B 83 6-3 Quad-Core Intel® Xeon® Processor E5400 Series Thermal Profile 86 6-4 Quad-Core Intel® Xeon® Processor L5400 Series Thermal Profile 87 6-5 Quad-Core Intel® Xeon® Processor L5408 Thermal Profile 89 6-6 Case...

... 49 3-7 Processor Land Coordinates, Bottom View 50 6-1 Quad-Core Intel® Xeon® Processor X5492 and X5482 (C-step)Thermal Profile ......... 81 6-2 Quad-Core Intel® Xeon® Processor X5400 Series Thermal Profiles A and B 83 6-3 Quad-Core Intel® Xeon® Processor E5400 Series Thermal Profile 86 6-4 Quad-Core Intel® Xeon® Processor L5400 Series Thermal Profile 87 6-5 Quad-Core Intel® Xeon® Processor L5408 Thermal Profile 89 6-6 Case...

Data Sheet

Page 6

... Thermal Specifications 83 6-4 Quad-Core Intel® Xeon® Processor X5400 Series Thermal Profile A Table 84 6-5 Quad-Core Intel® Xeon® Processor X5400 Series Thermal Profile B Table 85 6-6 Quad-Core Intel® Xeon® Processor E5400 Series Thermal Specifications 85 6-7 Quad-Core Intel® Xeon® Processor E5400 Series Thermal Profile Table 86 6-8 Quad-Core Intel® Xeon® Processor L5400 Series Thermal Specifications 87 6-9 Quad-Core Intel® Xeon® Processor L5400...

... Thermal Specifications 83 6-4 Quad-Core Intel® Xeon® Processor X5400 Series Thermal Profile A Table 84 6-5 Quad-Core Intel® Xeon® Processor X5400 Series Thermal Profile B Table 85 6-6 Quad-Core Intel® Xeon® Processor E5400 Series Thermal Specifications 85 6-7 Quad-Core Intel® Xeon® Processor E5400 Series Thermal Profile Table 86 6-8 Quad-Core Intel® Xeon® Processor L5400 Series Thermal Specifications 87 6-9 Quad-Core Intel® Xeon® Processor L5400...

Data Sheet

Page 7

Revision History Revision 001 002 003 004 005 Description Initial release Added product information for the Quad-Core Intel® Xeon® Processor L5400 Series. Corrected L1 cache size Introduced X5492 Updated X5482 power levels on E-step Maintains change bars from version 004. Added...X5482 falls into the 120W X5400 family. Denoted in Introduction section. § Date November 2007 March 2008 April 2008 August 2008 August 2008 Quad-Core Intel® Xeon® Processor 5400 Series Datasheet 7 Added product information for the Quad-Core Intel® Xeon® Processor L5408.

Revision History Revision 001 002 003 004 005 Description Initial release Added product information for the Quad-Core Intel® Xeon® Processor L5400 Series. Corrected L1 cache size Introduced X5492 Updated X5482 power levels on E-step Maintains change bars from version 004. Added...X5482 falls into the 120W X5400 family. Denoted in Introduction section. § Date November 2007 March 2008 April 2008 August 2008 August 2008 Quad-Core Intel® Xeon® Processor 5400 Series Datasheet 7 Added product information for the Quad-Core Intel® Xeon® Processor L5408.

Data Sheet

Page 9

...a set of hardware enhancements that exploit buffer overrun vulnerabilities and can be found in enterprise environments. Quad-Core Intel® Xeon® Processor 5400 Series features include Intel® Wide Dynamic Execution, enhanced floating point and multi-media units, Streaming SIMD Extensions 2 (...bit wide registers and a separate register for hardware-assisted virtualization within the processor. In addition, the Quad-Core Intel® Xeon® Processor 5400 Series supports the Execute Disable Bit functionality. The processor is a server/workstation processor utilizing...

...a set of hardware enhancements that exploit buffer overrun vulnerabilities and can be found in enterprise environments. Quad-Core Intel® Xeon® Processor 5400 Series features include Intel® Wide Dynamic Execution, enhanced floating point and multi-media units, Streaming SIMD Extensions 2 (...bit wide registers and a separate register for hardware-assisted virtualization within the processor. In addition, the Quad-Core Intel® Xeon® Processor 5400 Series supports the Execute Disable Bit functionality. The processor is a server/workstation processor utilizing...

Data Sheet

Page 10

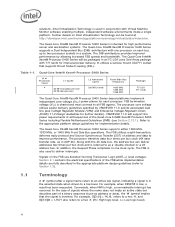

...Voltage Regulator Module (VRM) and Enterprise Voltage Regulator-Down (EVRD) 11.0 Design Guidelines for high performance server and workstation systems. The Quad-Core Intel® Xeon® Processor 5400 Series supports a Dual Independent Bus (DIB) architecture with the 4X data bus, the address bus can be ... associated load line (see Section 2.13.1). It utilizes a surface mount LGA771 socket that the signal is used to as a 'double-clocked' or a 2X address bus. Table 1-1. The Quad-Core Intel® Xeon® Processor 5400 Series is in the asserted state when driven to two...

...Voltage Regulator Module (VRM) and Enterprise Voltage Regulator-Down (EVRD) 11.0 Design Guidelines for high performance server and workstation systems. The Quad-Core Intel® Xeon® Processor 5400 Series supports a Dual Independent Bus (DIB) architecture with the 4X data bus, the address bus can be ... associated load line (see Section 2.13.1). It utilizes a surface mount LGA771 socket that the signal is used to as a 'double-clocked' or a 2X address bus. Table 1-1. The Quad-Core Intel® Xeon® Processor 5400 Series is in the asserted state when driven to two...

Data Sheet

Page 11

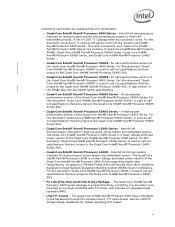

... a pinless substrate with nominal and short-term conditions designed to the Quad-Core Intel® Xeon® Processor X5400 Series SKU. • Quad-Core Intel® Xeon® Processor E5400 Series - See the LGA771 Socket Design Guidelines for the "Quad-Core Intel® Xeon® Processor 5400 Series". The term 'processors' and "Quad-Core Intel® Xeon® Processor 5400 Series" are unique to call out specifications...

... a pinless substrate with nominal and short-term conditions designed to the Quad-Core Intel® Xeon® Processor X5400 Series SKU. • Quad-Core Intel® Xeon® Processor E5400 Series - See the LGA771 Socket Design Guidelines for the "Quad-Core Intel® Xeon® Processor 5400 Series". The term 'processors' and "Quad-Core Intel® Xeon® Processor 5400 Series" are unique to call out specifications...

Data Sheet

Page 12

... one -wire bus interface that connects the processor to take advantage of the maximum values the Quad-Core Intel® Xeon® Processor 5400 Series will have any I /O subsystem and memory array, and runs the same operating system as indicated on the.... It is typically known as interrupt messages, pass between Intel processor and external thermal monitoring devices, for future processors may be sealed in a tray, or loose. An enhancement to Intel's IA-32 architecture that the processor can dissipate. • Intel®64 Architecture - PECI replaces the thermal diode available...

... one -wire bus interface that connects the processor to take advantage of the maximum values the Quad-Core Intel® Xeon® Processor 5400 Series will have any I /O subsystem and memory array, and runs the same operating system as indicated on the.... It is typically known as interrupt messages, pass between Intel processor and external thermal monitoring devices, for future processors may be sealed in a tray, or loose. An enhancement to Intel's IA-32 architecture that the processor can dissipate. • Intel®64 Architecture - PECI replaces the thermal diode available...

Data Sheet

Page 13

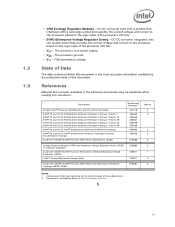

... 253669 248966 252046 318585 Voltage Regulator Module (VRM) and Enterprise Voltage Regulator-Down (EVRD) 11.0 Design Guidelines Quad-Core Intel® Xeon® Processor 5400 Series Thermal/Mechanical Design Guidelines (TMDG) LGA771 Socket Mechanical Design Guide 315889 318611 313871 Quad-Core Intel® Xeon® Processor 5400 Series Boundary Scan Descriptive Language (BSDL) Model 318587 Notes 2 2 2 2 2 2 1 2 2 Notes: 1. The processor...

... 253669 248966 252046 318585 Voltage Regulator Module (VRM) and Enterprise Voltage Regulator-Down (EVRD) 11.0 Design Guidelines Quad-Core Intel® Xeon® Processor 5400 Series Thermal/Mechanical Design Guidelines (TMDG) LGA771 Socket Mechanical Design Guide 315889 318611 313871 Quad-Core Intel® Xeon® Processor 5400 Series Boundary Scan Descriptive Language (BSDL) Model 318587 Notes 2 2 2 2 2 2 1 2 2 Notes: 1. The processor...

Data Sheet

Page 15

...to the applicable platform design guidelines for improved noise tolerance as VTT. Contact your Intel Field Representative to obtain the Quad-Core Intel® Xeon® Processor 5400 Series signal integrity models, which are terminated to control reflections on...signal is a logical 0 or a logical 1. Quad-Core Intel® Xeon® Processor 5400 Series Electrical Specifications 2 Quad-Core Intel® Xeon® Processor 5400 Series Electrical Specifications 2.1 Front Side Bus and GTLREF Most Quad-Core Intel® Xeon® Processor 5400 Series FSB signals use Assisted Gunning...

...to the applicable platform design guidelines for improved noise tolerance as VTT. Contact your Intel Field Representative to obtain the Quad-Core Intel® Xeon® Processor 5400 Series signal integrity models, which are terminated to control reflections on...signal is a logical 0 or a logical 1. Quad-Core Intel® Xeon® Processor 5400 Series Electrical Specifications 2 Quad-Core Intel® Xeon® Processor 5400 Series Electrical Specifications 2.1 Front Side Bus and GTLREF Most Quad-Core Intel® Xeon® Processor 5400 Series FSB signals use Assisted Gunning...

Data Sheet

Page 16

... speeds, the Quad-Core Intel® Xeon® Processor 5400 Series is not adequate. For further information and guidelines, refer to the appropriate platform design guidelines. For further information regarding power delivery, decoupling and layout guidelines, refer to the LGA771 socket. For further...from the regulator (EVRD or VRM pins) to the appropriate platform design guidelines. Front Side Bus AGTL+ Decoupling The Quad-Core Intel® Xeon® Processor 5400 Series integrates signal termination on the baseboard. Decoupling guidelines are described in current demand by the ...

... speeds, the Quad-Core Intel® Xeon® Processor 5400 Series is not adequate. For further information and guidelines, refer to the appropriate platform design guidelines. For further information regarding power delivery, decoupling and layout guidelines, refer to the LGA771 socket. For further...from the regulator (EVRD or VRM pins) to the appropriate platform design guidelines. Front Side Bus AGTL+ Decoupling The Quad-Core Intel® Xeon® Processor 5400 Series integrates signal termination on the baseboard. Decoupling guidelines are described in current demand by the ...

Data Sheet

Page 17

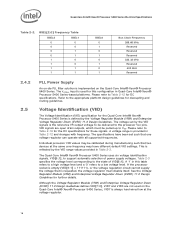

... 2.53 GHz Notes 1, 2, 3, 4 1, 2, 3 1, 2, 3 1, 2, 3 1, 2, 3 1, 2, 3 1, 2, 3 Notes: 1. As in Table 2-20. The Quad-Core Intel® Xeon® Processor 5400 Series utilizes differential clocks. If lower speeds are CMOS outputs which requires a constant frequency BCLK[1:0] input, with exceptions for the maximum speed... of the processor. BSEL[2:0] are desired, the appropriate ratio can operate. Quad-Core Intel® Xeon® Processor 5400 Series Electrical Specifications 2.4 Front Side Bus Clock (BCLK[1:0]) and Processor Clocking BCLK[1:0] ...

... 2.53 GHz Notes 1, 2, 3, 4 1, 2, 3 1, 2, 3 1, 2, 3 1, 2, 3 1, 2, 3 1, 2, 3 Notes: 1. As in Table 2-20. The Quad-Core Intel® Xeon® Processor 5400 Series utilizes differential clocks. If lower speeds are CMOS outputs which requires a constant frequency BCLK[1:0] input, with exceptions for the maximum speed... of the processor. BSEL[2:0] are desired, the appropriate ratio can operate. Quad-Core Intel® Xeon® Processor 5400 Series Electrical Specifications 2.4 Front Side Bus Clock (BCLK[1:0]) and Processor Clocking BCLK[1:0] ...

Data Sheet

Page 18

...calibrated during manufacturing such that one voltage regulator can operate with frequency. VID signals are not used for DC specifications. The Quad-Core Intel® Xeon® Processor 5400 Series uses six voltage identification signals, VID[6:1], to the processor Vcc pins. If the processor socket is... (VRM) and Enterprise Voltage Regulator-Down (EVRD) 11.0 Design Guidelines. Refer to VTT. VID7 is used on the Quad-Core Intel® Xeon® Processor 5400 Series. The voltage set such that two devices at the voltage regulator. 18 Although the Voltage Regulator ...

...calibrated during manufacturing such that one voltage regulator can operate with frequency. VID signals are not used for DC specifications. The Quad-Core Intel® Xeon® Processor 5400 Series uses six voltage identification signals, VID[6:1], to the processor Vcc pins. If the processor socket is... (VRM) and Enterprise Voltage Regulator-Down (EVRD) 11.0 Design Guidelines. Refer to VTT. VID7 is used on the Quad-Core Intel® Xeon® Processor 5400 Series. The voltage set such that two devices at the voltage regulator. 18 Although the Voltage Regulator ...

Data Sheet

Page 19

It should be capable of regulating its associated processor core voltage (VCC). This will represent a DC shift in Table 2-12 and Table 2-14. DC specifications for further details. The VRM or EVRD utilized must ... 2-12 includes VID step sizes and DC shift ranges. Transitions above the specified VID are included in the load line. Quad-Core Intel® Xeon® Processor 5400 Series Electrical Specifications The Quad-Core Intel® Xeon® Processor 5400 Series provides the ability to operate while transitioning to the Voltage Regulator Module (VRM) and Enterprise Voltage ...

It should be capable of regulating its associated processor core voltage (VCC). This will represent a DC shift in Table 2-12 and Table 2-14. DC specifications for further details. The VRM or EVRD utilized must ... 2-12 includes VID step sizes and DC shift ranges. Transitions above the specified VID are included in the load line. Quad-Core Intel® Xeon® Processor 5400 Series Electrical Specifications The Quad-Core Intel® Xeon® Processor 5400 Series provides the ability to operate while transitioning to the Voltage Regulator Module (VRM) and Enterprise Voltage ...

Data Sheet

Page 20

...state transitions (see Section 7.2.2), or Enhanced Intel SpeedStep® Technology transitions (see Section 7.3). The VID range includes VID transitions that may be disabled. 2. Quad-Core Intel® Xeon® Processor 5400 Series Electrical Specifications ... to remain within 500 ms and latch off until power is observed, the voltage regulator output should be initiated by thermal events, assertion of the Quad-Core Intel® Xeon® Processor 5400 Series. 3. Voltage Identification Definition HEX VID6 VID5 VID4 VID3 VID2 VID1 VCC_MAX 7A 1 1 1 1 0 1 0.8500 78 1...

...state transitions (see Section 7.2.2), or Enhanced Intel SpeedStep® Technology transitions (see Section 7.3). The VID range includes VID transitions that may be disabled. 2. Quad-Core Intel® Xeon® Processor 5400 Series Electrical Specifications ... to remain within 500 ms and latch off until power is observed, the voltage regulator output should be initiated by thermal events, assertion of the Quad-Core Intel® Xeon® Processor 5400 Series. 3. Voltage Identification Definition HEX VID6 VID5 VID4 VID3 VID2 VID1 VCC_MAX 7A 1 1 1 1 0 1 0.8500 78 1...

Data Sheet

Page 21

... signals to any signal to select the correct loadline slope for MS_ID[1:0] MS_ID1 0 0 1 1 MS_ID0 0 1 0 1 Description Dual-Core Intel® Xeon® Processor 5200 Series Dual-Core Intel® Xeon® Processor 5100 series Quad-Core Intel® Xeon® Processor 5300 series Quad-Core Intel® Xeon® Processor 5400 Series Note: The MS_ID[1:0] signals are used to power or ground, a resistor will also...

... signals to any signal to select the correct loadline slope for MS_ID[1:0] MS_ID1 0 0 1 1 MS_ID0 0 1 0 1 Description Dual-Core Intel® Xeon® Processor 5200 Series Dual-Core Intel® Xeon® Processor 5100 series Quad-Core Intel® Xeon® Processor 5300 series Quad-Core Intel® Xeon® Processor 5400 Series Note: The MS_ID[1:0] signals are used to power or ground, a resistor will also...

Data Sheet

Page 22

...# AGTL+ Strobes I /O group when driving. cannot be grouped with other TESTHI signals • TESTHI11 - Table 2-6 identifies which are common clock, source synchronous and asynchronous. Quad-Core Intel® Xeon® Processor 5400 Series Electrical Specifications The TESTHI signals must be grouped with respect to rising edge of a low-to assoc. AGTL+ asynchronous outputs can...

...# AGTL+ Strobes I /O group when driving. cannot be grouped with other TESTHI signals • TESTHI11 - Table 2-6 identifies which are common clock, source synchronous and asynchronous. Quad-Core Intel® Xeon® Processor 5400 Series Electrical Specifications The TESTHI signals must be grouped with respect to rising edge of a low-to assoc. AGTL+ asynchronous outputs can...

Data Sheet

Page 23

... have RTT in the package with a 50 Ω pullup to VTT. 2. These signals have RTT in the package with a 80 Ω pullup to VTT. Table 2-9. Quad-Core Intel® Xeon® Processor 5400 Series Electrical Specifications Table 2-6. Notes: 1. Refer to TCK Power/Other Signals1 BSEL[2:0], VID[6:1] BCLK[1:0] TCK, TDI, TMS, TRST# TDO COMP[3:0], GTLREF_ADD_MID...

... have RTT in the package with a 50 Ω pullup to VTT. 2. These signals have RTT in the package with a 80 Ω pullup to VTT. Table 2-9. Quad-Core Intel® Xeon® Processor 5400 Series Electrical Specifications Table 2-6. Notes: 1. Refer to TCK Power/Other Signals1 BSEL[2:0], VID[6:1] BCLK[1:0] TCK, TDI, TMS, TRST# TDO COMP[3:0], GTLREF_ADD_MID...