Product Specification

Page 4

...BIOS Defaults 50 4.5 Multiple Boot Blocks 50 iv Revision 1.3 Intel order number E15331-006 Server Board Overview ...2 2.1 Server Board Feature Set 2 2.2 Server Board Layout 4 3. Functional Architecture ...7 3.1 3.2 3.2.1 3.2.2 Processor Subsystem 8 Intel® X38 Chipset...8 Memory Controller Hub (MCH): Intel® X38 MCH 9 I/O Controller Hub: Intel® ICH9-R 9 3.3 Integrated Baseboard Management Controller 12 ......17 3.5.6 Super I/O Chip ...18 3.6 Replacing the Back-Up Battery 19 4. Table of Contents Intel® Server Board X38ML Table of Contents 1.

...BIOS Defaults 50 4.5 Multiple Boot Blocks 50 iv Revision 1.3 Intel order number E15331-006 Server Board Overview ...2 2.1 Server Board Feature Set 2 2.2 Server Board Layout 4 3. Functional Architecture ...7 3.1 3.2 3.2.1 3.2.2 Processor Subsystem 8 Intel® X38 Chipset...8 Memory Controller Hub (MCH): Intel® X38 MCH 9 I/O Controller Hub: Intel® ICH9-R 9 3.3 Integrated Baseboard Management Controller 12 ......17 3.5.6 Super I/O Chip ...18 3.6 Replacing the Back-Up Battery 19 4. Table of Contents Intel® Server Board X38ML Table of Contents 1.

Product Specification

Page 15

... 800/1066/1333MHz FSB ƒ Intel® X38 chipset components ƒ Intel® X38 MCH Memory Controller Hub ƒ Intel® ICH9R I /O panel o Two internal USB 2.0 headers - PCI Express* connector ƒ One PCI Express* x16 connector supporting PCI Express* riser card - Intel® Server Board X38ML Server Board Overview - Intel® Core™2 Duo Processor E4500 - Intel® Core™2 Duo Processor...

... 800/1066/1333MHz FSB ƒ Intel® X38 chipset components ƒ Intel® X38 MCH Memory Controller Hub ƒ Intel® ICH9R I /O panel o Two internal USB 2.0 headers - PCI Express* connector ƒ One PCI Express* x16 connector supporting PCI Express* riser card - Intel® Server Board X38ML Server Board Overview - Intel® Core™2 Duo Processor E4500 - Intel® Core™2 Duo Processor...

Product Specification

Page 20

... two components that work together to the Intel® Server Board X38ML support Web site: http://support.intel.com/support/motherboards/server/X38ML/. 3.2 Intel® X38 Chipset The Intel® Server Board X38ML is designed around the Intel® X38 chipset. Previous generations of Intel® processors are based on the Intel® Core™ micro-architecture and built on the server board, including the processor, memory, and I/O subsystems. These...

... two components that work together to the Intel® Server Board X38ML support Web site: http://support.intel.com/support/motherboards/server/X38ML/. 3.2 Intel® X38 Chipset The Intel® Server Board X38ML is designed around the Intel® X38 chipset. Previous generations of Intel® processors are based on the Intel® Core™ micro-architecture and built on the server board, including the processor, memory, and I/O subsystems. These...

Product Specification

Page 21

...provides six PCI Express* Root Ports (GEN1), which are used as two x1 ports or one x2. Intel® Server Board X38ML Functional Architecture The following sub-sections provide an overview of the primary functions and supported features of each direction... functionality for PCI Express*, LPC, USB, SATA II, IDE and SMBus, and numerous board management functions. Later sections provide more detail on the Intel® Server Board X38ML. Supports LGA775 processors in each chipset component as they are compliant with the PCI Express Base Specification, Revision 1.1. Supports 512 Mbit...

...provides six PCI Express* Root Ports (GEN1), which are used as two x1 ports or one x2. Intel® Server Board X38ML Functional Architecture The following sub-sections provide an overview of the primary functions and supported features of each direction... functionality for PCI Express*, LPC, USB, SATA II, IDE and SMBus, and numerous board management functions. Later sections provide more detail on the Intel® Server Board X38ML. Supports LGA775 processors in each chipset component as they are compliant with the PCI Express Base Specification, Revision 1.1. Supports 512 Mbit...

Product Specification

Page 68

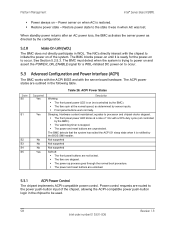

...that should not be in the powered-down activity: Source Power button BMC watchdog timer Platform event filtering Command Power state retention Chipset Table 27. This signal is activated by a momentary contact switch on or off 5.2.5.1 Power Button Signal The POWER_BUTTON signal toggles ...signal must be scanned in a constant state for 8 seconds or until PS_PWRGD is generated. The BMC waits 10 seconds. Platform Management Intel® Server Board X38ML 3. This is treated as POWER_ON) Capabilities Turns power on or off Turns power off, or power cycle Turns power off, power...

...that should not be in the powered-down activity: Source Power button BMC watchdog timer Platform event filtering Command Power state retention Chipset Table 27. This signal is activated by a momentary contact switch on or off 5.2.5.1 Power Button Signal The POWER_BUTTON signal toggles ...signal must be scanned in a constant state for 8 seconds or until PS_PWRGD is generated. The BMC waits 10 seconds. Platform Management Intel® Server Board X38ML 3. This is treated as POWER_ON) Capabilities Turns power on or off Turns power off, or power cycle Turns power off, power...

Product Specification

Page 69

...signal can change state as a result of the following events: ƒ Operating system request ƒ Real-time clock (RTC) alarm ƒ Chipset power button request response, including BMC-initiated power state changes 5.2.5.3 Power-On Enable The BMC must enable the power button pass-through and SIO circuitry... BMC to control the AC power-on behavior of its level for monitoring S5 transitions because S4 is not supported. Intel® Server Board X38ML Platform Management The signal is routed to the chipset power button signal through pass-through , as well as the PS_PWRGD signal. The...

...signal can change state as a result of the following events: ƒ Operating system request ƒ Real-time clock (RTC) alarm ƒ Chipset power button request response, including BMC-initiated power state changes 5.2.5.3 Power-On Enable The BMC must enable the power button pass-through and SIO circuitry... BMC to control the AC power-on behavior of its level for monitoring S5 transitions because S4 is not supported. Intel® Server Board X38ML Platform Management The signal is routed to the chipset power button signal through pass-through , as well as the PS_PWRGD signal. The...

Product Specification

Page 70

...ƒ The fans spin at a rate of the chipset, allowing the ACPI-compatible power push-button logic in the following table. The BMC must detect when the system is on to occur. Platform Management Intel® Server Board X38ML ƒ Power always on to occur. 5.3 Advanced ...Configuration and Power Interface (ACPI) The BMC works with the ACPI BIOS and with the server board hardware. Power control requests are unprotected.

...ƒ The fans spin at a rate of the chipset, allowing the ACPI-compatible power push-button logic in the following table. The BMC must detect when the system is on to occur. Platform Management Intel® Server Board X38ML ƒ Power always on to occur. 5.3 Advanced ...Configuration and Power Interface (ACPI) The BMC works with the ACPI BIOS and with the server board hardware. Power control requests are unprotected.

Product Specification

Page 72

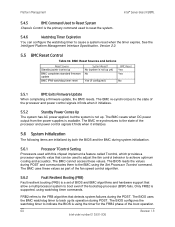

... algorithm. 5.6.2 Fault Resilient Booting (FRB) Fault resilient booting (FRB) is a set of the boot operation. 60 Revision 1.3 Intel order number E15331-006 FRB2 refers to the FRB algorithm that allow a multiprocessor system to boot even if the bootstrap processor (BSP...detects system failures during POST. Platform Management Intel® Server Board X38ML 5.4.5 BMC Command Used to Reset System Chassis Control is the primary command used to reset the system. 5.4.6 Watchdog Timer Expiration You can be used with this chipset implement a feature called Tcontrol, which provides...

... algorithm. 5.6.2 Fault Resilient Booting (FRB) Fault resilient booting (FRB) is a set of the boot operation. 60 Revision 1.3 Intel order number E15331-006 FRB2 refers to the FRB algorithm that allow a multiprocessor system to boot even if the bootstrap processor (BSP...detects system failures during POST. Platform Management Intel® Server Board X38ML 5.4.5 BMC Command Used to Reset System Chassis Control is the primary command used to reset the system. 5.4.6 Watchdog Timer Expiration You can be used with this chipset implement a feature called Tcontrol, which provides...

Product Specification

Page 74

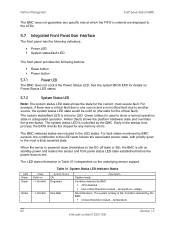

...LED state shows the state for the current, most critical asserted state. Green (status) is powered down event. Platform Management Intel® Server Board X38ML The BMC does not guarantee any memory errors. The system status/fault LED is likely to another source, the system status ... information in the startup boot process, the BIOS checks the chipset for the critical fault). The BMC-detected states are displayed to show a normal operation state or a degraded operation. temperature 62 Revision 1.3 Intel order number E15331-006 The system status LED is controlled by...

...LED state shows the state for the current, most critical asserted state. Green (status) is powered down event. Platform Management Intel® Server Board X38ML The BMC does not guarantee any memory errors. The system status/fault LED is likely to another source, the system status ... information in the startup boot process, the BIOS checks the chipset for the critical fault). The BMC-detected states are displayed to show a normal operation state or a degraded operation. temperature 62 Revision 1.3 Intel order number E15331-006 The system status LED is controlled by...

Product Specification

Page 75

...logs a SEL event when the system is in the SDR, then the system status LED behaves as asserted. This assertion is no longer active. Intel® Server Board X38ML Platform Management Color State Amber Solid on , sleep, or standby state. Condition detected by the BMC's integrated hardware. The front panel input buttons...the state of the Chassis Intrusion signal and makes the status of the Front Panel Reset signal to the BMC causes the system to the chipset. the signal must be in default SDR configuration. The de-bounce time is missing, the BMC logs a SEL event and sets the ...

...logs a SEL event when the system is in the SDR, then the system status LED behaves as asserted. This assertion is no longer active. Intel® Server Board X38ML Platform Management Color State Amber Solid on , sleep, or standby state. Condition detected by the BMC's integrated hardware. The front panel input buttons...the state of the Chassis Intrusion signal and makes the status of the Front Panel Reset signal to the BMC causes the system to the chipset. the signal must be in default SDR configuration. The de-bounce time is missing, the BMC logs a SEL event and sets the ...

Product Specification

Page 81

... supports a digital thermal sensor that provides a communication channel between the managed components, referred to as temperature between Intel processors and chipset components to determine the current fan domain state. The digital thermal sensors are divided into fan domains, each processor...has three states: sleep, nominal, and boost. The nominal state has a variable speed determined by throttling the processor. Intel® Server Board X38ML Platform Management 5.15.1.2 IERR Monitoring The BMC monitors the internal error (IERR) signal from each of which has a separate...

... supports a digital thermal sensor that provides a communication channel between the managed components, referred to as temperature between Intel processors and chipset components to determine the current fan domain state. The digital thermal sensors are divided into fan domains, each processor...has three states: sleep, nominal, and boost. The nominal state has a variable speed determined by throttling the processor. Intel® Server Board X38ML Platform Management 5.15.1.2 IERR Monitoring The BMC monitors the internal error (IERR) signal from each of which has a separate...

Product Specification

Page 85

...Yes N/A N/A N/A No N/A No 5.19.2 User Model The BMC supports the IPMI 2.0 user model including User ID 1 support. Intel® Server Board X38ML Platform Management Table 37. A total of four simultaneous sessions. This allows the state of other intelligent controllers in the chassis to be directed.../Response Protocol The protocols are assigned with a response message. They are mapped into the host I/O space and accessed via the chipset LPC bus. For example, both request messages and response messages in the IPMI 2.0 specification. An intelligent device acting as an ...

...Yes N/A N/A N/A No N/A No 5.19.2 User Model The BMC supports the IPMI 2.0 user model including User ID 1 support. Intel® Server Board X38ML Platform Management Table 37. A total of four simultaneous sessions. This allows the state of other intelligent controllers in the chassis to be directed.../Response Protocol The protocols are assigned with a response message. They are mapped into the host I/O space and accessed via the chipset LPC bus. For example, both request messages and response messages in the IPMI 2.0 specification. An intelligent device acting as an ...

Product Specification

Page 104

Error Reporting and Handling Intel® Server Board X38ML the BMC as PCI Express* Bus Uncorrectable errors. The uncorrectable errors ...: ƒ Memory errors (see Section 6.2.3.1) ƒ PCI bus errors (see Section 6.2.3.3) 92 Revision 1.3 Intel order number E15331-006 This specification describes the format of all but two bytes in the processor model specific register (MSR)... and the chipset. The ability to isolate the failure down to detect software or hardware failures and that parses...

Error Reporting and Handling Intel® Server Board X38ML the BMC as PCI Express* Bus Uncorrectable errors. The uncorrectable errors ...: ƒ Memory errors (see Section 6.2.3.1) ƒ PCI bus errors (see Section 6.2.3.3) 92 Revision 1.3 Intel order number E15331-006 This specification describes the format of all but two bytes in the processor model specific register (MSR)... and the chipset. The ability to isolate the failure down to detect software or hardware failures and that parses...

Product Specification

Page 110

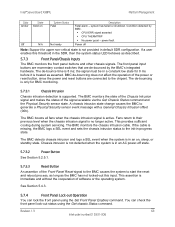

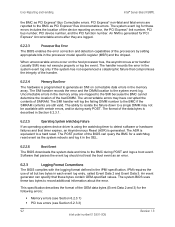

... initialization of the host processor (bootstrap processor) Host processor cache initialization (including AP) Starting application processor initialization SMM initialization Initializing a chipset component Reading configuration data from memory (SPD on the Intel® Server Board X38ML 6.3.2 POST Code Checkpoints Table 49. POST Progress Code LED Example 8h Red Green 1 1 Amber MSB Red 0 Green 4h Green 1 Red...

... initialization of the host processor (bootstrap processor) Host processor cache initialization (including AP) Starting application processor initialization SMM initialization Initializing a chipset component Reading configuration data from memory (SPD on the Intel® Server Board X38ML 6.3.2 POST Code Checkpoints Table 49. POST Progress Code LED Example 8h Red Green 1 1 Amber MSB Red 0 Green 4h Green 1 Red...

Product Specification

Page 114

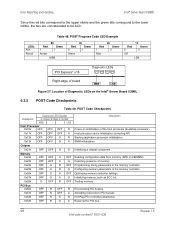

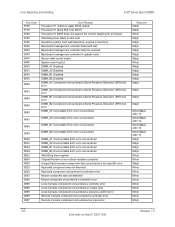

Error Reporting and Handling Intel® Server Board X38ML Error Code 8160 8170 8180 8190 8198 8300 84F2 84F3 84F4 84FF 8540 8541 8544 8545 8560 8561 8564 8565 8580 8581 8584 8585... error encountered DIMM_A1 Uncorrectable ECC error encountered DIMM_A2 Uncorrectable ECC error encountered DIMM_B1 Uncorrectable ECC error encountered DIMM_B2 Uncorrectable ECC error encountered WatchDog timer expired Chipset Reclaim of non-critical variables complete Unspecified processor component has encountered a non-specific error Keyboard component was not detected Keyboard component encountered a controller ...

Error Reporting and Handling Intel® Server Board X38ML Error Code 8160 8170 8180 8190 8198 8300 84F2 84F3 84F4 84FF 8540 8541 8544 8545 8560 8561 8564 8565 8580 8581 8584 8585... error encountered DIMM_A1 Uncorrectable ECC error encountered DIMM_A2 Uncorrectable ECC error encountered DIMM_B1 Uncorrectable ECC error encountered DIMM_B2 Uncorrectable ECC error encountered WatchDog timer expired Chipset Reclaim of non-critical variables complete Unspecified processor component has encountered a non-specific error Keyboard component was not detected Keyboard component encountered a controller ...