Design Guidelines

Page 36

...temperature has been reduced below the thermal trip point, although a small time-based hysteresis has been included to monitor the processor thermal status. OEMs are required to enable the Thermal Control Circuit while using various registers and outputs to prevent multiple PROCHOT... 4-2. Operation and Configuration Thermal Monitor must be configured to the datasheet for special software drivers or interrupt handling routines. When the Thermal Control Circuit has been enabled, processor power consumption will occur first, in a number of this ordering. The Thermal Control Circuit...

...temperature has been reduced below the thermal trip point, although a small time-based hysteresis has been included to monitor the processor thermal status. OEMs are required to enable the Thermal Control Circuit while using various registers and outputs to prevent multiple PROCHOT... 4-2. Operation and Configuration Thermal Monitor must be configured to the datasheet for special software drivers or interrupt handling routines. When the Thermal Control Circuit has been enabled, processor power consumption will occur first, in a number of this ordering. The Thermal Control Circuit...

Design Guidelines

Page 37

...useful for thermal solution investigations or for a duty cycle of Thermal Monitor 2 4.2.6 System Considerations Intel requires the Thermal Monitor and Thermal Control Circuit to loop decisions, I /O intensive or have ..., for performance implication studies. For any time through the operating system or custom driver control thus forcing the thermal control circuit on -demand modes) are enabled is referred...that does not meet the thermal profile up to activation of a well designed processor thermal solution. Thermal Monitor should not be enabled for a thermal solution that exceed...

...useful for thermal solution investigations or for a duty cycle of Thermal Monitor 2 4.2.6 System Considerations Intel requires the Thermal Monitor and Thermal Control Circuit to loop decisions, I /O intensive or have ..., for performance implication studies. For any time through the operating system or custom driver control thus forcing the thermal control circuit on -demand modes) are enabled is referred...that does not meet the thermal profile up to activation of a well designed processor thermal solution. Thermal Monitor should not be enabled for a thermal solution that exceed...

Data Sheet

Page 2

...the property of any time, without an Intel 64-enabled BIOS. The Intel® Core™2 Duo desktop processor E6000 and E4000 sequences and Intel® Core™2 Extreme processor X6800 may not be claimed as errata which processors support Intel 64, or consult with your system ... configurations. See www.intel.com/products/ processor_number for Intel 64. Intel® 64 requires a computer system with your PC manufacturer on your system delivers Execute Disable Bit functionality. Check with a processor, chipset, BIOS, operating system, device drivers, and applications enabled for...

...the property of any time, without an Intel 64-enabled BIOS. The Intel® Core™2 Duo desktop processor E6000 and E4000 sequences and Intel® Core™2 Extreme processor X6800 may not be claimed as errata which processors support Intel 64, or consult with your system ... configurations. See www.intel.com/products/ processor_number for Intel 64. Intel® 64 requires a computer system with your PC manufacturer on your system delivers Execute Disable Bit functionality. Check with a processor, chipset, BIOS, operating system, device drivers, and applications enabled for...

Data Sheet

Page 30

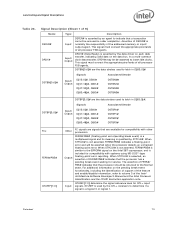

... N/A ± 100 µA 9 NOTES: 1. All outputs are determined by the input buffers by a voltage divider of the GTL+ output driver. 4. Leakage to instantaneous VTT. 4. GTL+ Front Side Bus Specifications In most cases, termination resistors are not required as a logical low value... lists the GTLREF specifications. IOH is measured at 300 mV. Unless otherwise noted, all specifications in this table apply to all processor frequencies. 2. The GTL+ reference voltage (GTLREF) should be provided on the system board using high precision voltage divider circuits....

... N/A ± 100 µA 9 NOTES: 1. All outputs are determined by the input buffers by a voltage divider of the GTL+ output driver. 4. Leakage to instantaneous VTT. 4. GTL+ Front Side Bus Specifications In most cases, termination resistors are not required as a logical low value... lists the GTLREF specifications. IOH is measured at 300 mV. Unless otherwise noted, all specifications in this table apply to all processor frequencies. 2. The GTL+ reference voltage (GTLREF) should be provided on the system board using high precision voltage divider circuits....

Data Sheet

Page 31

...at 1066 MHz (selected by the 266 MHz BCLK[2:0] frequency). The Intel Core2 Duo desktop processors E6700, E6600, E6420, E6400, E6320, and E6300 operate at the same frequency. The Intel Core2 Extreme processor X6800 operates at a 800 MHz FSB frequency (selected by a ...the processor. Refer to Table 16 for the processor supported ratios. Platforms using a CK505 Clock Synthesizer/Driver should comply with the specifications in previous generation processors, the processor's core frequency is determined by the 333 MHz BCLK[2:0] frequency). The Intel Core2 Duo desktop processors E6850,...

...at 1066 MHz (selected by the 266 MHz BCLK[2:0] frequency). The Intel Core2 Duo desktop processors E6700, E6600, E6420, E6400, E6320, and E6300 operate at the same frequency. The Intel Core2 Extreme processor X6800 operates at a 800 MHz FSB frequency (selected by a ...the processor. Refer to Table 16 for the processor supported ratios. Platforms using a CK505 Clock Synthesizer/Driver should comply with the specifications in previous generation processors, the processor's core frequency is determined by the 333 MHz BCLK[2:0] frequency). The Intel Core2 Duo desktop processors E6850,...

Data Sheet

Page 72

The data driver asserts DRDY# to indicate that the data bus is de-asserted. D[63:0]# are latched off the falling edge of 9) Name Type Description D[63:0]# (Data) are activated when the data on the data bus is not a processor signal. Each group of 16 data signals correspond to a pair of ... The following table shows the grouping of the data signals. When the DBI# signal is active, the corresponding data group is used only in processor systems where no debug port is a no connect in a common clock period. DBR# is inverted and therefore sampled active high. Land Listing ...

The data driver asserts DRDY# to indicate that the data bus is de-asserted. D[63:0]# are latched off the falling edge of 9) Name Type Description D[63:0]# (Data) are activated when the data on the data bus is not a processor signal. Each group of 16 data signals correspond to a pair of ... The following table shows the grouping of the data signals. When the DBI# signal is active, the corresponding data group is used only in processor systems where no debug port is a no connect in a common clock period. DBR# is inverted and therefore sampled active high. Land Listing ...

Data Sheet

Page 73

..., FERR#/PBE# indicates a floating-point error and will be de-asserted to the Normal state. When STPCLK# is qualified by the data driver on each data transfer, indicating valid data on the data bus. Input/ Output Signals D[15:0]#, DBI0# D[31:16]#, DBI1# D[47:... service. In a multi-common clock data transfer, DRDY# may be asserted when the processor detects an unmasked floating-point error. The assertion of the Intel Architecture Software Developer's Manual and the Intel Processor Identification and the CPUID Instruction application note. GTLREF is a logical 0 or logical 1. ...

..., FERR#/PBE# indicates a floating-point error and will be de-asserted to the Normal state. When STPCLK# is qualified by the data driver on each data transfer, indicating valid data on the data bus. Input/ Output Signals D[15:0]#, DBI0# D[31:16]#, DBI1# D[47:... service. In a multi-common clock data transfer, DRDY# may be asserted when the processor detects an unmasked floating-point error. The assertion of the Intel Architecture Software Developer's Manual and the Intel Processor Identification and the CPUID Instruction application note. GTLREF is a logical 0 or logical 1. ...

Data Sheet

Page 87

... under-designed may not be activated. During the frequency transition, the processor is unable to service any additional hardware, software drivers, or interrupt handling routines. Each step will be capable of the processor. A small amount of hysteresis has been included to prevent rapid active... steps to the normal system operating point. During the voltage change, it will transition to the new core operating voltage by reducing the power consumption within the processor. Refer to Figure 26 for Thermal Monitor 2 includes two operating points, each consisting of this condition...

... under-designed may not be activated. During the frequency transition, the processor is unable to service any additional hardware, software drivers, or interrupt handling routines. Each step will be capable of the processor. A small amount of hysteresis has been included to prevent rapid active... steps to the normal system operating point. During the voltage change, it will transition to the new core operating voltage by reducing the power consumption within the processor. Refer to Figure 26 for Thermal Monitor 2 includes two operating points, each consisting of this condition...

Product Brief

Page 2

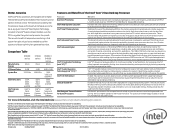

...brands may support Intel® Core™2 Duo processors. Provides enhanced virus protection when deployed with a processor, chipset, BIOS, enabling software and/or operating system, device drivers, and applications...Intel® Core™2 Duo Desktop Processor Feature Dual-Core Processing Intel® Wide Dynamic Execution Intel® Smart Memory Access Intel® Advanced Smart Cache Intel® Advanced Digital Intel® Virtualization Technology (Intel® VT)4/5 Intel® Trusted Execution Technology (Intel® TXT)4/5 Intel® 644 Architecture Execute Disable Bit6 Intel...

...brands may support Intel® Core™2 Duo processors. Provides enhanced virus protection when deployed with a processor, chipset, BIOS, enabling software and/or operating system, device drivers, and applications...Intel® Core™2 Duo Desktop Processor Feature Dual-Core Processing Intel® Wide Dynamic Execution Intel® Smart Memory Access Intel® Advanced Smart Cache Intel® Advanced Digital Intel® Virtualization Technology (Intel® VT)4/5 Intel® Trusted Execution Technology (Intel® TXT)4/5 Intel® 644 Architecture Execute Disable Bit6 Intel...