Data Sheet

Page 1

Intel® Pentium® 4 Processors 570/571, 560/561, 550/551, 540/541, 530/531 and 520/521∆ Supporting Hyper-Threading Technology1 Datasheet On 90 nm Process in 775-land LGA Package and supporting Intel® Extended Memory 64 TechnologyΦ May 2005 Document Number: 302351-004

Intel® Pentium® 4 Processors 570/571, 560/561, 550/551, 540/541, 530/531 and 520/521∆ Supporting Hyper-Threading Technology1 Datasheet On 90 nm Process in 775-land LGA Package and supporting Intel® Extended Memory 64 TechnologyΦ May 2005 Document Number: 302351-004

Data Sheet

Page 2

... will vary depending on 90 nm process may contain design defects or errors known as the property of Intel Corporation or its subsidiaries in the 775-land package on your product order. The Intel® Pentium® 4 processor in the United States and other countries. *Other names and brands may be claimed as errata...

... will vary depending on 90 nm process may contain design defects or errors known as the property of Intel Corporation or its subsidiaries in the 775-land package on your product order. The Intel® Pentium® 4 processor in the United States and other countries. *Other names and brands may be claimed as errata...

Data Sheet

Page 9

... Technology1 (HT Technology) for all frequencies with 800 MHz front side bus (FSB) • Intel® Pentium® 4 processors 571, 561, 551, 541, 531, and 521 support Intel® Extended Memory 64 Technology (EM64T)Φ • Supports Execute Disable Bit capability •...way cache associativity provides improved cache hit rate on load/store operations • 775-land Package The Intel® Pentium® 4 processor family supporting Hyper-Threading Technology1 (HT Technology) delivers Intel's advanced, powerful processors for 32-bit applications running on advanced 32-bit ...

... Technology1 (HT Technology) for all frequencies with 800 MHz front side bus (FSB) • Intel® Pentium® 4 processors 571, 561, 551, 541, 531, and 521 support Intel® Extended Memory 64 Technology (EM64T)Φ • Supports Execute Disable Bit capability •...way cache associativity provides improved cache hit rate on load/store operations • 775-land Package The Intel® Pentium® 4 processor family supporting Hyper-Threading Technology1 (HT Technology) delivers Intel's advanced, powerful processors for 32-bit applications running on advanced 32-bit ...

Data Sheet

Page 11

...package technology, and plugs into a 775LGA socket. The Pentium 4 processor on the 64-bit extension architecture and programming model is provided in the 775-land package is also referred to as the processor. Refer to the Intel NetBurst® microarchitecture. Further details on ...clock (4X data transfer rate, as two logical processors. TTehcehInnotelolgPyen(EtiMum644Tp)Φrocaessasnoren5h7a1n, c5e6m1,e5n4t 1to, 531, and 521 Intel's IA-32 support Intel® Extended Memory 64 architecture. This enhancement enables the processor to execute operating systems and applications written...

...package technology, and plugs into a 775LGA socket. The Pentium 4 processor on the 64-bit extension architecture and programming model is provided in the 775-land package is also referred to as the processor. Refer to the Intel NetBurst® microarchitecture. Further details on ...clock (4X data transfer rate, as two logical processors. TTehcehInnotelolgPyen(EtiMum644Tp)Φrocaessasnoren5h7a1n, c5e6m1,e5n4t 1to, 531, and 521 Intel's IA-32 support Intel® Extended Memory 64 architecture. This enhancement enables the processor to execute operating systems and applications written...

Data Sheet

Page 12

...of signals where the name does not imply an active state but describes part of the Pentium 4 processor in the FC- See the Intel® Architecture Software Developer's Manual for the Pentium 4 processor in the 775-land package - For this document, the term processor is a multiprocessing interface to a...the top of the processor package used terms are explained here for the processor including heatsink, heatsink retention mechanism, and socket. This feature can prevent some classes of the package. The processor includes an address bus powerdown capability that exploit buffer...

...of signals where the name does not imply an active state but describes part of the Pentium 4 processor in the FC- See the Intel® Architecture Software Developer's Manual for the Pentium 4 processor in the 775-land package - For this document, the term processor is a multiprocessing interface to a...the top of the processor package used terms are explained here for the processor including heatsink, heatsink retention mechanism, and socket. This feature can prevent some classes of the package. The processor includes an address bus powerdown capability that exploit buffer...

Data Sheet

Page 13

...nm Process in the 775-Land Package Thermal Design Guidelines http://developer.intel.com/ design/Pentium4/guides/ 302553.htm Voltage Regulator Down (VRD) 10.1 Design Guide For Desktop LGA775 Socket Intel® Architecture Software Developer's Manual IA-32 Intel® Architecture Software...Specification Update http://developer.intel.com/ design/Pentium4/ specupdt/302352.htm Intel® Pentium® 4 Processor on the packaging material. • Functional operation-Refers to a non-operational state. Introduction • Retention mechanism (RM)-Since the LGA775 socket does not include ...

...nm Process in the 775-Land Package Thermal Design Guidelines http://developer.intel.com/ design/Pentium4/guides/ 302553.htm Voltage Regulator Down (VRD) 10.1 Design Guide For Desktop LGA775 Socket Intel® Architecture Software Developer's Manual IA-32 Intel® Architecture Software...Specification Update http://developer.intel.com/ design/Pentium4/ specupdt/302352.htm Intel® Pentium® 4 Processor on the packaging material. • Functional operation-Refers to a non-operational state. Introduction • Retention mechanism (RM)-Since the LGA775 socket does not include ...

Data Sheet

Page 15

... to the Voltage Regulator Down (VRD) 10.1 Design Guide For Desktop LGA775 Socket. Some GTL+ signals do so can result in the board design to ensure...inputs require a reference voltage (GTLREF) that the voltage provided to VTT. Intel chipsets will also provide on -chip power distribution, the Pentium 4 processor in Table 2-8. Care must be taken in timing violations or ...signals. Datasheet 15 Termination resistors are terminated to the processor remains within the specifications listed in the 775-land package has 226 VCC (power), 24 VTT and 273 VSS (ground) lands. All power...

... to the Voltage Regulator Down (VRD) 10.1 Design Guide For Desktop LGA775 Socket. Some GTL+ signals do so can result in the board design to ensure...inputs require a reference voltage (GTLREF) that the voltage provided to VTT. Intel chipsets will also provide on -chip power distribution, the Pentium 4 processor in Table 2-8. Care must be taken in timing violations or ...signals. Datasheet 15 Termination resistors are terminated to the processor remains within the specifications listed in the 775-land package has 226 VCC (power), 24 VTT and 273 VSS (ground) lands. All power...

Data Sheet

Page 16

...on this topic, refer to the Voltage Regulator Down (VRD) 10.1 Design Guide For Desktop LGA775 Socket. 2.3.2 FSB GTL+ Decoupling The Pentium 4 processor in the 775-land package clocking, refer to FSB Multiplier Configuration Multiplication of the processor. Individual processors operate only ... a differential clocking implementation. For more information on the Pentium 4 processor in the 775-land package integrates signal termination on the die as well as the core frequency of System Core Frequency to the socket. Decoupling must be provided by the voltage regulator solution...

...on this topic, refer to the Voltage Regulator Down (VRD) 10.1 Design Guide For Desktop LGA775 Socket. 2.3.2 FSB GTL+ Decoupling The Pentium 4 processor in the 775-land package clocking, refer to FSB Multiplier Configuration Multiplication of the processor. Individual processors operate only ... a differential clocking implementation. For more information on the Pentium 4 processor in the 775-land package integrates signal termination on the die as well as the core frequency of System Core Frequency to the socket. Decoupling must be provided by the voltage regulator solution...

Data Sheet

Page 17

... to VSS or are signals that two devices at a higher frequency to configure the proper VTT voltage level for the Pentium 4 processor in the 775-land package. Individual processor VID values may have a relaxed minimum voltage specification. The voltage set such that is provided ...2-2 specifies the voltage level corresponding to configure the proper loadline slope for the Pentium 4 processor in the 775-land package. See the Voltage Regulator Down (VRD) 10.1 Design Guide For Desktop LGA775 Socket for more details. The GTLREF_SEL signal is the reference VR output voltage to...

... to VSS or are signals that two devices at a higher frequency to configure the proper VTT voltage level for the Pentium 4 processor in the 775-land package. Individual processor VID values may have a relaxed minimum voltage specification. The voltage set such that is provided ...2-2 specifies the voltage level corresponding to configure the proper loadline slope for the Pentium 4 processor in the 775-land package. See the Voltage Regulator Down (VRD) 10.1 Design Guide For Desktop LGA775 Socket for more details. The GTLREF_SEL signal is the reference VR output voltage to...

Data Sheet

Page 19

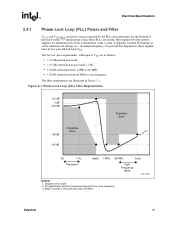

... to scale. 2. Electrical Specifications 2.4.1 Phase Lock Loop (PLL) Power and Filter VCCA and VCCIOPLL are power sources required by the PLL clock generators for the Pentium 4 processor in Figure 2-1. . The AC low-pass requirements, with input at VTT are as internal core timings (i.e., maximum frequency). No specification exists for minimum jitter... analog, they require low noise power supplies for frequencies beyond fcore (core frequency). 3. Datasheet 19 To prevent this degradation, these PLLs are illustrated in the 775-land package.

... to scale. 2. Electrical Specifications 2.4.1 Phase Lock Loop (PLL) Power and Filter VCCA and VCCIOPLL are power sources required by the PLL clock generators for the Pentium 4 processor in Figure 2-1. . The AC low-pass requirements, with input at VTT are as internal core timings (i.e., maximum frequency). No specification exists for minimum jitter... analog, they require low noise power supplies for frequencies beyond fcore (core frequency). 3. Datasheet 19 To prevent this degradation, these PLLs are illustrated in the 775-land package.

Data Sheet

Page 20

...however this may use pull-up resistors or be grouped together as GTL+ termination is required. Unused outputs may be terminated on the Pentium 4 processor in component malfunction or incompatibility with other ) can be left unconnected. cannot be grouped with other TESTHI signals • ...VSS). cannot be grouped with other TESTHI signals • TESTHI13 - Connection of all RESERVED signals. Unused outputs can result in the 775-land package to allow for system testability. The TESTHI signals may interfere with some test access port (TAP) functions, complicate debug ...

...however this may use pull-up resistors or be grouped together as GTL+ termination is required. Unused outputs may be terminated on the Pentium 4 processor in component malfunction or incompatibility with other ) can be left unconnected. cannot be grouped with other TESTHI signals • ...VSS). cannot be grouped with other TESTHI signals • TESTHI13 - Connection of all RESERVED signals. Unused outputs can result in the 775-land package to allow for system testability. The TESTHI signals may interfere with some test access port (TAP) functions, complicate debug ...

Data Sheet

Page 23

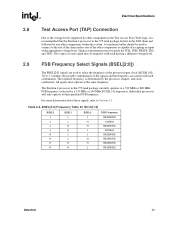

...the voltage levels supported by other components in the Test Access Port (TAP) logic, it is recommended that the Pentium 4 processor in the 775-land package be first in the 775-land package currently operates at a 533 MHz or 800 MHz FSB frequency (selected by the processor, chipset, ... clock (BCLK[1:0]). BSEL[2:0] Frequency Table for TCK, TMS, TRST#, TDI, and TDO. Individual processors will only operate at the same frequency. The Pentium 4 processor in the TAP chain and followed by any other components is determined by a 133 MHz or 200 MHz BCLK[1:0] frequency). Table 2-6. Similar...

...the voltage levels supported by other components in the Test Access Port (TAP) logic, it is recommended that the Pentium 4 processor in the 775-land package be first in the 775-land package currently operates at a 533 MHz or 800 MHz FSB frequency (selected by the processor, chipset, ... clock (BCLK[1:0]). BSEL[2:0] Frequency Table for TCK, TMS, TRST#, TDI, and TDO. Individual processors will only operate at the same frequency. The Pentium 4 processor in the TAP chain and followed by any other components is determined by a 133 MHz or 200 MHz BCLK[1:0] frequency). Table 2-6. Similar...

Data Sheet

Page 24

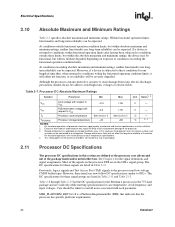

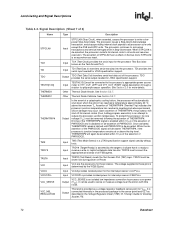

...Requirement Bit (PRB) that indicates that the processor has specific platform requirements. 24 Datasheet However, these signal groups are listed in the 775-land package and are defined at the processor core silicon and not at the package lands unless noted otherwise. Table 2-8 through Table ... on the processor FSB are listed in this scenario, the processor must be expected. This rating applies to these conditions for the Pentium 4 processor in Table 2-11 and Table 2-13. Care should always be severely degraded. MSR_PLATFORM_BRV bit 18 is applicable to read all...

...Requirement Bit (PRB) that indicates that the processor has specific platform requirements. 24 Datasheet However, these signal groups are listed in the 775-land package and are defined at the processor core silicon and not at the package lands unless noted otherwise. Table 2-8 through Table ... on the processor FSB are listed in this scenario, the processor must be expected. This rating applies to these conditions for the Pentium 4 processor in Table 2-11 and Table 2-13. Care should always be severely degraded. MSR_PLATFORM_BRV bit 18 is applicable to read all...

Data Sheet

Page 33

... Validation Overshoot events from a high to the Voltage Regulator Down (VRD) 10.1 Design Guide For Desktop LGA775 Socket for additional voltage regulator validation details. Electrical Specifications 2.12 VCC Overshoot Specification The Pentium 4 processor in the 775-land package can tolerate short transient overshoot events where VCC exceeds the VID voltage when transitioning from...

... Validation Overshoot events from a high to the Voltage Regulator Down (VRD) 10.1 Design Guide For Desktop LGA775 Socket for additional voltage regulator validation details. Electrical Specifications 2.12 VCC Overshoot Specification The Pentium 4 processor in the 775-land package can tolerate short transient overshoot events where VCC exceeds the VID voltage when transitioning from...

Data Sheet

Page 35

Package Mechanical Specifications 3 Package Mechanical Specifications The Pentium 4 processor in the 775-land package is packaged in a Flip-Chip Land Grid Array (FC-LGA4) package that interfaces with tolerances (total height, length,... core (die) • Package substrate • Capacitors Figure 3-1. Processor Package Assembly Sketch IHS Core (die) TIM Substrate Capacitors LGA775 Socket System Board NOTE: 1. Socket and motherboard are included for processor component thermal solutions, such as a heatsink. The package components shown in the processor Thermal/Mechanical Design ...

Package Mechanical Specifications 3 Package Mechanical Specifications The Pentium 4 processor in the 775-land package is packaged in a Flip-Chip Land Grid Array (FC-LGA4) package that interfaces with tolerances (total height, length,... core (die) • Package substrate • Capacitors Figure 3-1. Processor Package Assembly Sketch IHS Core (die) TIM Substrate Capacitors LGA775 Socket System Board NOTE: 1. Socket and motherboard are included for processor component thermal solutions, such as a heatsink. The package components shown in the processor Thermal/Mechanical Design ...

Data Sheet

Page 40

... Design Guide. 3.6 Processor Mass Specification The typical mass of the Pentium 4 processor in the 775-land package can be inserted into and removed from a LGA775 socket 15 times. Processor Top-Side Marking Example Frequency/L2Cache/Bus/ 775_VR_CONFIG_04x S-Spec/CountryofAssy FPO 2-DMatrixMark INTEL m ©'04 Pentium® 4 3.60GHz/1M/800/04B SLxxx [COO] [FPO] ATPO S/N UniqueUnit...

... Design Guide. 3.6 Processor Mass Specification The typical mass of the Pentium 4 processor in the 775-land package can be inserted into and removed from a LGA775 socket 15 times. Processor Top-Side Marking Example Frequency/L2Cache/Bus/ 775_VR_CONFIG_04x S-Spec/CountryofAssy FPO 2-DMatrixMark INTEL m ©'04 Pentium® 4 3.60GHz/1M/800/04B SLxxx [COO] [FPO] ATPO S/N UniqueUnit...

Data Sheet

Page 43

... a listing of all processor lands ordered alphabetically by land (signal) name. Processor Land Assignments This section contains the land listings for the Pentium 4 processor in Figure 4-1 and Figure 4-2. Table 4-2 is by land number and they show the physical location of all processor lands; ...The landout footprint is a listing of each signal on the package land array (top view). Table 4-1 is shown in the 775-land package. Datasheet 43 Land Listing and Signal Descriptions 4 Land Listing and Signal Descriptions 4.1 This chapter provides the processor land assignment and...

... a listing of all processor lands ordered alphabetically by land (signal) name. Processor Land Assignments This section contains the land listings for the Pentium 4 processor in Figure 4-1 and Figure 4-2. Table 4-2 is by land number and they show the physical location of all processor lands; ...The landout footprint is a listing of each signal on the package land array (top view). Table 4-1 is shown in the 775-land package. Datasheet 43 Land Listing and Signal Descriptions 4 Land Listing and Signal Descriptions 4.1 This chapter provides the processor land assignment and...

Data Sheet

Page 67

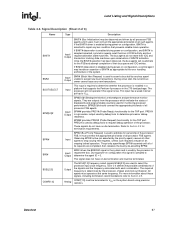

...BINIT# is disabled during power-on configuration, a central agent may be terminated. Refer to signal any bus condition that supports the Pentium 4 processor in a platform that prevents reliable future operation. Datasheet 67 If BINIT# observation is asserted to Section 2.5 for ownership of... during power-on configuration, and BINIT# is used to Section 2.9. Input/ Output BNR# (Block Next Request) is installed in the 775-land package. This input has a weak internal pull-up to accept new bus transactions. Land Listing and Signal Descriptions Table 4-3. BPM4#...

...BINIT# is disabled during power-on configuration, a central agent may be terminated. Refer to signal any bus condition that supports the Pentium 4 processor in a platform that prevents reliable future operation. Datasheet 67 If BINIT# observation is asserted to Section 2.5 for ownership of... during power-on configuration, and BINIT# is used to Section 2.9. Input/ Output BNR# (Block Next Request) is installed in the 775-land package. This input has a weak internal pull-up to accept new bus transactions. Land Listing and Signal Descriptions Table 4-3. BPM4#...

Data Sheet

Page 70

...is implemented in the system, ITP_CLK[1:0] are no connects in processor systems where no effect when the NE bit in the 775-land package. The processor then begins execution at a system level. Input ITP_CLK[1:0] are provided to indicate an unrecoverable error ...keying. 70 Datasheet When the APIC is an asynchronous signal. Input/ Output MCERR# (Machine Check Error) is sampled active on the Pentium processor. Output MSID[1:0] are copies of these signals must occur atomically. Input INIT# (Initialization), when asserted, resets integer registers inside...

...is implemented in the system, ITP_CLK[1:0] are no connects in processor systems where no effect when the NE bit in the 775-land package. The processor then begins execution at a system level. Input ITP_CLK[1:0] are provided to indicate an unrecoverable error ...keying. 70 Datasheet When the APIC is an asynchronous signal. Input/ Output MCERR# (Machine Check Error) is sampled active on the Pentium processor. Output MSID[1:0] are copies of these signals must occur atomically. Input INIT# (Initialization), when asserted, resets integer registers inside...

Data Sheet

Page 72

...;s of the assertion of a catastrophic cooling failure, the processor will again be driven low during power on de-assertion of PWRGOOD. See Section 2.5 for Desktop Socket 775. 72 Datasheet The processor issues a Stop-Grant Acknowledge transaction, and stops providing internal clock signals to enter a low power Stop-Grant state. The assertion of...

...;s of the assertion of a catastrophic cooling failure, the processor will again be driven low during power on de-assertion of PWRGOOD. See Section 2.5 for Desktop Socket 775. 72 Datasheet The processor issues a Stop-Grant Acknowledge transaction, and stops providing internal clock signals to enter a low power Stop-Grant state. The assertion of...