English Manual.

Page 9

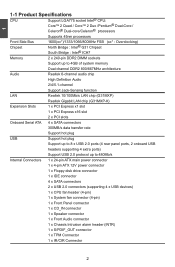

...Dual-core/Celeron® processors Supports 45nm processors Front Side Bus 1600(oc*)/1333/1066/800MHz FSB (oc* : Overclocking) Chipset North Bridge : Intel® G31 Chipset South Bridge : Intel® ICH7 Memory 2 x 240-pin DDR2 DIMM sockets Support up to 4GB of ...Dual channel DDR2 800/667MHz architecture Audio Realtek 6-channel audio chip High Definition Audio 2/4/5.1-channel Support Jack-Sensing function LAN Realtek 10/100Mb/s LAN chip (G31MXP) Realtek Gigabit LAN chip (G31MXP-K) Expansion Slots 1 x PCI Express x1 slot 1 x PCI Express x16 slot 2 x...

...Dual-core/Celeron® processors Supports 45nm processors Front Side Bus 1600(oc*)/1333/1066/800MHz FSB (oc* : Overclocking) Chipset North Bridge : Intel® G31 Chipset South Bridge : Intel® ICH7 Memory 2 x 240-pin DDR2 DIMM sockets Support up to 4GB of ...Dual channel DDR2 800/667MHz architecture Audio Realtek 6-channel audio chip High Definition Audio 2/4/5.1-channel Support Jack-Sensing function LAN Realtek 10/100Mb/s LAN chip (G31MXP) Realtek Gigabit LAN chip (G31MXP-K) Expansion Slots 1 x PCI Express x1 slot 1 x PCI Express x16 slot 2 x...

English Manual.

Page 37

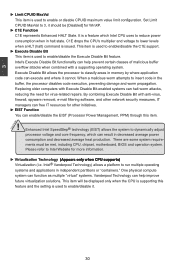

...Disable Bit functionality can result in halt state. Enhanced Intel SpeedStep® technology (EIST) allows the system to dynamically adjust processor voltage and core frequency, which Intel CPU uses to reduce power consumption when in decreased average power consumption and decreased average ... solutions. There are some system requirements must be displayed only when the CPU is supporting this item. ! When a malicious worm attempts to classify areas in the buffer, the processor disables code execution, preventing damage and worm propagation. This item will be met, including...

...Disable Bit functionality can result in halt state. Enhanced Intel SpeedStep® technology (EIST) allows the system to dynamically adjust processor voltage and core frequency, which Intel CPU uses to reduce power consumption when in decreased average power consumption and decreased average ... solutions. There are some system requirements must be displayed only when the CPU is supporting this item. ! When a malicious worm attempts to classify areas in the buffer, the processor disables code execution, preventing damage and worm propagation. This item will be met, including...

English Manual.

Page 48

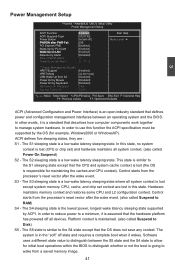

...is responsible for maintaining the caches and CPU context). The S2 sleeping state is a low wake latency sleeping state. Control starts from the processor's reset vector after the wake event. CPU, cache, and chip set ) and hardware maintains all system context is similar to Disk) ...Help [S3(STR)] [Instant-off all devices. Control starts from the processor's reset vector after the wake event. (also called Suspend to wake from S3 [Disabled] Power On by Mouse [Disabled] Power On by ACPI. HPET Support [Enabled] HPET Mode [32-bit mode] USB Wake Up from a...

...is responsible for maintaining the caches and CPU context). The S2 sleeping state is a low wake latency sleeping state. Control starts from the processor's reset vector after the wake event. CPU, cache, and chip set ) and hardware maintains all system context is similar to Disk) ...Help [S3(STR)] [Instant-off all devices. Control starts from the processor's reset vector after the wake event. (also called Suspend to wake from S3 [Disabled] Power On by Mouse [Disabled] Power On by ACPI. HPET Support [Enabled] HPET Mode [32-bit mode] USB Wake Up from a...