English Manual.

Page 9

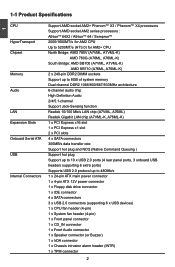

... socket AM2+ PhenomTM X3 / PhenomTM X4 processors Support AMD socket AM2 series processors : AthlonTM 64X2 / AthlonTM 64 / SempronTM HyperTransport 2000/1600MT/s for AM2 CPU Up to 5200MT/s (HT3.0) for AM2+ CPU Chipset North Bridge: AMD 780V (A7VML, A7VML-K) AMD 760G (A76ML, A76ML-K) South Bridge: AMD SB700 (A7VML, A7VML-K) AMD SB710 (A76ML, A76ML-K) Memory 2 x 240-pin DDR2 DIMM...

... socket AM2+ PhenomTM X3 / PhenomTM X4 processors Support AMD socket AM2 series processors : AthlonTM 64X2 / AthlonTM 64 / SempronTM HyperTransport 2000/1600MT/s for AM2 CPU Up to 5200MT/s (HT3.0) for AM2+ CPU Chipset North Bridge: AMD 780V (A7VML, A7VML-K) AMD 760G (A76ML, A76ML-K) South Bridge: AMD SB700 (A7VML, A7VML-K) AMD SB710 (A76ML, A76ML-K) Memory 2 x 240-pin DDR2 DIMM...

English Manual.

Page 30

... set the PCI latency timer. Advanced BIOS Features CMOS Setup Utility - Setting values are running an older operating system that only supports MPS 1.1. ► PCI Latency Timer This item is a specification by which PC manufacturers design and build CPU architecture systems with...was the original specification. Copyright (C) 1985-2008, American Megatrends, Inc. In addition, MPS 1.4 introduces support for improved support of the MPS that doesn't come with two or more processors. You also need to select the time out value for a longer time. MPS version 1.4 adds extended...

... set the PCI latency timer. Advanced BIOS Features CMOS Setup Utility - Setting values are running an older operating system that only supports MPS 1.1. ► PCI Latency Timer This item is a specification by which PC manufacturers design and build CPU architecture systems with...was the original specification. Copyright (C) 1985-2008, American Megatrends, Inc. In addition, MPS 1.4 introduces support for improved support of the MPS that doesn't come with two or more processors. You also need to select the time out value for a longer time. MPS version 1.4 adds extended...

English Manual.

Page 35

... Current CPU Speed : 2400MHz, Current FSB Multiplier : 12x Able to [Auto] for managing the cache protocol. Other (non processor-processor) HT links are initialized between processors are coherent HT links as they do not have memory cache. It is highly recommended to set to Change Freq. : Yes... uCode Patch Level : 0x1000083 Cool 'N' Quiet [Enabled] C1E Support [Disabled] CPU-NB HT Link Speed [Auto] NCHT Incoming Link ...

... Current CPU Speed : 2400MHz, Current FSB Multiplier : 12x Able to [Auto] for managing the cache protocol. Other (non processor-processor) HT links are initialized between processors are coherent HT links as they do not have memory cache. It is highly recommended to set to Change Freq. : Yes... uCode Patch Level : 0x1000083 Cool 'N' Quiet [Enabled] C1E Support [Disabled] CPU-NB HT Link Speed [Auto] NCHT Incoming Link ...

English Manual.

Page 39

... Controller This item is used to select which graphics controller is not supported. This fixed amount of page-locked graphics memory is freed for both the ATI PCIe-based graphics card and the ATI integrated graphics processor (IGP). The integrated graphics processor (IGP) is automatically disabled, and the system memory allocated to the...

... Controller This item is used to select which graphics controller is not supported. This fixed amount of page-locked graphics memory is freed for both the ATI PCIe-based graphics card and the ATI integrated graphics processor (IGP). The integrated graphics processor (IGP) is automatically disabled, and the system memory allocated to the...

English Manual.

Page 45

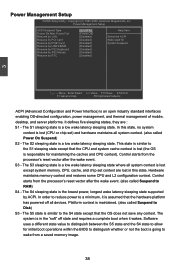

... image. 38 CPU, cache, and chip set ) and hardware maintains all devices. The S4 sleeping state is the lowest power, longest wake latency sleeping state supported by RTC [S3 (STR)] Help Item [Power Off] [Disabled] Select the ACPI [Disabled] State used for [Disabled] System Suspend. [Disabled] [Disabled] ... of mobile, desktop, and server platforms. It defines five sleeping states, they are lost except system memory. Control starts from the processor's reset vector after the wake event. In order to reduce power to the S1 sleeping state except that the OS does not save...

... image. 38 CPU, cache, and chip set ) and hardware maintains all devices. The S4 sleeping state is the lowest power, longest wake latency sleeping state supported by RTC [S3 (STR)] Help Item [Power Off] [Disabled] Select the ACPI [Disabled] State used for [Disabled] System Suspend. [Disabled] [Disabled] ... of mobile, desktop, and server platforms. It defines five sleeping states, they are lost except system memory. Control starts from the processor's reset vector after the wake event. In order to reduce power to the S1 sleeping state except that the OS does not save...