Adaptec 1737100 - 62044 SGL ENET PCI 4CH Support and Manuals

Get Help and Manuals for this Adaptec item

This item is in your list!

View All Support Options Below

Free Adaptec 1737100 manuals!

Problems with Adaptec 1737100?

Ask a Question

Free Adaptec 1737100 manuals!

Problems with Adaptec 1737100?

Ask a Question

Popular Adaptec 1737100 Manual Pages

Programmer Manual - Page 4

... bits, 1 stop bit, no liability resulting from the use the Adaptec Interactive Support System, call 408-934-7274, M -F, 6:00 A.M.

to 5:00 P.M., Pacific Time.

While reasonable efforts have questions about many of your problem and then provides step-by-step troubleshooting instructions. you with a product support representative, call 800-959-7274 or 408-945-2550, 24 hours...

Programmer Manual - Page 7

... 7-84

8 Sample Driver

Code Conventions 8-1 Producer-Consumer Model for the AIC-6915...Model 8-9 Receive Polling Model 8-9 Receive Initialization 8-9 Receive Interrupt Handling 8-15 Transmit Process 8-16 Transmit Completion Descriptor Queue 8-16

Transmit Completion Descriptor Types 8-17 Transmit Buffer Descriptor Queue 8-17

Document Title: AIC-6915 Ethernet LAN Controller Programmer's

Manual...

Programmer Manual - Page 18

... EEPROM for downloading chip configurations and MAC

address s INTA_ interrupt generation from hardware, firmware, and software controlled

sources s Supports PCI slave accesses to PCI Configuration Header from configuration

(read/write), I/O (indirect, read only) and memory address spaces (read only) s Supports PCI slave access to AIC-6915 functional registers from indirect I /O

and memory address...

Programmer Manual - Page 46

...error is serviced. This option can request the AIC-6915 to the driver...error is done internally in the PCI Configuration Status register) status active. The PCI master is required for five PCLKs (SAC - dual address cycle) after FRAME_ is set...Ethernet LAN Controller Programmer's Manual

PCI Master Module

The PCI... reading extra bytes might cause a problem. The PCI master does not retry...

Programmer Manual - Page 47

...support 64-bit PCI data path, the REQ64_ must be set to determine whether the system supports a 64-bit data path. This means that AD[2:0] must assert REQ64_ during the time that the target is a 32-bit device and does not support...asserts FRAME_ and REQ64_ to the timing specification. Under this situation, it is very ...

RST_ REQ64_

// REQ64_ to RST_ s

setup min 102 cycle time

//

RST_ to ...

Programmer Manual - Page 50

...are no current of pending transfers.

AIC-6915 Ethernet LAN Controller Programmer's Manual

Power Management

The PCI bus power management defined four power states. In the...represent power managed states. Table 4-1 shows the states supported by software through the PMCSR register.

When a function is accomplished by setting the Powerstate bits in the PMC (Power Management Capabilities)...

Programmer Manual - Page 54

...even parity that contained the error. SERR_ is sourcing the ...set. As a target device, the AIC-6915 allows accesses to it detects an address parity error only if the PERRESPEN (Parity Error Response Enable, COMMAND register in PCI Configuration header) and SERRESPEN (System Error...support writes to complete the decode. The AIC-6915 only supports...value on an address errors. Memory Address Space...

Programmer Manual - Page 58

... wake-up frames. AIC-6915 Ethernet LAN Controller Programmer's Manual

s LC= 0, 1 or 2, and EXCONCLOCK is set, or s Read/Write instruction is executed and the Input IOREADY is on a byte boundary... given by Microsoft On-Now specification, including assertion of carry information (GFPDATAIN[17:16]). The data read a location pointed by the instruction.

Transmit Checksum Accelerator

To accelerate...

Programmer Manual - Page 78

... bit enables the AIC-6915 to respond to be asserted.

The AIC-6915 does not support VSNOOPEN.

When MSPACEEN is detected as a target for detected address parity errors.

When active (=1) indicates a master can be a bus master. MSPACEEN is set inactive during the data phase of PCI_PCIRST_

7-6

VSNOOPEN: VGA Snoop Enable, Always reads 0. When...

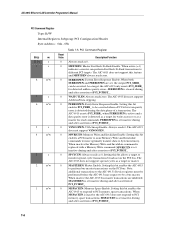

Programmer Manual - Page 80

... supports Fast Back-To-Back

transactions. Response time for assertion of PCI_PCIRST_ or by the AIC-6915, refer to - Setting this...fatal error condition.

If this bit

indicates that the target is a read only bit.

0

Reserved: Always read as 0

7-8 Setting this ...Ethernet LAN Controller Programmer's Manual

Bit(s)

rw

11

r/w

Table 7-6. Illegal Write. STA is set , the register at ...

Programmer Manual - Page 82

... PCI MWRIC, MRDLC or MRDMC commands.

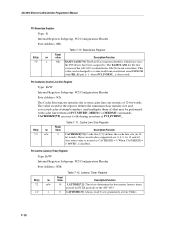

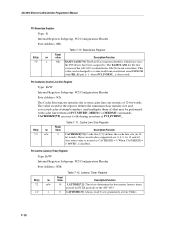

AIC-6915 Ethernet LAN Controller Programmer's Manual

PCI Baseclass Register Type: R Internal Registers Subgroup: PCI Configuration Header Byte Address...PCI_PCIRST_ is disabled.

When CACHESIZE = 0, MWRIC is deasserted. Those word values supported are reset to 0h during assertion of 32-bit words. Bit(s)

rw

7:0 ...sets granularity at four CLKs).

7-10

Programmer Manual - Page 168

...set by the driver upon initialization and whenever a receive buffer resource has been freed by setting the RX64BITBUFFERADDRESSES bit to the first buffer used by the driver to the Type 0 descriptor. The VALID bit is set when the receive producer-consumer model...when the operating system supports 64-bit addressing. ... Ethernet LAN Controller Programmer's Manual

Type 2 Completion Descriptor The...

Programmer Manual - Page 173

....RxDescQ1Entries = 1; // use 2K receive buffer descriptors. Sample Driver

// assign the base address of the variable-size queue. AIC6915_WRITE_REG...variable size queue RxDescQueue1CtrlValue.RxVariableSizeQueues = 1; // use polling model RxDescQueue1CtrlValue.RxPrefetchDescriptors = 1; // set for RxDescQueue2Ctrl // Set up the Receive Buffer Descriptor Queue

8-13 use default ...

Programmer Manual - Page 174

...'re using polling model on the receive side. This initializes the Receive Buffer Descriptor // Producer and Consumer indices to AIC-6915 AIC6915_WRITE_REG(RxDescQueue1LowAddress, RxDescQLowAddrValue);

// Use default value for RxDescQueue2LowAddress

// Initialize RxDescQueueHighAddr // set up the high 32 bits of address - AIC-6915 Ethernet LAN Controller Programmer's Manual

8-14

// If single...

Programmer Manual - Page 176

... have processed all current entries in size. The type which interrupt has been enabled in the driver. Adapter->RxDescQProducerIndex = RxDescIndex;

// We're done with the Valid bit // Set the previous last descriptor to the protocol (operating system specific). If dual transmit queues are two types of Transmit Completion Descriptors is based on which...

Adaptec 1737100 Reviews

Do you have an experience with the Adaptec 1737100 that you would like to share?

Earn 750 points for your review!

We have not received any reviews for Adaptec yet.

Earn 750 points for your review!