Aspire T670 and Power Fe Service Guide

Page 26

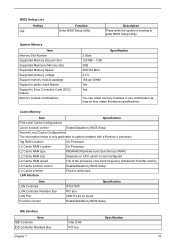

... Utility. BIOS Hotkey List Hotkey c Function Enter BIOS Setup Utility Description Press while the system is local configured L2 Cache RAM speed Full of the processor core clock frequency (Advanced Transfer Cache) L2 Cache function control Enable/Disable by BIOS Setup L2...The information below is only applicable to system installed with a Pentium 4 processor Tag RAM Location On Processor L2 Cache RAM Location On Processor L2 Cache RAM type PBSRAM (Pipelined-burst Synchronous RAM) L2 Cache RAM size Depends on CPU, which is booting to Error Correction Code (ECC) feature Memory...

... Utility. BIOS Hotkey List Hotkey c Function Enter BIOS Setup Utility Description Press while the system is local configured L2 Cache RAM speed Full of the processor core clock frequency (Advanced Transfer Cache) L2 Cache function control Enable/Disable by BIOS Setup L2...The information below is only applicable to system installed with a Pentium 4 processor Tag RAM Location On Processor L2 Cache RAM Location On Processor L2 Cache RAM type PBSRAM (Pipelined-burst Synchronous RAM) L2 Cache RAM size Depends on CPU, which is booting to Error Correction Code (ECC) feature Memory...

Aspire T670 and Power Fe Service Guide

Page 62

...processor and cache memory subsystem T Direct Memory Access (DMA) controller T Interrupt system T Three programmable timers T ROM subsystem T RAM subsystem T CMOS RAM subsystem and real time clock/calendar with built-in physical address 1000:0 Reserved 58 Chapter 4 The main components on the main ...C3h C5h 01h 02h Description Test CMOS R/W functionality Early chipset initialization: -Disable shadow RAM -Disable L2 cache (socket 7 or below) -Program basic chipset registers Detect memory -Auto-detection of DRAM size, type and ECC. -Auto-detection of L2 cache (socket 7 or below) Expand ...

...processor and cache memory subsystem T Direct Memory Access (DMA) controller T Interrupt system T Three programmable timers T ROM subsystem T RAM subsystem T CMOS RAM subsystem and real time clock/calendar with built-in physical address 1000:0 Reserved 58 Chapter 4 The main components on the main ...C3h C5h 01h 02h Description Test CMOS R/W functionality Early chipset initialization: -Disable shadow RAM -Disable L2 cache (socket 7 or below) -Program basic chipset registers Detect memory -Auto-detection of DRAM size, type and ECC. -Auto-detection of L2 cache (socket 7 or below) Expand ...