Specification Update

Page 1

Intel® Core™2 Extreme Processor X6800Δ and Intel® Core™2 Duo Desktop Processor E6000Δ and E4000Δ Sequence Specification Update - Document Number: 313279-027 Current characterized errata are documented in the 775-land LGA Package supporting Intel® 64Φ Architecture, Intel® Virtualization Technology± and Intel® Trusted Execution Technologyŧ December 2010 Notice: The Intel®...

Intel® Core™2 Extreme Processor X6800Δ and Intel® Core™2 Duo Desktop Processor E6000Δ and E4000Δ Sequence Specification Update - Document Number: 313279-027 Current characterized errata are documented in the 775-land LGA Package supporting Intel® 64Φ Architecture, Intel® Virtualization Technology± and Intel® Trusted Execution Technologyŧ December 2010 Notice: The Intel®...

Specification Update

Page 2

... IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Copyright © 2006 - 2010, Intel Corporation 2 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update

... IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Copyright © 2006 - 2010, Intel Corporation 2 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update

Specification Update

Page 4

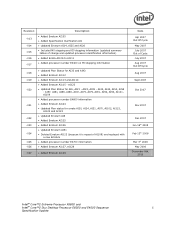

... 2007 Out Of Cycle Feb 2007 Mar 2007 Apr 2007 Apr 2007 Out Of Cycle 4 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update AI100 • Added Erratum AI101-AI104 • Updated ... -004 -005 -006 -007 -008 -009 -010 -011 -012 Description • Initial release of the Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 Sequence Specification Update • Updated Erratum AI19, AI29 and AI40 • Added Erratum AI58-AI67 • Updated...

... 2007 Out Of Cycle Feb 2007 Mar 2007 Apr 2007 Apr 2007 Out Of Cycle 4 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update AI100 • Added Erratum AI101-AI104 • Updated ... -004 -005 -006 -007 -008 -009 -010 -011 -012 Description • Initial release of the Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 Sequence Specification Update • Updated Erratum AI19, AI29 and AI40 • Added Erratum AI58-AI67 • Updated...

Specification Update

Page 5

...8226; Updated Erratum AI51 • Deleted Erratum AI123 (because it is repeat of AI108) and replaced with a new Erratum • Added processor number E4700 information • Added Erratum AI127, AI128 -027 • Added Erratum AI129 Date Apr 2007 Out Of Cycle May 2007 July 2007...2007 Oct 2007 Nov 2007 Dec 2007 Jan 16th 2008 Feb 13th 2008 Mar 3rd 2008 May 2008 December 8th, 2010 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 5 Specification Update AI23, AI38 - AI42, AI44, AI50, AI55 - AI123 • Updated ...

...8226; Updated Erratum AI51 • Deleted Erratum AI123 (because it is repeat of AI108) and replaced with a new Erratum • Added processor number E4700 information • Added Erratum AI127, AI128 -027 • Added Erratum AI129 Date Apr 2007 Out Of Cycle May 2007 July 2007...2007 Oct 2007 Nov 2007 Dec 2007 Jan 16th 2008 Feb 13th 2008 Mar 3rd 2008 May 2008 December 8th, 2010 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 5 Specification Update AI23, AI38 - AI42, AI44, AI50, AI55 - AI123 • Updated ...

Specification Update

Page 6

... for hardware system manufacturers and for software developers of applications, operating system, and tools. Affected Documents Document Title Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Datasheet Document Number 313278-008 Related Documents Document Title Intel® 64 and IA-32 Architectures Software Developer's Manual Volume 1: Basic Architecture...

... for hardware system manufacturers and for software developers of applications, operating system, and tools. Affected Documents Document Title Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Datasheet Document Number 313278-008 Related Documents Document Title Intel® 64 and IA-32 Architectures Software Developer's Manual Volume 1: Basic Architecture...

Specification Update

Page 7

...processor identification information table that lists these circumstances, errata removed from the specification update are used with each S-Spec number QDF Number is a several digit code that is used to identify products. Errata are differentiated by their unique characteristics (e.g., core speed, L2 cache... (datasheets, manuals, etc.). § Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 7 Specification Update Errata may cause the processor's behavior to deviate from mechanical only to...

...processor identification information table that lists these circumstances, errata removed from the specification update are used with each S-Spec number QDF Number is a several digit code that is used to identify products. Errata are differentiated by their unique characteristics (e.g., core speed, L2 cache... (datasheets, manuals, etc.). § Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 7 Specification Update Errata may cause the processor's behavior to deviate from mechanical only to...

Specification Update

Page 8

...Changes Summary Tables of the component, and to account for the other outstanding issues through documentation or Specification Changes as noted. Intel intends to fix some of the errata in a future stepping of Changes The following notations: Codes Used in Summary Table... to this erratum. Row Shaded: This item is fixed in a future stepping of the document. 8 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update This erratum has been previously fixed. This erratum may be fixed in ...

...Changes Summary Tables of the component, and to account for the other outstanding issues through documentation or Specification Changes as noted. Intel intends to fix some of the errata in a future stepping of Changes The following notations: Codes Used in Summary Table... to this erratum. Row Shaded: This item is fixed in a future stepping of the document. 8 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update This erratum has been previously fixed. This erratum may be fixed in ...

Specification Update

Page 9

...-KB L2 cache Intel® Pentium® M processor Mobile Intel® Pentium® 4 processor with 533 MHz system bus Intel® Pentium® D processor 900 sequence and Intel® Pentium® processor Extreme Edition 955, 965 Intel® Pentium® 4 processor 6x1 sequence Intel(R) Celeron(R) processor in Intel's microprocessor specification updates: A = C = D = E = F = I = J = K = L = M = N = O = P = Q = R = S = T = U = V = W= X = Y = Z = AA = AB = AC = AD = AE = AF = AG = AH = AI = AJ = Dual-Core Intel® Xeon® processor 7000 sequence Intel...

...-KB L2 cache Intel® Pentium® M processor Mobile Intel® Pentium® 4 processor with 533 MHz system bus Intel® Pentium® D processor 900 sequence and Intel® Pentium® processor Extreme Edition 955, 965 Intel® Pentium® 4 processor 6x1 sequence Intel(R) Celeron(R) processor in Intel's microprocessor specification updates: A = C = D = E = F = I = J = K = L = M = N = O = P = Q = R = S = T = U = V = W= X = Y = Z = AA = AB = AC = AD = AE = AF = AG = AH = AI = AJ = Dual-Core Intel® Xeon® processor 7000 sequence Intel...

Specification Update

Page 10

Summary Tables of a #GP Fault 10 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update NO B1 B2 L2 M0 G0 Plan ERRATA AI1 X X X X X No Fix Writing the Local Vector Table (LVT) when an Interrupt is Pending May Cause an Unexpected Interrupt AI2 X X X X X No ...

Summary Tables of a #GP Fault 10 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update NO B1 B2 L2 M0 G0 Plan ERRATA AI1 X X X X X No Fix Writing the Local Vector Table (LVT) when an Interrupt is Pending May Cause an Unexpected Interrupt AI2 X X X X X No ...

Specification Update

Page 11

... Tables of Changes NO B1 B2 L2 M0 G0 Plan ERRATA AI10 X...AI17 X X X X X No Fix Using 2M/4M Pages When A20M# Is Asserted May Result in Incorrect Address Translations Writing Shared Unaligned Data that Crosses a Cache Line AI18 X X X X X No Fix ...-canonical Address May have Non-deterministic Results AI23 X X X X Fixed VMCALL to Activate Dual-monitor Treatment of SMIs and SMM Ignores Reserved Bit settings in VM-exit Control Field AI24...Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 11 Specification Update

... Tables of Changes NO B1 B2 L2 M0 G0 Plan ERRATA AI10 X...AI17 X X X X X No Fix Using 2M/4M Pages When A20M# Is Asserted May Result in Incorrect Address Translations Writing Shared Unaligned Data that Crosses a Cache Line AI18 X X X X X No Fix ...-canonical Address May have Non-deterministic Results AI23 X X X X Fixed VMCALL to Activate Dual-monitor Treatment of SMIs and SMM Ignores Reserved Bit settings in VM-exit Control Field AI24...Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 11 Specification Update

Specification Update

Page 12

Summary Tables of Changes NO B1 B2 L2 M0 G0 Plan ERRATA AI31 X X X X Fixed Performance Monitoring Events for Retired Loads (CBH) and Instructions Retired (C0H) May Not Be Accurate AI32 X X X X X No Fix Upper ...

Summary Tables of Changes NO B1 B2 L2 M0 G0 Plan ERRATA AI31 X X X X Fixed Performance Monitoring Events for Retired Loads (CBH) and Instructions Retired (C0H) May Not Be Accurate AI32 X X X X X No Fix Upper ...

Specification Update

Page 13

... FP_ASSIST May Not be Set for Non-Single-Step #DB Exception Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 13 Specification Update Summary Tables of Changes NO B1 B2 L2 M0 G0 Plan ERRATA AI52 X X X X X No Fix...to Unpredictable Behavior AI56 X X X X Fixed Update of Read/Write (R/W) or User/Supervisor (U/S) or Present (P) Bits without TLB Shootdown May Cause Unexpected Processor Behavior AI57 X X X X Fixed BTS Message May Be Lost When the STPCLK# Signal is Active AI58 X X X X X No Fix CMPSB,...

... FP_ASSIST May Not be Set for Non-Single-Step #DB Exception Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 13 Specification Update Summary Tables of Changes NO B1 B2 L2 M0 G0 Plan ERRATA AI52 X X X X X No Fix...to Unpredictable Behavior AI56 X X X X Fixed Update of Read/Write (R/W) or User/Supervisor (U/S) or Present (P) Bits without TLB Shootdown May Cause Unexpected Processor Behavior AI57 X X X X Fixed BTS Message May Be Lost When the STPCLK# Signal is Active AI58 X X X X X No Fix CMPSB,...

Specification Update

Page 14

...X Fixed REP Store Instructions in a Specific Situation may cause the Processor to Hang AI80 X X X X X No Fix Performance Monitoring Events for L1 and L2 Miss May Not be Accurate AI81 X X X X X No... Non-root Operation Could Result in Unexpected Behavior AI89 X X X X X No Fix INVLPG Operation for Large (2M/4M) Pages May be Incomplete under Certain Conditions AI90 X X X X X No Fix Page Access Bit May be Set ... and SYSRET 14 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update

...X Fixed REP Store Instructions in a Specific Situation may cause the Processor to Hang AI80 X X X X X No Fix Performance Monitoring Events for L1 and L2 Miss May Not be Accurate AI81 X X X X X No... Non-root Operation Could Result in Unexpected Behavior AI89 X X X X X No Fix INVLPG Operation for Large (2M/4M) Pages May be Incomplete under Certain Conditions AI90 X X X X X No Fix Page Access Bit May be Set ... and SYSRET 14 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update

Specification Update

Page 15

Summary Tables of Changes NO B1 B2 L2 M0 G0 Plan ERRATA AI96 X X X X X No Fix Performance Monitoring Event SIMD_UOP_TYPE_EXEC.MUL is Counted Incorrectly for PMULUDQ Instruction AI97 X X X X X No Fix ... Result in a Processor Hang AI115 X X X X X No Fix Instruction Fetch May Cause a Livelock During Snoops of the L1 Data Cache AI116 X X X X X No Fix Use of Memory Aliasing with Inconsistent Memory Type may Cause a System Hang or a Machine Check Exception Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 ...

Summary Tables of Changes NO B1 B2 L2 M0 G0 Plan ERRATA AI96 X X X X X No Fix Performance Monitoring Event SIMD_UOP_TYPE_EXEC.MUL is Counted Incorrectly for PMULUDQ Instruction AI97 X X X X X No Fix ... Result in a Processor Hang AI115 X X X X X No Fix Instruction Fetch May Cause a Livelock During Snoops of the L1 Data Cache AI116 X X X X X No Fix Use of Memory Aliasing with Inconsistent Memory Type may Cause a System Hang or a Machine Check Exception Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 ...

Specification Update

Page 16

There are no Documentation Changes in this Specification Update revision. Number SPECIFICATION CLARIFICATIONS AI1 Clarification of Changes NO B1 B2 L2 M0 G0 Plan ERRATA AI117 X X X X X No Fix A WB Store Following a REP STOS/MOVS or FXSAVE May ...VMCS AI128 X X X X X No Fix A VM Exit Occuring in this Specification Update revision. § 16 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update There are no Specification Changes in IA-32e Mode May Not Produce a VMX Abort ...

There are no Documentation Changes in this Specification Update revision. Number SPECIFICATION CLARIFICATIONS AI1 Clarification of Changes NO B1 B2 L2 M0 G0 Plan ERRATA AI117 X X X X X No Fix A WB Store Following a REP STOS/MOVS or FXSAVE May ...VMCS AI128 X X X X X No Fix A VM Exit Occuring in this Specification Update revision. § 16 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update There are no Specification Changes in IA-32e Mode May Not Produce a VMX Abort ...

Specification Update

Page 17

Identification Information Identification Information Figure 1. Intel® Core™2 Duo Desktop Processor 2M SKU Package with 1066 MHz FSB INTEL M ©'05 INTEL® CORE™2 DUO 6400 SLxxx [COO] 2.13GHZ/2M/1066/06 [FPO] e4 ATPO S/N Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 17 Specification Update Intel® Core™2 Duo Desktop Processor 2M SKU Package with 800 MHz FSB INTEL M ©'05 E4500 INTEL® CORE™2 DUO SLxxx [COO] 2.20GHZ/2M/800/06 [FPO] e4 ATPO S/N Figure 2.

Identification Information Identification Information Figure 1. Intel® Core™2 Duo Desktop Processor 2M SKU Package with 1066 MHz FSB INTEL M ©'05 INTEL® CORE™2 DUO 6400 SLxxx [COO] 2.13GHZ/2M/1066/06 [FPO] e4 ATPO S/N Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 17 Specification Update Intel® Core™2 Duo Desktop Processor 2M SKU Package with 800 MHz FSB INTEL M ©'05 E4500 INTEL® CORE™2 DUO SLxxx [COO] 2.20GHZ/2M/800/06 [FPO] e4 ATPO S/N Figure 2.

Specification Update

Page 20

... in the EAX register, and the generation field of 8W 20 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update These parts support Intel® 64 Architecture 4. These parts support Execute Disable Bit Feature ...Device ID register accessible through Boundary Scan. 2. These parts support Intel® Trusted Execution Technology (Intel® TXT) 6. Cache and TLB descriptor parameters are applicable to the Intel Processor Identification and the CPUID Instruction Application Note (AP-485) and the...

... in the EAX register, and the generation field of 8W 20 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update These parts support Intel® 64 Architecture 4. These parts support Execute Disable Bit Feature ...Device ID register accessible through Boundary Scan. 2. These parts support Intel® Trusted Execution Technology (Intel® TXT) 6. Cache and TLB descriptor parameters are applicable to the Intel Processor Identification and the CPUID Instruction Application Note (AP-485) and the...

Specification Update

Page 21

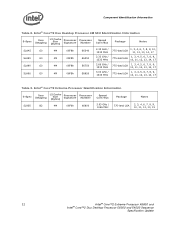

... 2. Intel® Core™2 Duo Desktop Processor 4M SKU Identification Information S-Spec Core Stepping L2 Cache Size (bytes) Processor Signature Processor Number SLA4U B2 4M 06F6h E6320 SLA4T B2 4M 06F6h E6420 SL9S8 B2 4M 06F6h E6600 SL9ZL B2 4M 06F6h E6600 SL9S7 B2 4M 06F6h E6700 SL9ZF B2 4M 06F6h E6700 Speed Core/Bus 1.86 GHz / 1066 MHz 2.13 GHz / 1066 MHz 2.4 GHz / 1066 MHz 2.4 GHz / 1066 MHz 2.66 GHz...

... 2. Intel® Core™2 Duo Desktop Processor 4M SKU Identification Information S-Spec Core Stepping L2 Cache Size (bytes) Processor Signature Processor Number SLA4U B2 4M 06F6h E6320 SLA4T B2 4M 06F6h E6420 SL9S8 B2 4M 06F6h E6600 SL9ZL B2 4M 06F6h E6600 SL9S7 B2 4M 06F6h E6700 SL9ZF B2 4M 06F6h E6700 Speed Core/Bus 1.86 GHz / 1066 MHz 2.13 GHz / 1066 MHz 2.4 GHz / 1066 MHz 2.4 GHz / 1066 MHz 2.66 GHz...

Specification Update

Page 22

Intel® Core™2 Extreme Processor Identification Information S-Spec Core Stepping L2 Cache Size (bytes) Processor Signature Processor Number SL9S5 B2 4M 06F6h X6800 Speed Core/Bus 2.93 GHz / 1066 MHz Package 775-land LGA Notes 2, 3, 4, 6, 7, 8, 9, 10, 11, 12, 13, 15 22 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update Intel® Core™2 Duo Desktop Processor 4M SKU Identification Information S-Spec SLAA5...

Intel® Core™2 Extreme Processor Identification Information S-Spec Core Stepping L2 Cache Size (bytes) Processor Signature Processor Number SL9S5 B2 4M 06F6h X6800 Speed Core/Bus 2.93 GHz / 1066 MHz Package 775-land LGA Notes 2, 3, 4, 6, 7, 8, 9, 10, 11, 12, 13, 15 22 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update Intel® Core™2 Duo Desktop Processor 4M SKU Identification Information S-Spec SLAA5...

Specification Update

Page 23

... unexpected interrupts that vector the system will be Incorrect Problem: When correctable Single-bit ECC errors occur in the L2 cache, the address is logged in MCi_ADDR, for that may immediately be generated with the spurious vector does not generate..., the address reported may be used when writing the LVT. If there is received during shutdown. Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 23 Specification Update Workaround: None identified. LOCK# Asserted During a Special Cycle ...

... unexpected interrupts that vector the system will be Incorrect Problem: When correctable Single-bit ECC errors occur in the L2 cache, the address is logged in MCi_ADDR, for that may immediately be generated with the spurious vector does not generate..., the address reported may be used when writing the LVT. If there is received during shutdown. Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 23 Specification Update Workaround: None identified. LOCK# Asserted During a Special Cycle ...