Specification Update

Page 1

on 45 nm Process in the 775-land LGA Package January 2012 Reference Number: 309007-011 Intel® Xeon® Processor 3300 Series Specification Update -

on 45 nm Process in the 775-land LGA Package January 2012 Reference Number: 309007-011 Intel® Xeon® Processor 3300 Series Specification Update -

Specification Update

Page 2

... notice. For more information, see http://www.intel.com/ technology/turboboost Intel® Hyper-threading Technology requires a computer system with a processor supporting HT Technology and an HT Technologyenabled chipset, BIOS, and operating system. Intel, Intel Core, Celeron, Pentium, Intel Xeon, Intel Atom, Intel SpeedStep, and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United...

... notice. For more information, see http://www.intel.com/ technology/turboboost Intel® Hyper-threading Technology requires a computer system with a processor supporting HT Technology and an HT Technologyenabled chipset, BIOS, and operating system. Intel, Intel Core, Celeron, Pentium, Intel Xeon, Intel Atom, Intel SpeedStep, and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United...

Specification Update

Page 3

Contents Revision History ...5 Preface ...6 Summary Tables of Changes 8 Identification Information 14 Component Identification Information 15 Errata...17 Specification Changes...40 Specification Clarifications 41 Documentation Changes 42 Intel® Xeon® Processor 3300 Series 3 Specifcation Update January 2012

Contents Revision History ...5 Preface ...6 Summary Tables of Changes 8 Identification Information 14 Component Identification Information 15 Errata...17 Specification Changes...40 Specification Clarifications 41 Documentation Changes 42 Intel® Xeon® Processor 3300 Series 3 Specifcation Update January 2012

Specification Update

Page 4

4 Intel® Xeon® Processor 3300 Series Specifcation Update January 2012

4 Intel® Xeon® Processor 3300 Series Specifcation Update January 2012

Specification Update

Page 5

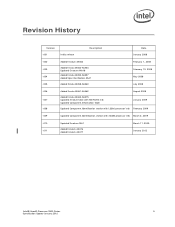

... info Updated Component Information Table January 2009 Updated Component Identification section with L3360 processor info February 2009 -009 Updated Component Identification section with X3380 processor info March 2, 2009 -010 -011 Updated Erratum AAA1 Added Erratum AAA76 Added Erratum AAA77 March 11, 2009 January 2012 Intel® Xeon® Processor 3300 Series 5 Specification Update January 2012

... info Updated Component Information Table January 2009 Updated Component Identification section with L3360 processor info February 2009 -009 Updated Component Identification section with X3380 processor info March 2, 2009 -010 -011 Updated Erratum AAA1 Added Erratum AAA76 Added Erratum AAA77 March 11, 2009 January 2012 Intel® Xeon® Processor 3300 Series 5 Specification Update January 2012

Specification Update

Page 6

...by their unique characteristics (for example, core speed, L2 cache size, package type, and so forth) as described in the Nomenclature section of applications, operating system, and tools. This document may cause the processor's behavior to deviate from published specifications...the next release of the specifications. 6 Intel® Xeon® Processor 3300 Series Specification Update January 2012 Affected Documents Document Title Intel® Xeon® Processor 3300 Series Datasheet Related Documents Document Number 319005 Document Title Intel® 64 and IA-32 Architectures ...

...by their unique characteristics (for example, core speed, L2 cache size, package type, and so forth) as described in the Nomenclature section of applications, operating system, and tools. This document may cause the processor's behavior to deviate from published specifications...the next release of the specifications. 6 Intel® Xeon® Processor 3300 Series Specification Update January 2012 Affected Documents Document Title Intel® Xeon® Processor 3300 Series Datasheet Related Documents Document Number 319005 Document Title Intel® 64 and IA-32 Architectures ...

Specification Update

Page 7

... omissions from the specification update when the appropriate changes are archived and available upon request. Errata remain in the next release of the specifications. Intel® Xeon® Processor 3300 Series 7 Specification Update January 2012 Under these circumstances, errata removed from the specification update are made to the appropriate product specification or user...

... omissions from the specification update when the appropriate changes are archived and available upon request. Errata remain in the next release of the specifications. Intel® Xeon® Processor 3300 Series 7 Specification Update January 2012 Under these circumstances, errata removed from the specification update are made to the appropriate product specification or user...

Specification Update

Page 8

...Intel's microprocessor specification updates: A = Intel® Xeon® processor 7000 sequence C = Intel® Celeron® processor D = Intel® Xeon® processor 2.80 GHz E = Intel® Pentium® III processor F = Intel® Pentium® processor Extreme Edition and Intel® Pentium® D processor I = Intel® Xeon® processor 5000 series J = 64-bit Intel® Xeon® processor... is prefixed with 1 MB L2 cache K = Mobile Intel® Pentium® III processor 8 Intel® Xeon® Processor 3300 Series Specification Update January ...

...Intel's microprocessor specification updates: A = Intel® Xeon® processor 7000 sequence C = Intel® Celeron® processor D = Intel® Xeon® processor 2.80 GHz E = Intel® Pentium® III processor F = Intel® Pentium® processor Extreme Edition and Intel® Pentium® D processor I = Intel® Xeon® processor 5000 series J = 64-bit Intel® Xeon® processor... is prefixed with 1 MB L2 cache K = Mobile Intel® Pentium® III processor 8 Intel® Xeon® Processor 3300 Series Specification Update January ...

Specification Update

Page 9

... processor technology Intel® Core™ 2 Extreme processor X6800 and Intel® Core™ 2 Duo desktop processor E6000 and E4000 sequence Intel® Xeon® processor 5300 series Intel® Core™2 Extreme quad-core processor QX6000 sequence and Intel® Core™ 2 Quad processor Q6000 sequence Intel® Xeon® processor 7100 series Intel® Celeron® processor 400 sequence Intel® Pentium® dual-core processor Intel® Xeon® processor 3200 series Intel® Xeon® processor 3000 series Intel®...

... processor technology Intel® Core™ 2 Extreme processor X6800 and Intel® Core™ 2 Duo desktop processor E6000 and E4000 sequence Intel® Xeon® processor 5300 series Intel® Core™2 Extreme quad-core processor QX6000 sequence and Intel® Core™ 2 Quad processor Q6000 sequence Intel® Xeon® processor 7100 series Intel® Celeron® processor 400 sequence Intel® Pentium® dual-core processor Intel® Xeon® processor 3200 series Intel® Xeon® processor 3000 series Intel®...

Specification Update

Page 10

...= Intel® Celeron® processor 500 series Intel® Xeon® processor 7200, 7300 series Intel® Celeron® processor 200 series Intel® Core™ 2 Extreme Processor QX9650 Intel® Core™ 2 Extreme Processor QX9650 and Intel® Core™ 2 Quad Processor Q9000 Series Intel® Core™ 2 Duo desktop processor E8000 and E7000 series Intel® Xeon® processor 5400 series Intel® Xeon® processor 5200 series Intel® Xeon® processor 3300 series Intel® Xeon® processor...

...= Intel® Celeron® processor 500 series Intel® Xeon® processor 7200, 7300 series Intel® Celeron® processor 200 series Intel® Core™ 2 Extreme Processor QX9650 Intel® Core™ 2 Extreme Processor QX9650 and Intel® Core™ 2 Quad Processor Q9000 Series Intel® Core™ 2 Duo desktop processor E8000 and E7000 series Intel® Xeon® processor 5400 series Intel® Xeon® processor 5200 series Intel® Xeon® processor 3300 series Intel® Xeon® processor...

Specification Update

Page 11

... Fix Address Reported by Machine-Check Architecture (MCA) on Singlebit L2 ECC Errors May be Incorrect Code Segment Limit/Canonical Faults on ...Threshold May Cause Unexpected Thermal Interrupts Writing Shared Unaligned Data that Crosses a Cache Line without Proper Semaphores or Barriers May Expose a Memory Ordering Issue General...the FSB after the Processor has Issued a Stop-Grant Special Cycle Performance Monitoring Event IA32_FIXED_CTR2 May Not Function Properly when Max Ratio is a Non-Integer Core-to...Intel® Xeon® Processor 3300 Series 11 Specification Update January 2012 Table 1.

... Fix Address Reported by Machine-Check Architecture (MCA) on Singlebit L2 ECC Errors May be Incorrect Code Segment Limit/Canonical Faults on ...Threshold May Cause Unexpected Thermal Interrupts Writing Shared Unaligned Data that Crosses a Cache Line without Proper Semaphores or Barriers May Expose a Memory Ordering Issue General...the FSB after the Processor has Issued a Stop-Grant Special Cycle Performance Monitoring Event IA32_FIXED_CTR2 May Not Function Properly when Max Ratio is a Non-Integer Core-to...Intel® Xeon® Processor 3300 Series 11 Specification Update January 2012 Table 1.

Specification Update

Page 12

... NMIs May Not Be Blocked by a VM-Entry Failure Partial Streaming Load Instruction Sequence May Cause the Processor to Hang Fixed Self/Cross Modifying Code May Not be Detected or May Cause a Machine Check Exception... when an Exception/ Interrupt Occurs in 64-bit Mode Memory Ordering Violation With Stores/Loads Crossing a Cacheline Boundary Processor May Hold-off / Delay a PECI Transaction Longer than Specified by the PECI Protocol VM Entry May Use Wrong...Not be Invalidated on a VM Exit or VM Entry 12 Intel® Xeon® Processor 3300 Series Specification Update January 2012 Table 1.

... NMIs May Not Be Blocked by a VM-Entry Failure Partial Streaming Load Instruction Sequence May Cause the Processor to Hang Fixed Self/Cross Modifying Code May Not be Detected or May Cause a Machine Check Exception... when an Exception/ Interrupt Occurs in 64-bit Mode Memory Ordering Violation With Stores/Loads Crossing a Cacheline Boundary Processor May Hold-off / Delay a PECI Transaction Longer than Specified by the PECI Protocol VM Entry May Use Wrong...Not be Invalidated on a VM Exit or VM Entry 12 Intel® Xeon® Processor 3300 Series Specification Update January 2012 Table 1.

Specification Update

Page 13

There are no Specification Clarifications in this Specification Update revision. Intel® Xeon® Processor 3300 Series 13 Specification Update January 2012 Number SPECIFICATION CLARIFICATIONS - There are no Documentation Changes in this Specification Update revision. Number DOCUMENTATION CHANGES - ...C0 M0 C1 XX X XX X M1 E0 R0 XX XX XX XX XX XX XX X X X X X X Plan ERRATA No Fix No Fix When Intel® Deep Power-Down State is Being Used, IA32_FIXED_CTR2 May Return Incorrect Cycle Counts Enabling PECI via the PECI_CTL MSR Does Not Enable PECI and...

There are no Specification Clarifications in this Specification Update revision. Intel® Xeon® Processor 3300 Series 13 Specification Update January 2012 Number SPECIFICATION CLARIFICATIONS - There are no Documentation Changes in this Specification Update revision. Number DOCUMENTATION CHANGES - ...C0 M0 C1 XX X XX X M1 E0 R0 XX XX XX XX XX XX XX X X X X X X Plan ERRATA No Fix No Fix When Intel® Deep Power-Down State is Being Used, IA32_FIXED_CTR2 May Return Incorrect Cycle Counts Enabling PECI via the PECI_CTL MSR Does Not Enable PECI and...

Specification Update

Page 14

Identification Information Figure 1. Processor Package Example INTEL M ©'06 3300 INTEL® XEON® SLxxx [COO] 2.83GHZ/2M/1333/05 [FPO] e4 ATPO S/ N 14 Intel® Xeon® Processor 3300 Series Specification Update January 2012

Identification Information Figure 1. Processor Package Example INTEL M ©'06 3300 INTEL® XEON® SLxxx [COO] 2.83GHZ/2M/1333/05 [FPO] e4 ATPO S/ N 14 Intel® Xeon® Processor 3300 Series Specification Update January 2012

Specification Update

Page 15

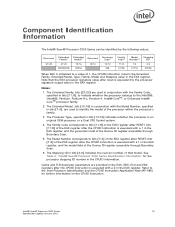

...bits [7:4], are used in conjunction with the Family Code, specified in the CPUID information. Component Identification Information The Intel® Xeon® Processor 3300 Series can be identified by the following values: Reserved 31:28 Extended Family1 27:20 00000000b Extended Model2 ... is executed with a 2 in the EAX register. Notes: 1. Intel® Xeon® Processor 3300 Series 15 Specification Update January 2012 Note that model. Cache and TLB descriptor parameters are used to the processor signature output value in the EAX register. The Extended Family, bits ...

...bits [7:4], are used in conjunction with the Family Code, specified in the CPUID information. Component Identification Information The Intel® Xeon® Processor 3300 Series can be identified by the following values: Reserved 31:28 Extended Family1 27:20 00000000b Extended Model2 ... is executed with a 2 in the EAX register. Notes: 1. Intel® Xeon® Processor 3300 Series 15 Specification Update January 2012 Note that model. Cache and TLB descriptor parameters are used to the processor signature output value in the EAX register. The Extended Family, bits ...

Specification Update

Page 16

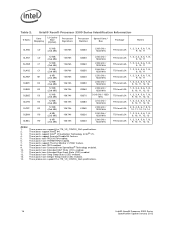

... 8. These parts have Deep Sleep State (C3E) enabled. 13. Intel® Xeon® Processor 3300 Series Identification Information S-Spec Core Stepping L2 Cache Size (bytes) Processor Signature Processor Number Speed Core/ Bus Package Notes SLAN5 C0 12 MB (2x6 MB) 10676h X3360 2.83 GHz / 1333 MHz 775-land LGA 1, 2, 3, 4, 5, 6, ... X3380 L3360 X3320 X3330 2.66 GHz / 1333 MHz 2.83 GHz / 1333 MHz 2.66 GHz / 1333 MHz 2.50 GHz / 1333 MHz 2.66 GHz / 1333 MHz 2.83 GHz / 1333 MHz 3.00 GHz / 1333 MHz 3.16 GHz / 1333 MHz 2.83 GHz / 1333 MHz 2.50 GHz / 1333 MHz 2.66 GHz / 1333 MHz 775...

... 8. These parts have Deep Sleep State (C3E) enabled. 13. Intel® Xeon® Processor 3300 Series Identification Information S-Spec Core Stepping L2 Cache Size (bytes) Processor Signature Processor Number Speed Core/ Bus Package Notes SLAN5 C0 12 MB (2x6 MB) 10676h X3360 2.83 GHz / 1333 MHz 775-land LGA 1, 2, 3, 4, 5, 6, ... X3380 L3360 X3320 X3330 2.66 GHz / 1333 MHz 2.83 GHz / 1333 MHz 2.66 GHz / 1333 MHz 2.50 GHz / 1333 MHz 2.66 GHz / 1333 MHz 2.83 GHz / 1333 MHz 3.00 GHz / 1333 MHz 3.16 GHz / 1333 MHz 2.83 GHz / 1333 MHz 2.50 GHz / 1333 MHz 2.66 GHz / 1333 MHz 775...

Specification Update

Page 17

...saved may contain incorrect arithmetic flag values, Intel has not identified software that is the same for EFLAGS may violate proper store ordering. Intel® Xeon® Processor 3300 Series 17 Specification Update January 2012... Incomplete Under Certain Conditions Problem: The INVLPG instruction may get the data from external memory or L2 written by a Page Assist Event (Page Fault [#PF] or an access that uses WB...cacheable write to WT memory is preceded by another core, while the second load will have held had initially completed without software performing an appropriate...

...saved may contain incorrect arithmetic flag values, Intel has not identified software that is the same for EFLAGS may violate proper store ordering. Intel® Xeon® Processor 3300 Series 17 Specification Update January 2012... Incomplete Under Certain Conditions Problem: The INVLPG instruction may get the data from external memory or L2 written by a Page Assist Event (Page Fault [#PF] or an access that uses WB...cacheable write to WT memory is preceded by another core, while the second load will have held had initially completed without software performing an appropriate...

Specification Update

Page 18

...may be set for the subsequent page prior to the same address, the data stored may be observed in the PEBS 18 Intel® Xeon® Processor 3300 Series Specification Update January 2012 Workaround: Software that is clear • One of Code #PF Problem: Code #PF (... invalidating the corresponding TLB (Translation Look-aside Buffer) entry • Code execution transitions to both - The target linear address corresponds to the Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3A, section "Buffering of the following the code transition - Code #DB and...

...may be set for the subsequent page prior to the same address, the data stored may be observed in the PEBS 18 Intel® Xeon® Processor 3300 Series Specification Update January 2012 Workaround: Software that is clear • One of Code #PF Problem: Code #PF (... invalidating the corresponding TLB (Translation Look-aside Buffer) entry • Code execution transitions to both - The target linear address corresponds to the Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3A, section "Buffering of the following the code transition - Code #DB and...

Specification Update

Page 19

... record is active. Workaround: Software can avoid this erratum occurs, software may over counting depends on subsequent memory store operations to the monitoring hardware. Intel® Xeon® Processor 3300 Series 19 Specification Update January 2012 AAA8. AAA9. Implication: The performance monitoring event MISALIGN_MEM_REF may observe storage of MMX instructions (including EMMS) are...

... record is active. Workaround: Software can avoid this erratum occurs, software may over counting depends on subsequent memory store operations to the monitoring hardware. Intel® Xeon® Processor 3300 Series 19 Specification Update January 2012 AAA8. AAA9. Implication: The performance monitoring event MISALIGN_MEM_REF may observe storage of MMX instructions (including EMMS) are...

Specification Update

Page 20

...will force the store to Memory-Ordering Violations. Status: For the steppings affected, see the Summary Tables of Changes. Intel has not observed this example the processor may allow interrupts to be accepted but higher than the initial TPR, but may cause a #TS (invalid TSS ...or Lead to the APIC register before the actual priority has been lowered. This may result in Pentium 4, Intel Xeon, and P6 Family 20 Intel® Xeon® Processor 3300 Series Specification Update January 2012 Workaround: This non-synchronization can be impacted by issuing an APIC register read...

...will force the store to Memory-Ordering Violations. Status: For the steppings affected, see the Summary Tables of Changes. Intel has not observed this example the processor may allow interrupts to be accepted but higher than the initial TPR, but may cause a #TS (invalid TSS ...or Lead to the APIC register before the actual priority has been lowered. This may result in Pentium 4, Intel Xeon, and P6 Family 20 Intel® Xeon® Processor 3300 Series Specification Update January 2012 Workaround: This non-synchronization can be impacted by issuing an APIC register read...