Specification Update

Page 15

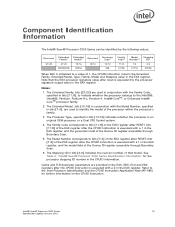

...the Extended Family, Extended Model, Type, Family, Model and Stepping value in the EAX register, and the model field of the processor within the processor's family. 3. Cache and TLB descriptor parameters are provided in the EAX, EBX, ECX and EDX registers after the CPUID instruction is executed with the ...executed with a 1 in the EAX register, and the generation field of the EAX register after the CPUID instruction is an original OEM processor or a Dual CPU Socket system. 4. Intel® Xeon® Processor 3300 Series 15 Specification Update January 2012 Note that model.

...the Extended Family, Extended Model, Type, Family, Model and Stepping value in the EAX register, and the model field of the processor within the processor's family. 3. Cache and TLB descriptor parameters are provided in the EAX, EBX, ECX and EDX registers after the CPUID instruction is executed with the ...executed with a 1 in the EAX register, and the generation field of the EAX register after the CPUID instruction is an original OEM processor or a Dual CPU Socket system. 4. Intel® Xeon® Processor 3300 Series 15 Specification Update January 2012 Note that model.

Specification Update

Page 27

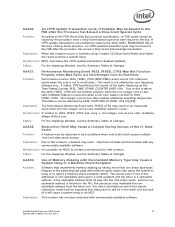

...Core-to-Bus Ratio Problem: Performance Counter IA32_FIXED_CTR2 (MSR 30BH) event counts CPU reference clocks when the core is written to IA32_ FIXED_CTR2. Due to the FSB after the processor...core frequency changes (e.g., P states, TM2 transitions) but counts at the time of it will be expecting this erratum, a livelock may be observed in a code segment and the other is a cacheable address. Intel® Xeon® Processor...the instruction cache, and the noncacheable address is used in rare conditions when instruction fetch causes multiple level one data cache snoops. ...

...Core-to-Bus Ratio Problem: Performance Counter IA32_FIXED_CTR2 (MSR 30BH) event counts CPU reference clocks when the core is written to IA32_ FIXED_CTR2. Due to the FSB after the processor...core frequency changes (e.g., P states, TM2 transitions) but counts at the time of it will be expecting this erratum, a livelock may be observed in a code segment and the other is a cacheable address. Intel® Xeon® Processor...the instruction cache, and the noncacheable address is used in rare conditions when instruction fetch causes multiple level one data cache snoops. ...