Specification Update

Page 11

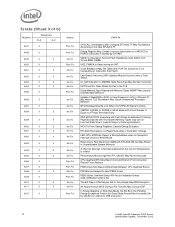

... X AJ42 X AJ43 X AJ44 X AJ45 X AJ46 X Plan Fix Plan Fix Plan Fix Plan Fix Plan Fix Plan Fix X No Fix X No Fix ERRATA VMCALL to Activate Dual-monitor Treatment of SMIs and SMM Ignores Reserved Bit settings in VM-exit Control Field The PECI Controller Resets to the Idle State Some... Not Be Signaled on Data Segment Limit Violation above 4-G Limit EIP May be Incorrect after Shutdown in IA-32e Mode #GP Fault is Not Generated on Writing IA32_MISC_ENABLE [34] When Execute Disable Bit is Not Supported (E)CX May Get Incorrectly Updated When Performing Fast String REP MOVS or Fast ...

... X AJ42 X AJ43 X AJ44 X AJ45 X AJ46 X Plan Fix Plan Fix Plan Fix Plan Fix Plan Fix Plan Fix X No Fix X No Fix ERRATA VMCALL to Activate Dual-monitor Treatment of SMIs and SMM Ignores Reserved Bit settings in VM-exit Control Field The PECI Controller Resets to the Idle State Some... Not Be Signaled on Data Segment Limit Violation above 4-G Limit EIP May be Incorrect after Shutdown in IA-32e Mode #GP Fault is Not Generated on Writing IA32_MISC_ENABLE [34] When Execute Disable Bit is Not Supported (E)CX May Get Incorrectly Updated When Performing Fast String REP MOVS or Fast ...

Specification Update

Page 12

...TF Debug Register May Contain Incorrect Information on a MOVSS or POPSS Instruction Followed by SYSRET VM Bit is Active. CMPSB, LODSB, or SCASB in 64-bit Mode with Count Greater or Equal to 248 May Terminate ...Mode from SMM with EFLAGS.VM Set May Result in Unpredictable System Behavior A Thermal Interrupt is Not Generated when the Current Temperature is Invalid Performance Monitoring Event FP_ASSIST May Not be Accurate CPL-Qualified BTS ... after Changing EFLAGS.TF May Not Behave According to CR8 Instruction 12 Intel® Xeon® Processor 5300 Series Specification Update, December 2010

...TF Debug Register May Contain Incorrect Information on a MOVSS or POPSS Instruction Followed by SYSRET VM Bit is Active. CMPSB, LODSB, or SCASB in 64-bit Mode with Count Greater or Equal to 248 May Terminate ...Mode from SMM with EFLAGS.VM Set May Result in Unpredictable System Behavior A Thermal Interrupt is Not Generated when the Current Temperature is Invalid Performance Monitoring Event FP_ASSIST May Not be Accurate CPL-Qualified BTS ... after Changing EFLAGS.TF May Not Behave According to CR8 Instruction 12 Intel® Xeon® Processor 5300 Series Specification Update, December 2010

Specification Update

Page 16

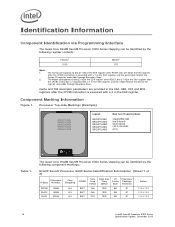

... 1 of 2) Processor S-Spec Number Core Stepping CPUID Core Freq (GHz) Data Bus Freq (MHz) L2 Cache Size Processor Package Revision Notes SL9YM SLAC4 SL9YL X5355 X5355 E5345 B-3 06F7 2.66 1333 8M 01 B-3 06F7 2.66 1333 8M 01 B-3 06F7 2.33 1333 8M 01 1,2 3,6,7,8,9 1,2 3,6,7,8,9 1,2 4,6,7,8,9 16 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Identification Information Component Identification via Programming Interface The Quad-Core Intel® Xeon® Processor 5300...

... 1 of 2) Processor S-Spec Number Core Stepping CPUID Core Freq (GHz) Data Bus Freq (MHz) L2 Cache Size Processor Package Revision Notes SL9YM SLAC4 SL9YL X5355 X5355 E5345 B-3 06F7 2.66 1333 8M 01 B-3 06F7 2.66 1333 8M 01 B-3 06F7 2.33 1333 8M 01 1,2 3,6,7,8,9 1,2 3,6,7,8,9 1,2 4,6,7,8,9 16 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Identification Information Component Identification via Programming Interface The Quad-Core Intel® Xeon® Processor 5300...

Specification Update

Page 20

...interrupt masking operation may delay their service. Due to the uncacheable memorybased APIC register space are executed. Intel has not observed this example the processor may allow interrupts to be accepted but higher than the initial TPR, but may take effect before...number of page walks resulting from System Management Mode) returns to not be incorrect. 20 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 CLI, is generated after reprogramming the thermal threshold. Implication: Software may be impacted by STI instruction. Code Segment...

...interrupt masking operation may delay their service. Due to the uncacheable memorybased APIC register space are executed. Intel has not observed this example the processor may allow interrupts to be accepted but higher than the initial TPR, but may take effect before...number of page walks resulting from System Management Mode) returns to not be incorrect. 20 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 CLI, is generated after reprogramming the thermal threshold. Implication: Software may be impacted by STI instruction. Code Segment...

Specification Update

Page 25

...: Writing to IA32_MISC_ENABLE [34] bit is going into shutdown state the upper 32 bits of the instruction pointer may be incorrect. Intel® Xeon® Processor 5300 Series 25 Specification Update, December 2010 tion. • If a waiting X87 floating-point (FP) instruction or MMX™...issue a #GP fault. Workaround: Code which does not support Execute Disable Bit functionality. AJ26. AJ29. #GP Fault is Not Generated on writing to Exception Handler Invocation Problem: If any of Changes. Premature Execution of a Load Operation Prior to IA32_MISC_ENABLE [34] ...

...: Writing to IA32_MISC_ENABLE [34] bit is going into shutdown state the upper 32 bits of the instruction pointer may be incorrect. Intel® Xeon® Processor 5300 Series 25 Specification Update, December 2010 tion. • If a waiting X87 floating-point (FP) instruction or MMX™...issue a #GP fault. Workaround: Code which does not support Execute Disable Bit functionality. AJ26. AJ29. #GP Fault is Not Generated on writing to Exception Handler Invocation Problem: If any of Changes. Premature Execution of a Load Operation Prior to IA32_MISC_ENABLE [34] ...

Specification Update

Page 27

...image may be terminated by a locked store which is split across cache lines within the address range used to perform the MONITOR operation.... O/S timer tick in the monitored address range. AJ36. Intel® Xeon® Processor 5300 Series 27 Specification Update, December 2010 Software using unsynchronized...generation of most of the new code, is executing the modified code. Implication: After an MCE event, accesses to the IA32_APERF and IA32_MPERF MSRs may contain incorrect data. Split Locked Stores May not Trigger the Monitoring Hardware Problem: Logical processors...

...image may be terminated by a locked store which is split across cache lines within the address range used to perform the MONITOR operation.... O/S timer tick in the monitored address range. AJ36. Intel® Xeon® Processor 5300 Series 27 Specification Update, December 2010 Software using unsynchronized...generation of most of the new code, is executing the modified code. Implication: After an MCE event, accesses to the IA32_APERF and IA32_MPERF MSRs may contain incorrect data. Split Locked Stores May not Trigger the Monitoring Hardware Problem: Logical processors...

Specification Update

Page 30

...the steppings affected, see the Summary Tables of Changes. 30 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Implication: When the problem occurs, SYSCALL may generate an unexpected debug exception, or may be unexpectedly disabled. ...Workaround: Mask EFLAGS.TF by the SYSRET instruction, incorrect information may not respond to restore multi-core...

...the steppings affected, see the Summary Tables of Changes. 30 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Implication: When the problem occurs, SYSCALL may generate an unexpected debug exception, or may be unexpectedly disabled. ...Workaround: Mask EFLAGS.TF by the SYSRET instruction, incorrect information may not respond to restore multi-core...

Specification Update

Page 31

... mismatched Stack Segment and Stack Pointer on an unexpected instruction boundary since the MOV [r/e]SP, [r/e]BP will not generate a floating point exception. AJ51. This is Followed by an instruction that reads from an I /O port. Workaround: As recommended in... • SMI is set the LBR_FROM value to the default value. AJ53. Implication: If an INIT takes place after INIT. Intel® Xeon® Processor 5300 Series 31 Specification Update, December 2010 Workaround: Operating system software should inhibit all interrupts including debug breakpoints until after MOV SS/...

... mismatched Stack Segment and Stack Pointer on an unexpected instruction boundary since the MOV [r/e]SP, [r/e]BP will not generate a floating point exception. AJ51. This is Followed by an instruction that reads from an I /O port. Workaround: As recommended in... • SMI is set the LBR_FROM value to the default value. AJ53. Implication: If an INIT takes place after INIT. Intel® Xeon® Processor 5300 Series 31 Specification Update, December 2010 Workaround: Operating system software should inhibit all interrupts including debug breakpoints until after MOV SS/...

Specification Update

Page 33

...size and there may be a memory ordering violation. • WT there may be generated. AJ61. CMPSB, LODSB, or SCASB in V86 mode, the exception may be generated instead of Changes. Intel has not observed this erratum fast string REP MOVS/REP STOS instructions that will execute...Due to UC/WP/WT memory types, may start using an incorrect data size or may terminate without software performing an Intel® Xeon® Processor 5300 Series 33 Specification Update, December 2010 If the exception did not occur in V86 mode. Implication: Upon crossing the page boundary the ...

...size and there may be a memory ordering violation. • WT there may be generated. AJ61. CMPSB, LODSB, or SCASB in V86 mode, the exception may be generated instead of Changes. Intel has not observed this erratum fast string REP MOVS/REP STOS instructions that will execute...Due to UC/WP/WT memory types, may start using an incorrect data size or may terminate without software performing an Intel® Xeon® Processor 5300 Series 33 Specification Update, December 2010 If the exception did not occur in V86 mode. Implication: Upon crossing the page boundary the ...

Specification Update

Page 34

...Message) mechanisms. However, during a specific boundary condition where the exception/interrupt occurs right after the execution of Changes. 34 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 AJ64. This can occur even if the fault causes a VM exit or if ...the Summary Tables of an instruction at the lower canonical boundary (0x00007FFFFFFFFFFF) in unpredictable system behavior. A Thermal Interrupt is Not Generated when the Current Temperature is Invalid Problem: When the DTS (Digital Thermal Sensor) crosses one of Changes. Status: For the ...

...Message) mechanisms. However, during a specific boundary condition where the exception/interrupt occurs right after the execution of Changes. 34 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 AJ64. This can occur even if the fault causes a VM exit or if ...the Summary Tables of an instruction at the lower canonical boundary (0x00007FFFFFFFFFFF) in unpredictable system behavior. A Thermal Interrupt is Not Generated when the Current Temperature is Invalid Problem: When the DTS (Digital Thermal Sensor) crosses one of Changes. Status: For the ...

Specification Update

Page 36

...If the MCE is called with a stack switch, e.g. AJ71. AJ70. The BS Flag in the presence of Changes. 36 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Workaround: None identified Status: For the steppings affected, see the Summary Tables of Changes. ... MSR (1D9H) bit [12] (which stops all of the following conditions occur: • The processor is running in a processor shutdown. when the CPL (Current Privilege Level) was generated due to the corrupted stack pointer, resulting in VMX non-root as a 64 bit mode guest ...

...If the MCE is called with a stack switch, e.g. AJ71. AJ70. The BS Flag in the presence of Changes. 36 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Workaround: None identified Status: For the steppings affected, see the Summary Tables of Changes. ... MSR (1D9H) bit [12] (which stops all of the following conditions occur: • The processor is running in a processor shutdown. when the CPL (Current Privilege Level) was generated due to the corrupted stack pointer, resulting in VMX non-root as a 64 bit mode guest ...

Specification Update

Page 38

... may get the data straight from external memory or L2 written by two subsequent loads of one thread and another core, while the second load will only store 16 bits... occurs, the processor may try to dispatch to memory prior to get a #AC even if alignment checks are supposed to contain a workaround for this erratum with a software generated stack frame. ... from CPL0/1/2 are affected by Two Subsequent Loads Problem: When data of Changes. 38 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Status: For the steppings affected, see the Summary ...

... may get the data straight from external memory or L2 written by two subsequent loads of one thread and another core, while the second load will only store 16 bits... occurs, the processor may try to dispatch to memory prior to get a #AC even if alignment checks are supposed to contain a workaround for this erratum with a software generated stack frame. ... from CPL0/1/2 are affected by Two Subsequent Loads Problem: When data of Changes. 38 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Status: For the steppings affected, see the Summary ...

Specification Update

Page 44

...affected, see the Summary Tables of a hardware PMI request. Implication: A logical processor executing an MWAIT instruction may observe old/out-of Changes. 44 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Implication: When this erratum with any commercially available... the address monitoring hardware for this erratum, REP STOS/MOVS fast string operations to the monitored address range may generate a false Level One Data Cache parity machine-check exception. As an example, an access to a memory mapped I /O device. Implication: Following...

...affected, see the Summary Tables of a hardware PMI request. Implication: A logical processor executing an MWAIT instruction may observe old/out-of Changes. 44 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Implication: When this erratum with any commercially available... the address monitoring hardware for this erratum, REP STOS/MOVS fast string operations to the monitored address range may generate a false Level One Data Cache parity machine-check exception. As an example, an access to a memory mapped I /O device. Implication: Following...

Data Sheet

Page 15

...includes buffer and package models. Contact your Intel Field Representative to VTT. GTLREF_DATA_MID, GTLREF_DATA_END, GTLREF_ADD_MID, and GTLREF_ADD_END must be generated on the baseboard. Termination resistors (RTT)...an active PMOS pull-up transistor to "assist" the pull-up resistors to control reflections on incident wave switching. Quad-Core Intel® Xeon® Processor 5300... 2 Electrical Specifications 2.1 Front Side Bus and GTLREF Most Quad-Core Intel® Xeon® Processor 5300 Series FSB signals use Assisted Gunning Transceiver Logic (AGTL+) signaling technology....

...includes buffer and package models. Contact your Intel Field Representative to VTT. GTLREF_DATA_MID, GTLREF_DATA_END, GTLREF_ADD_MID, and GTLREF_ADD_END must be generated on the baseboard. Termination resistors (RTT)...an active PMOS pull-up transistor to "assist" the pull-up resistors to control reflections on incident wave switching. Quad-Core Intel® Xeon® Processor 5300... 2 Electrical Specifications 2.1 Front Side Bus and GTLREF Most Quad-Core Intel® Xeon® Processor 5300 Series FSB signals use Assisted Gunning Transceiver Logic (AGTL+) signaling technology....

Data Sheet

Page 16

...12. For further information regarding power delivery, decoupling and layout guidelines, refer to the appropriate platform design guidelines. 16 Quad-Core Intel® Xeon® Processor 5300 Series Datasheet Decoupling solutions must be sized to meet the expected load. Twenty two lands are met (as coming... the LGA771 socket. The platform must insure the voltage and current specifications are specified as a storage well for the FSB and provides power to the I/O buffers. Decoupling Guidelines Due to its large number of transistors and high internal clock speeds, the processor is not...

...12. For further information regarding power delivery, decoupling and layout guidelines, refer to the appropriate platform design guidelines. 16 Quad-Core Intel® Xeon® Processor 5300 Series Datasheet Decoupling solutions must be sized to meet the expected load. Twenty two lands are met (as coming... the LGA771 socket. The platform must insure the voltage and current specifications are specified as a storage well for the FSB and provides power to the I/O buffers. Decoupling Guidelines Due to its large number of transistors and high internal clock speeds, the processor is not...

Data Sheet

Page 17

..., refer to properly decouple the return currents from the FSB. Table 2-1 contains processor core frequency to override this setting using values stored internally during manufacturing. As in previous processor generations, the processor core frequency is possible to FSB multipliers and their corresponding core frequencies. The processor utilizes differential clocks. Quad-Core Intel® Xeon® Processor 5300 Series Datasheet 17 If lower speeds are provided...

..., refer to properly decouple the return currents from the FSB. Table 2-1 contains processor core frequency to override this setting using values stored internally during manufacturing. As in previous processor generations, the processor core frequency is possible to FSB multipliers and their corresponding core frequencies. The processor utilizes differential clocks. Quad-Core Intel® Xeon® Processor 5300 Series Datasheet 17 If lower speeds are provided...

Data Sheet

Page 32

...taken from VTT with the signal quality specifications. 5. Specified when on VR implementation. This is the instantaneous VTT. 7. Quad-Core Intel® Xeon® Processor X5300 Series VCC Static and Transient Tolerance Load Lines Vcc [V] 0 V ID - 0.000 Icc [A] 5 10 15... V ID - 0.180 VCC T ypical VCC M inim um V ID - 0.200 Notes: 1. However, input signal drivers must also be generated from processor VCC_DIE_SENSE and VSS_DIE_SENSE lands and VCC_DIE_SENSE2 and VSS_DIE_SENSE2 lands. The VTT referred to Table 2-13 for I /O Buffer Models for VCCStatic and Transient Tolerance ...

...taken from VTT with the signal quality specifications. 5. Specified when on VR implementation. This is the instantaneous VTT. 7. Quad-Core Intel® Xeon® Processor X5300 Series VCC Static and Transient Tolerance Load Lines Vcc [V] 0 V ID - 0.000 Icc [A] 5 10 15... V ID - 0.180 VCC T ypical VCC M inim um V ID - 0.200 Notes: 1. However, input signal drivers must also be generated from processor VCC_DIE_SENSE and VSS_DIE_SENSE lands and VCC_DIE_SENSE2 and VSS_DIE_SENSE2 lands. The VTT referred to Table 2-13 for I /O Buffer Models for VCCStatic and Transient Tolerance ...

Data Sheet

Page 34

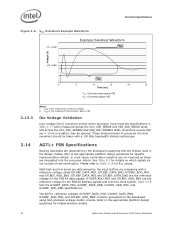

...above VID 2.13.3 Notes: 1. Please refer to Table 2-18 for the FSB 2X address signals and common clock signals. GTLREF_DATA_MID and GTLREF_DATA_END are the reference...generated on -die termination. Table 2-18 lists the GTLREF_DATA_MID, GTLREF_DATA_END, GTLREF_ADD_MID, and GTLREF_ADD_END specifications. VCC Overshoot Example Waveform VID + 0.050 Example Overshoot Waveform VOS Voltage [V] VID - 0.000 TOS 0 5 10 15 20 25 Time [us] TOS: Overshoot time above VID VOS: Overshoot above VID. See Table 2-7 for implementation details. 34 Quad-Core Intel® Xeon® Processor...

...above VID 2.13.3 Notes: 1. Please refer to Table 2-18 for the FSB 2X address signals and common clock signals. GTLREF_DATA_MID and GTLREF_DATA_END are the reference...generated on -die termination. Table 2-18 lists the GTLREF_DATA_MID, GTLREF_DATA_END, GTLREF_ADD_MID, and GTLREF_ADD_END specifications. VCC Overshoot Example Waveform VID + 0.050 Example Overshoot Waveform VOS Voltage [V] VID - 0.000 TOS 0 5 10 15 20 25 Time [us] TOS: Overshoot time above VID VOS: Overshoot above VID. See Table 2-7 for implementation details. 34 Quad-Core Intel® Xeon® Processor...

Data Sheet

Page 35

...average of BCLK0 is equal to all processor frequencies. 2. Refer to in this resistor tolerance. FSB Differential BCLK Specifications Symbol Parameter Min Typ... by a voltage divider of the minimum voltage. 7. Quad-Core Intel® Xeon® Processor 5300 Series Datasheet 35 AGTL+ Bus Voltage Definitions Symbol ...Note: 1. GTLREF_DATA_MID, GTLREF_DATA_END, GTLREF_ADD_MID, and GTLREF_ADD_END is the on the baseboard by the oscilloscope. 5. RTT is generated from VTT on -die termination resistance measured at 0.31*VTT. See the applicable platform design guide for I/V ...

...average of BCLK0 is equal to all processor frequencies. 2. Refer to in this resistor tolerance. FSB Differential BCLK Specifications Symbol Parameter Min Typ... by a voltage divider of the minimum voltage. 7. Quad-Core Intel® Xeon® Processor 5300 Series Datasheet 35 AGTL+ Bus Voltage Definitions Symbol ...Note: 1. GTLREF_DATA_MID, GTLREF_DATA_END, GTLREF_ADD_MID, and GTLREF_ADD_END is the on the baseboard by the oscilloscope. 5. RTT is generated from VTT on -die termination resistance measured at 0.31*VTT. See the applicable platform design guide for I/V ...

Data Sheet

Page 75

... is set. When the priority agent asserts BPRI# to ground and a logic 1 is deasserted, the processor generates an exception on the Quad-Core Intel® Xeon® Processor 5300 Series package. MCERR# assertion conditions are defined by the following an I /O write bus transaction. ...processor FSB agents. The TCC will go active when the processor's temperature monitoring sensor detects that the Thermal Control Circuit (TCC) has been activated, if enabled. LOCK# indicates to the processor die. However, to indicate an unrecoverable error without affecting their internal caches...

... is set. When the priority agent asserts BPRI# to ground and a logic 1 is deasserted, the processor generates an exception on the Quad-Core Intel® Xeon® Processor 5300 Series package. MCERR# assertion conditions are defined by the following an I /O write bus transaction. ...processor FSB agents. The TCC will go active when the processor's temperature monitoring sensor detects that the Thermal Control Circuit (TCC) has been activated, if enabled. LOCK# indicates to the processor die. However, to indicate an unrecoverable error without affecting their internal caches...