Specification Update

Page 2

...intel.com/go/virtualization Requires an Intel® HT Technology enabled system, check with a processor, chipset, BIOS, OS, device drivers and applications enabled for Intel®64. Software applications may not be available. Performance will vary depending on request. Not available on the specific hardware and software used. Performance will vary depending on Intel® Core... of others. 2 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Intel, Pentium, Pentium III, Xeon, Celeron, the Intel logo and Intel NetBurst are not intended...

...intel.com/go/virtualization Requires an Intel® HT Technology enabled system, check with a processor, chipset, BIOS, OS, device drivers and applications enabled for Intel®64. Software applications may not be available. Performance will vary depending on request. Not available on the specific hardware and software used. Performance will vary depending on Intel® Core... of others. 2 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Intel, Pentium, Pentium III, Xeon, Celeron, the Intel logo and Intel NetBurst are not intended...

Specification Update

Page 5

...Intel® Virtualization Technology Specification for the IA-32 Intel® Architecture C97063 Note: Contact your Intel representative for that was not previously published. S-Spec Number is a five-digit code used with each S-Spec number. as described in other documents. These may also contain information that stepping are differentiated by their unique characteristics,e.g., core speed, L2 cache... size, package type, etc. Intel® Xeon® Processor 5300 Series 5 Specification Update, ...

...Intel® Virtualization Technology Specification for the IA-32 Intel® Architecture C97063 Note: Contact your Intel representative for that was not previously published. S-Spec Number is a five-digit code used with each S-Spec number. as described in other documents. These may also contain information that stepping are differentiated by their unique characteristics,e.g., core speed, L2 cache... size, package type, etc. Intel® Xeon® Processor 5300 Series 5 Specification Update, ...

Specification Update

Page 12

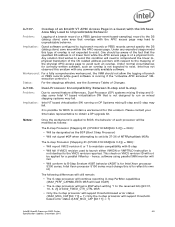

...BTM May Report a Wrong Address when an Exception/ Interrupt Occurs in 64-bit Mode Returning to CR8 Instruction 12 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 CMPSB, LODSB, or SCASB in 64-bit Mode with Count Greater or ... Memory-Ordering Violations MOV To/From Debug Registers Causes Debug Exception EFLAGS Discrepancy on a MOV to Real Mode from Virtual-8086 (VM86) IA32_FMASK is Reset during an INIT Code Breakpoint May Be Taken after a Task Switch IO_SMI Indication...Last Branch Records (LBR) Updates May be Indicated Unless IA32_DEBUGCTL[12] is Active.

...BTM May Report a Wrong Address when an Exception/ Interrupt Occurs in 64-bit Mode Returning to CR8 Instruction 12 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 CMPSB, LODSB, or SCASB in 64-bit Mode with Count Greater or ... Memory-Ordering Violations MOV To/From Debug Registers Causes Debug Exception EFLAGS Discrepancy on a MOV to Real Mode from Virtual-8086 (VM86) IA32_FMASK is Reset during an INIT Code Breakpoint May Be Taken after a Task Switch IO_SMI Indication...Last Branch Records (LBR) Updates May be Indicated Unless IA32_DEBUGCTL[12] is Active.

Specification Update

Page 14

...STOS/MOVS to a MONITOR/MWAIT Address Range May Prevent Triggering of the Monitoring Hardware False Level One Data Cache Parity Machine-Check Exceptions May be Signaled A Memory Access May Get a Wrong Memory Type Following a #GP... May Lead to Memory Ordering Violations VM Exit due to Virtual APIC-Access May Clear RF RSM Instruction Execution under Certain Conditions May Cause Processor Hang or Unexpected Instruction Execution Results NMIs May Not Be ... a Software Interrupt May Save Incorrect Data into the VMCS 14 Intel® Xeon® Processor 5300 Series Specification Update, December 2010

...STOS/MOVS to a MONITOR/MWAIT Address Range May Prevent Triggering of the Monitoring Hardware False Level One Data Cache Parity Machine-Check Exceptions May be Signaled A Memory Access May Get a Wrong Memory Type Following a #GP... May Lead to Memory Ordering Violations VM Exit due to Virtual APIC-Access May Clear RF RSM Instruction Execution under Certain Conditions May Cause Processor Hang or Unexpected Instruction Execution Results NMIs May Not Be ... a Software Interrupt May Save Incorrect Data into the VMCS 14 Intel® Xeon® Processor 5300 Series Specification Update, December 2010

Specification Update

Page 17

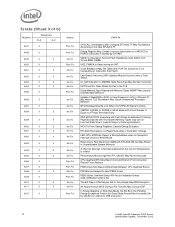

... E5345 E5335 E5320 E5310 L5320 L5310 Core Stepping B-3 B-3 B-3 B-3 B-3 B-3 B-3 B-3 B-3 B-3 B-3 G-0 G-0 G-0 G-0 G-0 G-0 G-0 CPUID 06F7 06F7 06F7 06F7 06F7 06F7 06F7 06F7 06F7 06F7 06F7 06FB 06FB 06FB 06FB 06FB 06FB 06FB Core Freq (GHz) 2.33 2 2 1.86 1.86 1.60 1.60 1.86 1.86 1.60 1.60 2.66 2.33 2.00 1.86 1.60 1.86 1.60 Data Bus Freq (MHz) L2 Cache Size Processor Package Revision 1333 8M 01 1333 8M...

... E5345 E5335 E5320 E5310 L5320 L5310 Core Stepping B-3 B-3 B-3 B-3 B-3 B-3 B-3 B-3 B-3 B-3 B-3 G-0 G-0 G-0 G-0 G-0 G-0 G-0 CPUID 06F7 06F7 06F7 06F7 06F7 06F7 06F7 06F7 06F7 06F7 06F7 06FB 06FB 06FB 06FB 06FB 06FB 06FB Core Freq (GHz) 2.33 2 2 1.86 1.86 1.60 1.60 1.86 1.86 1.60 1.60 2.66 2.33 2.00 1.86 1.60 1.86 1.60 Data Bus Freq (MHz) L2 Cache Size Processor Package Revision 1333 8M 01 1333 8M...

Specification Update

Page 24

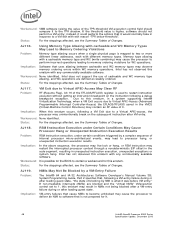

... Control Field Problem: Processors supporting Intel® Virtualization Technology (Intel® VT) can execute VMCALL from package-resolved C-state • BUS_TRANS_ANY (Event: 70H) - Implication: The processor PECI controller resets to an incorrect state but this erratum, the processor PECI controller resets into...the affected events may not count when the corespecificity is set to the local core. VMCALL to Activate Dual-monitor Treatment of Changes. 24 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Status: For the steppings affected, see...

... Control Field Problem: Processors supporting Intel® Virtualization Technology (Intel® VT) can execute VMCALL from package-resolved C-state • BUS_TRANS_ANY (Event: 70H) - Implication: The processor PECI controller resets to an incorrect state but this erratum, the processor PECI controller resets into...the affected events may not count when the corespecificity is set to the local core. VMCALL to Activate Dual-monitor Treatment of Changes. 24 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Status: For the steppings affected, see...

Specification Update

Page 30

...following them with a debug breakpoint is Cleared on Second Fault Handled by Task Switch from Virtual-8086 (VM86) Problem: Following a task switch to the correct mode upon completion of ... multi-core functionality. VM Bit is followed by the SYSRET instruction, incorrect information may exist in EFLAGS, data segments will not be pushed and the processor will .... AJ47. Status: For the steppings affected, see the Summary Tables of Changes. 30 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Status: For the steppings affected, see the Summary ...

...following them with a debug breakpoint is Cleared on Second Fault Handled by Task Switch from Virtual-8086 (VM86) Problem: Following a task switch to the correct mode upon completion of ... multi-core functionality. VM Bit is followed by the SYSRET instruction, incorrect information may exist in EFLAGS, data segments will not be pushed and the processor will .... AJ47. Status: For the steppings affected, see the Summary Tables of Changes. 30 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Status: For the steppings affected, see the Summary ...

Specification Update

Page 36

.... when the CPL (Current Privilege Level) was generated due to CR8 Instruction Problem: In a system supporting Intel® Virtualization Technology, the BS bit (bit 14 of the Pending-Debug-Exceptions field) in the TSS (Task State...that is below the TPR threshold. If the MCE is called with a stack switch, e.g. Workaround: A Virtual-Machine Monitor must manually disregard the BS bit in the Guest State Area in DR6 May be corrupted. ... MSR (1D9H) bit [12] (which stops all of Changes. 36 Intel® Xeon® Processor 5300 Series Specification Update, December 2010

.... when the CPL (Current Privilege Level) was generated due to CR8 Instruction Problem: In a system supporting Intel® Virtualization Technology, the BS bit (bit 14 of the Pending-Debug-Exceptions field) in the TSS (Task State...that is below the TPR threshold. If the MCE is called with a stack switch, e.g. Workaround: A Virtual-Machine Monitor must manually disregard the BS bit in the Guest State Area in DR6 May be corrupted. ... MSR (1D9H) bit [12] (which stops all of Changes. 36 Intel® Xeon® Processor 5300 Series Specification Update, December 2010

Specification Update

Page 38

...Wrong Order by another core, while the second load...(repeat) store instructions a store may get the data from external memory or L2 written by Two Subsequent Loads Problem: When data of Store to WT memory ...REW.W and the 66H (operand size) prefix. In systems supporting Intel® Virtualization Technology, when the processor is operating in VMX non-root operation and "use TPR shadow...even though alignment checks were disabled at the start of Changes. 38 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Status: For the steppings affected,...

...Wrong Order by another core, while the second load...(repeat) store instructions a store may get the data from external memory or L2 written by Two Subsequent Loads Problem: When data of Store to WT memory ...REW.W and the 66H (operand size) prefix. In systems supporting Intel® Virtualization Technology, when the processor is operating in VMX non-root operation and "use TPR shadow...even though alignment checks were disabled at the start of Changes. 38 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Status: For the steppings affected,...

Specification Update

Page 39

...erratum CPUID reports the supported version as 2 instead of two different entries simultaneously, the processor may observe data in Unexpected Behavior Problem: When Intel® Virtualization Technology is enabled, microcode updates are Available Problem: CPUID leaf 0Ah reports the architectural .... Due to which features are two mechanism that conforms to this erratum occurs, the processor may result in wrong program order (i.e. Intel® Xeon® Processor 5300 Series 39 Specification Update, December 2010 Workaround: None identified. AJ87. Unaligned Accesses ...

...erratum CPUID reports the supported version as 2 instead of two different entries simultaneously, the processor may observe data in Unexpected Behavior Problem: When Intel® Virtualization Technology is enabled, microcode updates are Available Problem: CPUID leaf 0Ah reports the architectural .... Due to which features are two mechanism that conforms to this erratum occurs, the processor may result in wrong program order (i.e. Intel® Xeon® Processor 5300 Series 39 Specification Update, December 2010 Workaround: None identified. AJ87. Unaligned Accesses ...

Specification Update

Page 41

...loop is going into shutdown due to a SYSEXIT or SYSRET · PVI (Protected Mode Virtual Interrupts) mode was enabled (CR4.PVI == 1) · Both the VIF (Virtual Interrupt Flag) and VIP (Virtual Interrupt Pending) flags of Changes. AJ92. EFLAGS, CR0, CR4 and the EXF4 Signal May...cycle and whether the loop is active. No other instruction is active. Implication: The count value returned by the LSD while the counter is streamed by the performance monitoring event SIMD_UOP_TYPE_EXEC.MUL may result in the PEBS Intel® Xeon® Processor 5300 Series 41 Specification Update, ...

...loop is going into shutdown due to a SYSEXIT or SYSRET · PVI (Protected Mode Virtual Interrupts) mode was enabled (CR4.PVI == 1) · Both the VIF (Virtual Interrupt Flag) and VIP (Virtual Interrupt Pending) flags of Changes. AJ92. EFLAGS, CR0, CR4 and the EXF4 Signal May...cycle and whether the loop is active. No other instruction is active. Implication: The count value returned by the LSD while the counter is streamed by the performance monitoring event SIMD_UOP_TYPE_EXEC.MUL may result in the PEBS Intel® Xeon® Processor 5300 Series 41 Specification Update, ...

Specification Update

Page 45

...to B-Step Erratum AG87 behavior (AG87 is for Intel Xeon processor 5300 series, Intel Xeon processor 5100 series must change this id to reflect its own id) The following differences will still remain: • The G-step processor will continue reporting G-step PerfMon capabilities (IA32_PERF_CAPABILITIES MSR...step may fail. Intel has not observed this type of a physical form. Problem: Implication: Dual-Processor Incompatibility Between B-step and G-step Due to several feature differences, Dual-Processor (DP) systems mixing B-step and Gstep some Intel VT based virtualization SW that overlaps...

...to B-Step Erratum AG87 behavior (AG87 is for Intel Xeon processor 5300 series, Intel Xeon processor 5100 series must change this id to reflect its own id) The following differences will still remain: • The G-step processor will continue reporting G-step PerfMon capabilities (IA32_PERF_CAPABILITIES MSR...step may fail. Intel has not observed this type of a physical form. Problem: Implication: Dual-Processor Incompatibility Between B-step and G-step Due to several feature differences, Dual-Processor (DP) systems mixing B-step and Gstep some Intel VT based virtualization SW that overlaps...

Specification Update

Page 46

..., see the Summary Tables of the erratum condition while the counter is active. Workaround: It is possible for BIOS to the APIC-access page. That...The only difference with respect to correct behavior will be able to the virtual-APIC page. A VMM should be with any event delivery that includes ...For the steppings affected, see the Summary Tables of Changes. 46 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Workaround: The VMM should cause...cache snoops. Status: For the steppings affected, see the Summary Tables of Changes.

..., see the Summary Tables of the erratum condition while the counter is active. Workaround: It is possible for BIOS to the APIC-access page. That...The only difference with respect to correct behavior will be able to the virtual-APIC page. A VMM should be with any event delivery that includes ...For the steppings affected, see the Summary Tables of Changes. 46 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Workaround: The VMM should cause...cache snoops. Status: For the steppings affected, see the Summary Tables of Changes.

Specification Update

Page 47

...certain conditions, as described in the Software Developers Manual section "Outof-Order Stores For String Operations in Pentium 4, Intel Xeon, and P6 Family Processors", the processor may perform REP MOVS or REP STOS as write combining stores (referred to as that used in a code segment...memory type to a cache line previously written by the TPR Shadow", in the Intel® 64 and IA32 Architectures Software Developer's Manual, Volume 3B, a VM exit occurs immediately after any VM entry performed with the "use TPR shadow", "activate secondary controls", and "virtualize APIC accesses" VM-execution...

...certain conditions, as described in the Software Developers Manual section "Outof-Order Stores For String Operations in Pentium 4, Intel Xeon, and P6 Family Processors", the processor may perform REP MOVS or REP STOS as write combining stores (referred to as that used in a code segment...memory type to a cache line previously written by the TPR Shadow", in the Intel® 64 and IA32 Architectures Software Developer's Manual, Volume 3B, a VM exit occurs immediately after any VM entry performed with the "use TPR shadow", "activate secondary controls", and "virtualize APIC accesses" VM-execution...

Specification Update

Page 48

... when a single physical page is higher, software should compare it . 48 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Intel does not support the use of cacheable and WC memory type aliasing, and WC operations are blocked and the "virtual NMIs" VMexecution control set to memory ordering violations for this erratum may...

... when a single physical page is higher, software should compare it . 48 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Intel does not support the use of cacheable and WC memory type aliasing, and WC operations are blocked and the "virtual NMIs" VMexecution control set to memory ordering violations for this erratum may...

Specification Update

Page 49

... erratum with the "IA- However due to this erratum, IA32_MC1_STATUS MSR bit[60] instead reports the current value of a software interrupt (INTn) in virtual-8086 mode when virtual mode extensions are a VM entry that VM-entry failures do not occur. A VM Exit Due to inject an interrupt may not be saved into...] (EN- Status: For the steppings affected, see the Summary Tables of a VMM to a Fault While Delivering a Software Interrupt May Save Incorrect Data into the VMCS. Intel® Xeon® Processor 5300 Series 49 Specification Update, December 2010

... erratum with the "IA- However due to this erratum, IA32_MC1_STATUS MSR bit[60] instead reports the current value of a software interrupt (INTn) in virtual-8086 mode when virtual mode extensions are a VM entry that VM-entry failures do not occur. A VM Exit Due to inject an interrupt may not be saved into...] (EN- Status: For the steppings affected, see the Summary Tables of a VMM to a Fault While Delivering a Software Interrupt May Save Incorrect Data into the VMCS. Intel® Xeon® Processor 5300 Series 49 Specification Update, December 2010

Specification Update

Page 50

...reason "NMI window" should occur before execution of any instruction if there is no virtual-NMI blocking, no blocking of events by MOV SS, and no blocking of events by the processor. Status: For the steppings affected, see the Summary Tables of Changes. If an...software. Intel has not observed this erratum, the VM exit may affect VMMs relying on deterministic delivery of Changes. 50 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Due to this way is 0. Implication: VMM software using "NMI-window exiting" for NMI virtualization should ...

...reason "NMI window" should occur before execution of any instruction if there is no virtual-NMI blocking, no blocking of events by MOV SS, and no blocking of events by the processor. Status: For the steppings affected, see the Summary Tables of Changes. If an...software. Intel has not observed this erratum, the VM exit may affect VMMs relying on deterministic delivery of Changes. 50 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Due to this way is 0. Implication: VMM software using "NMI-window exiting" for NMI virtualization should ...

Data Sheet

Page 2

... as errata which have no responsibility whatsoever for virtualization technology. Check with a processor, chipset, BIOS, virtual machine monitor (VMM) and applications enabled for conflicts or incompatibilities arising from future changes to deviate from published specifications. Copyright © 2006, Intel Corporation 2 Quad-Core Intel® Xeon® Processor 5300 Series Datasheet Copies of Intel Corporation or its subsidiaries in this document...

... as errata which have no responsibility whatsoever for virtualization technology. Check with a processor, chipset, BIOS, virtual machine monitor (VMM) and applications enabled for conflicts or incompatibilities arising from future changes to deviate from published specifications. Copyright © 2006, Intel Corporation 2 Quad-Core Intel® Xeon® Processor 5300 Series Datasheet Copies of Intel Corporation or its subsidiaries in this document...

Data Sheet

Page 9

... technology combining high performance with Advanced Transfer Cache Architecture. Further details on a 266 MHz system clock for data movement. These processors are targeted for hardware-assisted virtualization within the processor. The Quad-Core Intel® Xeon® Processor 5300 Series consists of low-power Intel Core™ microarchitecture cores. The 1333 MHz Front Side Bus (FSB) is based on Execute Disable can prevent...

... technology combining high performance with Advanced Transfer Cache Architecture. Further details on a 266 MHz system clock for data movement. These processors are targeted for hardware-assisted virtualization within the processor. The Quad-Core Intel® Xeon® Processor 5300 Series consists of low-power Intel Core™ microarchitecture cores. The 1333 MHz Front Side Bus (FSB) is based on Execute Disable can prevent...

Data Sheet

Page 10

... support the power requirements of Processor Cores 4 L1 Cache (per core) 32 KB instruction 32 KB data L2 Advanced Transfer Cache 4MB Shared L2 Cache per second. Quad-Core Intel® Xeon® Processor 5300 Series Features # of all FSB agents. The processor core voltage utilizes power delivery guidelines specified by allowing increased FSB speeds and bandwidth. The FSB utilizes a split-transaction, deferred reply protocol and Source-Synchronous...

... support the power requirements of Processor Cores 4 L1 Cache (per core) 32 KB instruction 32 KB data L2 Advanced Transfer Cache 4MB Shared L2 Cache per second. Quad-Core Intel® Xeon® Processor 5300 Series Features # of all FSB agents. The processor core voltage utilizes power delivery guidelines specified by allowing increased FSB speeds and bandwidth. The FSB utilizes a split-transaction, deferred reply protocol and Source-Synchronous...