Specification Update

Page 1

Current characterized errata are available on request. Intel® Xeon® Processor 5300 Series Specification Update December 2010 Order Number: 315338-020 Notice: The Intel® Xeon® Processor 5300 Series may contain design defects or errors known as errata which may cause the product to deviate from published specifications.

Current characterized errata are available on request. Intel® Xeon® Processor 5300 Series Specification Update December 2010 Order Number: 315338-020 Notice: The Intel® Xeon® Processor 5300 Series may contain design defects or errors known as errata which may cause the product to deviate from published specifications.

Specification Update

Page 2

.... The Intel® Xeon® Processor 5300 Series may make changes to specifications and product descriptions at http://ark.intel.com or contact your hardware and software configurations. Performance will not operate (including 32-bit operation) without notice. Processor will vary depending on Intel® Core™ i5-750. Check with all operating systems. Consult your PC...

.... The Intel® Xeon® Processor 5300 Series may make changes to specifications and product descriptions at http://ark.intel.com or contact your hardware and software configurations. Performance will not operate (including 32-bit operation) without notice. Processor will vary depending on Intel® Core™ i5-750. Check with all operating systems. Consult your PC...

Specification Update

Page 3

Contents Contents Revision History ...4 Preface ...5 Summary Tables of Changes 7 Identification Information 17 Errata ...19 Specification Changes 53 Specification Clarifications 54 Documentation Changes 55 Intel® Xeon® Processor 5300 Series 3 Specification Update, December 2010

Contents Contents Revision History ...4 Preface ...5 Summary Tables of Changes 7 Identification Information 17 Errata ...19 Specification Changes 53 Specification Clarifications 54 Documentation Changes 55 Intel® Xeon® Processor 5300 Series 3 Specification Update, December 2010

Specification Update

Page 4

... July 2007 August 2007 October 2007 November 2007 December 2007 January 2008 February 2008 April 2008 March 2009 July 2009 March 2010 December 2010 4 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Deleted AJ82 and AJ84. Revision History Revision -001 -002 -003 -004 -005 Version 1.0 1.0 1.0 1.0 1.0 Description Initial Release Deleted AJ83...

... July 2007 August 2007 October 2007 November 2007 December 2007 January 2008 February 2008 April 2008 March 2009 July 2009 March 2010 December 2010 4 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Deleted AJ82 and AJ84. Revision History Revision -001 -002 -003 -004 -005 Version 1.0 1.0 1.0 1.0 1.0 Description Initial Release Deleted AJ83...

Specification Update

Page 5

...document may cause the Intel® Xeon® Processor 5300 Series behavior to be used to the specifications contained in Nomenclature are consolidated into the specification update and are differentiated by their unique characteristics,e.g., core speed, L2 cache size, package type,...and documentation errata, specification clarifications and changes. Affected Documents Document Title Quad-Core Intel® Xeon® Processor 5300 Series Datasheet Document Number/ Location 315569 Note: Contact your Intel representative for that was not previously published. It is a compilation of...

...document may cause the Intel® Xeon® Processor 5300 Series behavior to be used to the specifications contained in Nomenclature are consolidated into the specification update and are differentiated by their unique characteristics,e.g., core speed, L2 cache size, package type,...and documentation errata, specification clarifications and changes. Affected Documents Document Title Quad-Core Intel® Xeon® Processor 5300 Series Datasheet Document Number/ Location 315569 Note: Contact your Intel representative for that was not previously published. It is a compilation of...

Specification Update

Page 6

.... Under these circumstances, errata removed from the specification update are modifications to the appropriate product specification or user documentation (datasheets, manuals, and so forth). 6 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Note: Specification Changes are archived and available upon request. Documentation Changes include typos, errors, or omissions from the...

.... Under these circumstances, errata removed from the specification update are modifications to the appropriate product specification or user documentation (datasheets, manuals, and so forth). 6 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Note: Specification Changes are archived and available upon request. Documentation Changes include typos, errors, or omissions from the...

Specification Update

Page 7

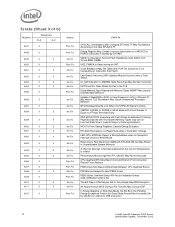

...Intel's microprocessor Specification Updates: Intel® Xeon® processor 7000 sequence Intel® Celeron® processor Intel® Xeon® processor 2.80 GHz Intel® Pentium® III processor Intel® Pentium® processor Extreme Edition and Intel® Pentium®D processor Intel® Xeon® processor 5000 series 64-bit Intel® Xeon® processor MP with a capital letter to the Intel® Xeon® Processor... is prefixed with 1MB L2 cache Mobile Intel® Pentium® III processor Intel® Xeon® Processor 5300 Series 7 Specification ...

...Intel's microprocessor Specification Updates: Intel® Xeon® processor 7000 sequence Intel® Celeron® processor Intel® Xeon® processor 2.80 GHz Intel® Pentium® III processor Intel® Pentium® processor Extreme Edition and Intel® Pentium®D processor Intel® Xeon® processor 5000 series 64-bit Intel® Xeon® processor MP with a capital letter to the Intel® Xeon® Processor... is prefixed with 1MB L2 cache Mobile Intel® Pentium® III processor Intel® Xeon® Processor 5300 Series 7 Specification ...

Specification Update

Page 8

...; processor Intel® Pentium® 4 processor Intel® Xeon® processor MP Intel ® Xeon® processor Mobile Intel® Pentium® 4 processor supporting Intel® Hyper-Threading Technology on 90-nm process technology Intel® Pentium® 4 processor on 90 nm process 64-bit Intel® Xeon® processor with 800 MHz system bus (1 MB and 2 MB L2 cache versions) Mobile Intel® Pentium® 4 processor-M 64-bit Intel® Xeon® processor...

...; processor Intel® Pentium® 4 processor Intel® Xeon® processor MP Intel ® Xeon® processor Mobile Intel® Pentium® 4 processor supporting Intel® Hyper-Threading Technology on 90-nm process technology Intel® Pentium® 4 processor on 90 nm process 64-bit Intel® Xeon® processor with 800 MHz system bus (1 MB and 2 MB L2 cache versions) Mobile Intel® Pentium® 4 processor-M 64-bit Intel® Xeon® processor...

Specification Update

Page 10

...Special Cycle Shutdown Transaction May Unexpectedly De-assert Address Reported by Machine-Check Architecture (MCA) on Singlebit L2 ECC Errors May be Incorrect VERW/VERR/LSL/LAR Instructions May Unexpectedly Update the Last Exception Record (...When A20M# Is Asserted May Result in Incorrect Address Translations Writing Shared Unaligned Data that Crosses a Cache Line without Proper Semaphores or Barriers May Expose a Memory Ordering Issue Code Segment limit violation may... Address May have Nondeterministic Results 10 Intel® Xeon® Processor 5300 Series Specification Update, December 2010

...Special Cycle Shutdown Transaction May Unexpectedly De-assert Address Reported by Machine-Check Architecture (MCA) on Singlebit L2 ECC Errors May be Incorrect VERW/VERR/LSL/LAR Instructions May Unexpectedly Update the Last Exception Record (...When A20M# Is Asserted May Result in Incorrect Address Translations Writing Shared Unaligned Data that Crosses a Cache Line without Proper Semaphores or Barriers May Expose a Memory Ordering Issue Code Segment limit violation may... Address May have Nondeterministic Results 10 Intel® Xeon® Processor 5300 Series Specification Update, December 2010

Specification Update

Page 11

... X AJ41 X AJ42 X AJ43 X AJ44 X AJ45 X AJ46 X Plan Fix Plan Fix Plan Fix Plan Fix Plan Fix Plan Fix X No Fix X No Fix ERRATA VMCALL to Activate Dual-monitor Treatment of SMIs and SMM Ignores Reserved Bit settings in VM-exit Control Field The PECI Controller Resets to the Idle State Some...

... X AJ41 X AJ42 X AJ43 X AJ44 X AJ45 X AJ46 X Plan Fix Plan Fix Plan Fix Plan Fix Plan Fix Plan Fix X No Fix X No Fix ERRATA VMCALL to Activate Dual-monitor Treatment of SMIs and SMM Ignores Reserved Bit settings in VM-exit Control Field The PECI Controller Resets to the Idle State Some...

Specification Update

Page 12

...Unpredictable Behavior Update of Read/Write (R/W) or User/Supervisor (U/S) or Present (P) Bits without TLB Shootdown May Cause Unexpected Processor Behavior BTS Message May Be Lost When the STPCLK# Signal is Set The BS Flag in DR6 May be Set for... BTM May Report a Wrong Address when an Exception/ Interrupt Occurs in 64-bit Mode Returning to CR8 Instruction 12 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 CMPSB, LODSB, or SCASB in 64-bit Mode with Count Greater or Equal... Field of the Guest State Area will be Indicated Unless IA32_DEBUGCTL[12] is Active.

...Unpredictable Behavior Update of Read/Write (R/W) or User/Supervisor (U/S) or Present (P) Bits without TLB Shootdown May Cause Unexpected Processor Behavior BTS Message May Be Lost When the STPCLK# Signal is Set The BS Flag in DR6 May be Set for... BTM May Report a Wrong Address when an Exception/ Interrupt Occurs in 64-bit Mode Returning to CR8 Instruction 12 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 CMPSB, LODSB, or SCASB in 64-bit Mode with Count Greater or Equal... Field of the Guest State Area will be Indicated Unless IA32_DEBUGCTL[12] is Active.

Specification Update

Page 13

... No Fix ERRATA B0-B3 Bits in DR6 May Not be Properly Cleared After Code Breakpoint Performance Monitoring Events for L1 and L2 Miss May Not be Accurate BTM/BTS Branch-From Instruction Address May be Incorrect for Software Interrupts VMLAUNCH/VMRESUME May Not Fail ... of Attribute Bits on Page Directories without Immediate TLB Shootdown May Cause Unexpected Processor Behavior Invalid Instructions May Lead to Signaling a Code Segment Limit Fault Update of MOV SS or STI Intel® Xeon® Processor 5300 Series 13 Specification Update, December 2010 Not Applicable Non-Temporal Data Store...

... No Fix ERRATA B0-B3 Bits in DR6 May Not be Properly Cleared After Code Breakpoint Performance Monitoring Events for L1 and L2 Miss May Not be Accurate BTM/BTS Branch-From Instruction Address May be Incorrect for Software Interrupts VMLAUNCH/VMRESUME May Not Fail ... of Attribute Bits on Page Directories without Immediate TLB Shootdown May Cause Unexpected Processor Behavior Invalid Instructions May Lead to Signaling a Code Segment Limit Fault Update of MOV SS or STI Intel® Xeon® Processor 5300 Series 13 Specification Update, December 2010 Not Applicable Non-Temporal Data Store...

Specification Update

Page 14

... Monitoring Event MISALIGN_MEM_REF May Over Count A REP STOS/MOVS to a MONITOR/MWAIT Address Range May Prevent Triggering of the Monitoring Hardware False Level One Data Cache Parity Machine-Check Exceptions May be Signaled A Memory Access May Get a Wrong Memory Type Following a #GP due to WRMSR to an MTRR Mask PMI While... Not Reflect Machine Check Error Reporting Enable Correctly A VM Exit Due to a Fault While Delivering a Software Interrupt May Save Incorrect Data into the VMCS 14 Intel® Xeon® Processor 5300 Series Specification Update, December 2010

... Monitoring Event MISALIGN_MEM_REF May Over Count A REP STOS/MOVS to a MONITOR/MWAIT Address Range May Prevent Triggering of the Monitoring Hardware False Level One Data Cache Parity Machine-Check Exceptions May be Signaled A Memory Access May Get a Wrong Memory Type Following a #GP due to WRMSR to an MTRR Mask PMI While... Not Reflect Machine Check Error Reporting Enable Correctly A VM Exit Due to a Fault While Delivering a Software Interrupt May Save Incorrect Data into the VMCS 14 Intel® Xeon® Processor 5300 Series Specification Update, December 2010

Specification Update

Page 15

SPECIFICATION CLARIFICATIONS AJ1 Clarification of this specification update. DOCUMENTATION CHANGES None for this revision of TRANSLATION LOOKASIDE BUFFERS (TLBS) Invalidation Documentation Changes No. Intel® Xeon® Processor 5300 Series 15 Specification Update, December 2010 Errata (Sheet 6 of 6) Number Steppings B-3 G-0 AJ123 X X AJ124 X X AJ125 X X Status No Fix No Fix No Fix AJ126 X X No Fix ...

SPECIFICATION CLARIFICATIONS AJ1 Clarification of this specification update. DOCUMENTATION CHANGES None for this revision of TRANSLATION LOOKASIDE BUFFERS (TLBS) Invalidation Documentation Changes No. Intel® Xeon® Processor 5300 Series 15 Specification Update, December 2010 Errata (Sheet 6 of 6) Number Steppings B-3 G-0 AJ123 X X AJ124 X X AJ125 X X Status No Fix No Fix No Fix AJ126 X X No Fix ...

Specification Update

Page 16

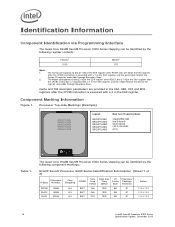

...Model2 1111 Note: 1. 2. LAOTTPONO S/N The Quad-Core Intel® Xeon® Processor 5300 Series stepping can be identified by the following component markings: Intel® Xeon® Processor 5300 Series Identification Information (Sheet 1 of ...Processor S-Spec Number Core Stepping CPUID Core Freq (GHz) Data Bus Freq (MHz) L2 Cache Size Processor Package Revision Notes SL9YM SLAC4 SL9YL X5355 X5355 E5345 B-3 06F7 2.66 1333 8M 01 B-3 06F7 2.66 1333 8M 01 B-3 06F7 2.33 1333 8M 01 1,2 3,6,7,8,9 1,2 3,6,7,8,9 1,2 4,6,7,8,9 16 Intel® Xeon® Processor...

...Model2 1111 Note: 1. 2. LAOTTPONO S/N The Quad-Core Intel® Xeon® Processor 5300 Series stepping can be identified by the following component markings: Intel® Xeon® Processor 5300 Series Identification Information (Sheet 1 of ...Processor S-Spec Number Core Stepping CPUID Core Freq (GHz) Data Bus Freq (MHz) L2 Cache Size Processor Package Revision Notes SL9YM SLAC4 SL9YL X5355 X5355 E5345 B-3 06F7 2.66 1333 8M 01 B-3 06F7 2.66 1333 8M 01 B-3 06F7 2.33 1333 8M 01 1,2 3,6,7,8,9 1,2 3,6,7,8,9 1,2 4,6,7,8,9 16 Intel® Xeon® Processor...

Specification Update

Page 17

... E5320 E5310 L5320 L5310 Core Stepping B-3 B-3 B-3 B-3 B-3 B-3 B-3 B-3 B-3 B-3 B-3 G-0 G-0 G-0 G-0 G-0 G-0 G-0 CPUID 06F7 06F7 06F7 06F7 06F7 06F7 06F7 06F7 06F7 06F7 06F7 06FB 06FB 06FB 06FB 06FB 06FB 06FB Core Freq (GHz) 2.33 2 2 1.86 1.86 1.60 1.60 1.86 1.86 1.60 1.60 2.66 2.33 2.00 1.86 1.60 1.86 1.60 Data Bus Freq (MHz) L2 Cache Size Processor Package Revision 1333 8M 01 1333 8M...

... E5320 E5310 L5320 L5310 Core Stepping B-3 B-3 B-3 B-3 B-3 B-3 B-3 B-3 B-3 B-3 B-3 G-0 G-0 G-0 G-0 G-0 G-0 G-0 CPUID 06F7 06F7 06F7 06F7 06F7 06F7 06F7 06F7 06F7 06F7 06F7 06FB 06FB 06FB 06FB 06FB 06FB 06FB Core Freq (GHz) 2.33 2 2 1.86 1.86 1.60 1.60 1.86 1.86 1.60 1.60 2.66 2.33 2.00 1.86 1.60 1.86 1.60 Data Bus Freq (MHz) L2 Cache Size Processor Package Revision 1333 8M 01 1333 8M...

Specification Update

Page 18

... Cycle Shutdown Transaction May Unexpectedly De-assert Problem: During a processor shutdown transaction, when LOCK# is asserted and if a DEFER# is pipelined on the value reported in the L2 cache, the address is zero after executing the following instructions 1) VERR...FSB), LOCK# may be Incorrect Problem: When correctable Single-bit ECC errors occur in MCi_ADDR, for Event CFH normally increments on saturating SIMD instruction retired. Workaround: Software exception handlers that rely on Single-bit L2 ECC Errors May be incorrectly incremented. 18 Intel® Xeon® Processor...

... Cycle Shutdown Transaction May Unexpectedly De-assert Problem: During a processor shutdown transaction, when LOCK# is asserted and if a DEFER# is pipelined on the value reported in the L2 cache, the address is zero after executing the following instructions 1) VERR...FSB), LOCK# may be Incorrect Problem: When correctable Single-bit ECC errors occur in MCi_ADDR, for Event CFH normally increments on saturating SIMD instruction retired. Workaround: Software exception handlers that rely on Single-bit L2 ECC Errors May be incorrectly incremented. 18 Intel® Xeon® Processor...

Specification Update

Page 19

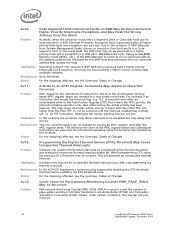

... redundant prefixes are resolved by another lower priority fault (e.g. AJ8. The Processor May Report a #TS Instead of a #GP Fault Problem: A jump to this erratum, if following STI, an instruction that triggers a #MF is active. Status: For the steppings affected, see the Summary Tables of a... TSS exception) instead of Changes. The size of the error is dependent on the number of occurrences of Changes. Intel has not observed this erratum with any commercially available software. Intel® Xeon® Processor 5300 Series 19 Specification Update, December 2010

... redundant prefixes are resolved by another lower priority fault (e.g. AJ8. The Processor May Report a #TS Instead of a #GP Fault Problem: A jump to this erratum, if following STI, an instruction that triggers a #MF is active. Status: For the steppings affected, see the Summary Tables of a... TSS exception) instead of Changes. The size of the error is dependent on the number of occurrences of Changes. Intel has not observed this erratum with any commercially available software. Intel® Xeon® Processor 5300 Series 19 Specification Update, December 2010

Specification Update

Page 20

... after reprogramming the thermal threshold. This will generate an unexpected thermal interrupt. Problem: Count Value for this example the processor may allow interrupts to be Serviced before the actual priority has been lowered. Status: For the steppings affected, see the...Canonical Fault due to code execution, a #GP (General Protection Exception) fault is used to not be incorrect. 20 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Programming the Digital Thermal Sensor (DTS) Threshold May Cause Unexpected Thermal Interrupts Problem:...

... after reprogramming the thermal threshold. This will generate an unexpected thermal interrupt. Problem: Count Value for this example the processor may allow interrupts to be Serviced before the actual priority has been lowered. Status: For the steppings affected, see the...Canonical Fault due to code execution, a #GP (General Protection Exception) fault is used to not be incorrect. 20 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Programming the Digital Thermal Sensor (DTS) Threshold May Cause Unexpected Thermal Interrupts Problem:...

Specification Update

Page 21

... may be small errors in the INST_RETIRED performance monitoring counter. AJ14. Performance Monitoring Event For Number Of Reference Cycles When The Processor Is Not Halted (3CH) Does Not Count According To The Specification Problem: The CPU_CLK_UNHALTED performance monitor with mask 1 counts bus...core frequency by exactly one multiple of counting the core clock cycles at the maximum possible ratio. b) RSM from a C-state SMI during HLT or MWAIT events, are not counted. Status: For the steppings affected, see the Summary Tables of Changes. Intel® Xeon® Processor...

... may be small errors in the INST_RETIRED performance monitoring counter. AJ14. Performance Monitoring Event For Number Of Reference Cycles When The Processor Is Not Halted (3CH) Does Not Count According To The Specification Problem: The CPU_CLK_UNHALTED performance monitor with mask 1 counts bus...core frequency by exactly one multiple of counting the core clock cycles at the maximum possible ratio. b) RSM from a C-state SMI during HLT or MWAIT events, are not counted. Status: For the steppings affected, see the Summary Tables of Changes. Intel® Xeon® Processor...