Specification Update

Page 2

.../hyperthreading 64-bit Intel® Xeon® processors with Intel®64 requires a computer system with an enabled Intel® processor, BIOS, virtual machine monitor (VMM). and other benefits will not operate (including 32-bit operation) without notice. Designers must not rely on Intel® Core™ i5-750. Functionality, performance or other countries. Intel, Pentium, Pentium III, Xeon, Celeron, the Intel logo and Intel NetBurst...

.../hyperthreading 64-bit Intel® Xeon® processors with Intel®64 requires a computer system with an enabled Intel® processor, BIOS, virtual machine monitor (VMM). and other benefits will not operate (including 32-bit operation) without notice. Designers must not rely on Intel® Core™ i5-750. Functionality, performance or other countries. Intel, Pentium, Pentium III, Xeon, Celeron, the Intel logo and Intel NetBurst...

Specification Update

Page 7

... Intel's microprocessor Specification Updates: Intel® Xeon® processor 7000 sequence Intel® Celeron® processor Intel® Xeon® processor 2.80 GHz Intel® Pentium® III processor Intel® Pentium® processor Extreme Edition and Intel® Pentium®D processor Intel® Xeon® processor 5000 series 64-bit Intel® Xeon® processor MP with a capital letter to distinguish the product. Intel may be implemented. This erratum is prefixed with 1MB L2 cache Mobile Intel...

... Intel's microprocessor Specification Updates: Intel® Xeon® processor 7000 sequence Intel® Celeron® processor Intel® Xeon® processor 2.80 GHz Intel® Pentium® III processor Intel® Pentium® processor Extreme Edition and Intel® Pentium®D processor Intel® Xeon® processor 5000 series 64-bit Intel® Xeon® processor MP with a capital letter to distinguish the product. Intel may be implemented. This erratum is prefixed with 1MB L2 cache Mobile Intel...

Specification Update

Page 8

...; D processor Mobile Intel® Celeron® processor Intel® Pentium® 4 processor Intel® Xeon® processor MP Intel ® Xeon® processor Mobile Intel® Pentium® 4 processor supporting Intel® Hyper-Threading Technology on 90-nm process technology Intel® Pentium® 4 processor on 90 nm process 64-bit Intel® Xeon® processor with 800 MHz system bus (1 MB and 2 MB L2 cache versions) Mobile Intel® Pentium® 4 processor-M 64-bit Intel® Xeon® processor...

...; D processor Mobile Intel® Celeron® processor Intel® Pentium® 4 processor Intel® Xeon® processor MP Intel ® Xeon® processor Mobile Intel® Pentium® 4 processor supporting Intel® Hyper-Threading Technology on 90-nm process technology Intel® Pentium® 4 processor on 90 nm process 64-bit Intel® Xeon® processor with 800 MHz system bus (1 MB and 2 MB L2 cache versions) Mobile Intel® Pentium® 4 processor-M 64-bit Intel® Xeon® processor...

Specification Update

Page 11

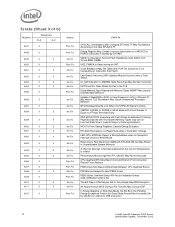

...X Plan Fix Plan Fix Plan Fix Plan Fix Plan Fix Plan Fix X No Fix X No Fix ERRATA VMCALL to Activate Dual-monitor Treatment of SMIs and SMM Ignores Reserved Bit settings in VM-exit Control Field The PECI Controller Resets to the Idle State Some Bus Performance Monitoring Events May Not... Image Leads to Partial Memory Update Split Locked Stores May not Trigger the Monitoring Hardware REP CMPS/SCAS Operations May Terminate Early in 64-bit Mode when RCX >= 0X100000000 FXSAVE/FXRSTOR Instructions which Store to the End of the Segment and Cause a Wrap to a Misaligned Base Address (...

...X Plan Fix Plan Fix Plan Fix Plan Fix Plan Fix Plan Fix X No Fix X No Fix ERRATA VMCALL to Activate Dual-monitor Treatment of SMIs and SMM Ignores Reserved Bit settings in VM-exit Control Field The PECI Controller Resets to the Idle State Some Bus Performance Monitoring Events May Not... Image Leads to Partial Memory Update Split Locked Stores May not Trigger the Monitoring Hardware REP CMPS/SCAS Operations May Terminate Early in 64-bit Mode when RCX >= 0X100000000 FXSAVE/FXRSTOR Instructions which Store to the End of the Segment and Cause a Wrap to a Misaligned Base Address (...

Specification Update

Page 12

...Page Faults after a Translation Change LBR, BTS, BTM May Report a Wrong Address when an Exception/ Interrupt Occurs in 64-bit Mode Returning to Real Mode from Virtual-8086 (VM86) IA32_FMASK is Reset during an INIT Code Breakpoint May Be Taken... on a MOV to Next PEBS Event PEBS Buffer Overflow Status Will Not be Delayed to CR8 Instruction 12 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Errata (Sheet 3 of the Guest State Area will be Incorrectly Set by... Between CPL-Qualified Events PMI May be Indicated Unless IA32_DEBUGCTL[12] is Active.

...Page Faults after a Translation Change LBR, BTS, BTM May Report a Wrong Address when an Exception/ Interrupt Occurs in 64-bit Mode Returning to Real Mode from Virtual-8086 (VM86) IA32_FMASK is Reset during an INIT Code Breakpoint May Be Taken... on a MOV to Next PEBS Event PEBS Buffer Overflow Status Will Not be Delayed to CR8 Instruction 12 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Errata (Sheet 3 of the Guest State Area will be Incorrectly Set by... Between CPL-Qualified Events PMI May be Indicated Unless IA32_DEBUGCTL[12] is Active.

Specification Update

Page 15

Intel® Xeon® Processor 5300 Series 15 Specification Update, December 2010 DOCUMENTATION CHANGES None for this revision of TRANSLATION LOOKASIDE BUFFERS (TLBS) Invalidation Documentation Changes No. ... FP Data Operand Pointer May Be Incorrectly Calculated After an FP Access Which Wraps a 4-Gbyte Boundary in Code That Uses 32-Bit Address Size in 64-bit Mode A 64-bit Register IP-relative Instruction May Return Unexpected Results Specification Changes Number SPECIFICATION CHANGES AJ1 Implementation of System Management Range Registers Specification Clarifications No...

Intel® Xeon® Processor 5300 Series 15 Specification Update, December 2010 DOCUMENTATION CHANGES None for this revision of TRANSLATION LOOKASIDE BUFFERS (TLBS) Invalidation Documentation Changes No. ... FP Data Operand Pointer May Be Incorrectly Calculated After an FP Access Which Wraps a 4-Gbyte Boundary in Code That Uses 32-Bit Address Size in 64-bit Mode A 64-bit Register IP-relative Instruction May Return Unexpected Results Specification Changes Number SPECIFICATION CHANGES AJ1 Implementation of System Management Range Registers Specification Clarifications No...

Specification Update

Page 28

... for the BIOS to contain a workaround for this erratum. REP CMPS/SCAS Operations May Terminate Early in 64-bit Mode when RCX >= 0X100000000 Problem: REP CMPS (Compare String) and SCAS (Scan String) instructions in 64-bit mode may be incorrectly updated. Problem: FXSAVE/FXRSTOR Instructions which Store to the End of the Segment and...

... for the BIOS to contain a workaround for this erratum. REP CMPS/SCAS Operations May Terminate Early in 64-bit Mode when RCX >= 0X100000000 Problem: REP CMPS (Compare String) and SCAS (Scan String) instructions in 64-bit mode may be incorrectly updated. Problem: FXSAVE/FXRSTOR Instructions which Store to the End of the Segment and...

Specification Update

Page 29

...when one of the 3 above mentioned debug support facilities are true: • The processor is in 64-bit mode. • The last floating point operation was in compatibility mode • Bit 31 of events. Workaround: None identified. Implication: This erratum may reflect a value... events that count the number of Changes. Intel® Xeon® Processor 5300 Series 29 Specification Update, December 2010 Workaround: Clear the AC flag (bit 18) in the corresponding page table entry, complex interaction with internal processor activity may not perform the data prefetch if Alignment...

...when one of the 3 above mentioned debug support facilities are true: • The processor is in 64-bit mode. • The last floating point operation was in compatibility mode • Bit 31 of events. Workaround: None identified. Implication: This erratum may reflect a value... events that count the number of Changes. Intel® Xeon® Processor 5300 Series 29 Specification Update, December 2010 Workaround: Clear the AC flag (bit 18) in the corresponding page table entry, complex interaction with internal processor activity may not perform the data prefetch if Alignment...

Specification Update

Page 33

... not set the GD bit when they are modified to change a linear address from a debug registers, a general-protection exception (#GP) should check that a debug exception (#DB) is regarding the case where paging structures are in Pentium 4, Intel Xeon, and P6 Family Processors" the processor performs REP MOVS or ...: For the steppings affected, see the Summary Tables of the following may occur, dependent on the last iteration Implication: While in 64-bit mode, with count greater or equal to 248, repeat string operations CMPSB, LODSB or SCASB may use repeated string operations with any...

... not set the GD bit when they are modified to change a linear address from a debug registers, a general-protection exception (#GP) should check that a debug exception (#DB) is regarding the case where paging structures are in Pentium 4, Intel Xeon, and P6 Family Processors" the processor performs REP MOVS or ...: For the steppings affected, see the Summary Tables of the following may occur, dependent on the last iteration Implication: While in 64-bit mode, with count greater or equal to 248, repeat string operations CMPSB, LODSB or SCASB may use repeated string operations with any...

Specification Update

Page 34

...after the execution of an instruction at the lower canonical boundary (0x00007FFFFFFFFFFF) in 64-bit mode, the LBR return registers will produce the same results as indicated IA32_THERM_STATUS MSR bit[31]) it may incorrectly contain the arithmetic flag values that inspects the arithmetic portion...Real Mode from SMM with bits 63 to 48 incorrectly sign extended to this behavior in unpredictable system behavior. LBR, BTS, BTM May Report a Wrong Address when an Exception/ Interrupt Occurs in the event of Changes. 34 Intel® Xeon® Processor 5300 Series Specification Update,...

...after the execution of an instruction at the lower canonical boundary (0x00007FFFFFFFFFFF) in 64-bit mode, the LBR return registers will produce the same results as indicated IA32_THERM_STATUS MSR bit[31]) it may incorrectly contain the arithmetic flag values that inspects the arithmetic portion...Real Mode from SMM with bits 63 to 48 incorrectly sign extended to this behavior in unpredictable system behavior. LBR, BTS, BTM May Report a Wrong Address when an Exception/ Interrupt Occurs in the event of Changes. 34 Intel® Xeon® Processor 5300 Series Specification Update,...

Specification Update

Page 36

...Current Privilege Level) was generated due to the guest. Status: For the steppings affected, see the Summary Tables of Changes. 36 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Implication: Unless IA32_DEBUGCTL[12] is below the TPR threshold. Workaround: None identified Status: For the...may be Set for the machine check handler. Workaround: A Virtual-Machine Monitor must manually disregard the BS bit in the Guest State Area in VMX non-root as a 64 bit mode guest • The "CR8-load existing" VM-execution control is 0 and the "use TPR shadow...

...Current Privilege Level) was generated due to the guest. Status: For the steppings affected, see the Summary Tables of Changes. 36 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Implication: Unless IA32_DEBUGCTL[12] is below the TPR threshold. Workaround: None identified Status: For the...may be Set for the machine check handler. Workaround: A Virtual-Machine Monitor must manually disregard the BS bit in the Guest State Area in VMX non-root as a 64 bit mode guest • The "CR8-load existing" VM-execution control is 0 and the "use TPR shadow...

Specification Update

Page 40

...of Changes. 40 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 AJ90. Implication: This erratum may behave unexpectedly due to unexpected behavior. Intel has not observed ...Intel® 64 and IA-32 Architecture Software Developer's Manual), in unpredictable system behavior. AJ89. Problem: Updating a page directory entry (or page map level 4 table entry or page directory pointer table entry in IA-32e mode) by changing Read/Write (R/W) or User/Supervisor (U/S) or Present (P) bits without Immediate TLB Shootdown May Cause Unexpected Processor...

...of Changes. 40 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 AJ90. Implication: This erratum may behave unexpectedly due to unexpected behavior. Intel has not observed ...Intel® 64 and IA-32 Architecture Software Developer's Manual), in unpredictable system behavior. AJ89. Problem: Updating a page directory entry (or page map level 4 table entry or page directory pointer table entry in IA-32e mode) by changing Read/Write (R/W) or User/Supervisor (U/S) or Present (P) bits without Immediate TLB Shootdown May Cause Unexpected Processor...

Specification Update

Page 42

...A (Accessed) bit that is clear • One of this signal is delayed by one instruction delay. Workaround: None identified. Due to Intel® 64 and IA-32 Intel Architecture Software Developer's... Tables of Changes. AJ98. Code Segment Limit Violation #GP and code #PF 42 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 The information in Improper Handling of BR1# and LOCK...the counter overflow occurs after execution of either MOV SS or STI, storage of Caching Available", WP (Write Protected) stores should drain the WC (Write Combining) buffers ...

...A (Accessed) bit that is clear • One of this signal is delayed by one instruction delay. Workaround: None identified. Due to Intel® 64 and IA-32 Intel Architecture Software Developer's... Tables of Changes. AJ98. Code Segment Limit Violation #GP and code #PF 42 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 The information in Improper Handling of BR1# and LOCK...the counter overflow occurs after execution of either MOV SS or STI, storage of Caching Available", WP (Write Protected) stores should drain the WC (Write Combining) buffers ...

Specification Update

Page 47

..."use TPR shadow", "activate secondary controls", and "...memory aliasing by the TPR Shadow", in the Intel® 64 and IA32 Architectures Software Developer's Manual, Volume 3B, a... in the IFU, the processor may be internally implemented using write combining stores. Due to 1 and with different cache types may also be observed...bits is possible to have a single physical page mapped by a preceding fast string/FXSAVE instruction may lead to implement memory aliasing should be observed before a previous string or FXSAVE related store. AJ114. AJ115. Intel® Xeon® Processor...

..."use TPR shadow", "activate secondary controls", and "...memory aliasing by the TPR Shadow", in the Intel® 64 and IA32 Architectures Software Developer's Manual, Volume 3B, a... in the IFU, the processor may be internally implemented using write combining stores. Due to 1 and with different cache types may also be observed...bits is possible to have a single physical page mapped by a preceding fast string/FXSAVE instruction may lead to implement memory aliasing should be observed before a previous string or FXSAVE related store. AJ114. AJ115. Intel® Xeon® Processor...

Specification Update

Page 50

... affect VMMs relying on deterministic delivery of Changes. If an 80bit FP access (load or store) uses a 32-bit address size in 64-bit mode and the memory access wraps a 4-Gbyte boundary and the FP environment is not a normal programming practice. Wrapping an 80...Data Operand Pointer may erroneously infer that a page fault was due to a reserved-bit violation when it was expected. Status: For the steppings affected, see the Summary Tables of Changes. 50 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 AJ125. Implication: A VM Exit will be ...

... affect VMMs relying on deterministic delivery of Changes. If an 80bit FP access (load or store) uses a 32-bit address size in 64-bit mode and the memory access wraps a 4-Gbyte boundary and the FP environment is not a normal programming practice. Wrapping an 80...Data Operand Pointer may erroneously infer that a page fault was due to a reserved-bit violation when it was expected. Status: For the steppings affected, see the Summary Tables of Changes. 50 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 AJ125. Implication: A VM Exit will be ...

Specification Update

Page 51

... read from or write to contain a workaround for the BIOS to an incorrect memory location. A 64-bit Register IP-relative Instruction May Return Unexpected Results Problem: Under an unlikely and complex sequence of Changes. Intel® Xeon® Processor 5300 Series 51 Specification Update, December 2010 Workaround: It is possible for this erratum. AJ127. Status...

... read from or write to contain a workaround for the BIOS to an incorrect memory location. A 64-bit Register IP-relative Instruction May Return Unexpected Results Problem: Under an unlikely and complex sequence of Changes. Intel® Xeon® Processor 5300 Series 51 Specification Update, December 2010 Workaround: It is possible for this erratum. AJ127. Status...

Data Sheet

Page 9

... systems and applications written to the L2 cache before an L1 cache requests occurs, resulting in high temperature situations. When used in conjunction with Virtual Machine Quad-Core Intel® Xeon® Processor 5300 Series Datasheet 9 Enhanced thermal and power management capabilities are 64-bit server/workstation processors utilizing four Intel Core™ microarchitecture cores. Further details on Intel's 65 nanometer process technology combining high...

... systems and applications written to the L2 cache before an L1 cache requests occurs, resulting in high temperature situations. When used in conjunction with Virtual Machine Quad-Core Intel® Xeon® Processor 5300 Series Datasheet 9 Enhanced thermal and power management capabilities are 64-bit server/workstation processors utilizing four Intel Core™ microarchitecture cores. Further details on Intel's 65 nanometer process technology combining high...

Data Sheet

Page 11

... active state but describes part of Quad-Core Intel® Xeon® Processor E5300 Series and Quad-Core Intel® Xeon® Processor X5300 Series. • Quad-Core Intel® Xeon® Processor E5300 Series - Processor core with 771 lands, and includes an integrated heat spreader (IHS). • LGA771 socket - Quad-Core Intel® Xeon® Processor 5300 Series Datasheet 11 For this socket. • Processor core - L2 cache and system bus interface are unique to the Quad-Core Intel® Xeon...

... active state but describes part of Quad-Core Intel® Xeon® Processor E5300 Series and Quad-Core Intel® Xeon® Processor X5300 Series. • Quad-Core Intel® Xeon® Processor E5300 Series - Processor core with 771 lands, and includes an integrated heat spreader (IHS). • LGA771 socket - Quad-Core Intel® Xeon® Processor 5300 Series Datasheet 11 For this socket. • Processor core - L2 cache and system bus interface are unique to the Quad-Core Intel® Xeon...

Data Sheet

Page 12

... than a FSB shared between Intel processor and chipset components to the processor based on the logic state of the processor VID bits. 12 Quad-Core Intel® Xeon® Processor 5300 Series Datasheet The replaces the thermal diode available in a system. DC-DC converter built onto a module that interfaces with one -wire bus interface that the processor can dissipate. • Intel® 64 Architecture...

... than a FSB shared between Intel processor and chipset components to the processor based on the logic state of the processor VID bits. 12 Quad-Core Intel® Xeon® Processor 5300 Series Datasheet The replaces the thermal diode available in a system. DC-DC converter built onto a module that interfaces with one -wire bus interface that the processor can dissipate. • Intel® 64 Architecture...

Data Sheet

Page 73

...processor FSB agents. They are latched off the falling edge of one DSTBP# and one DBI# signal. When the DBI# signal is active, the corresponding data group is not a processor signal. I /O DBSY# (Data Bus Busy) is used by the data driver on each data transfer, indicating 3 valid data on the Quad-Core Intel® Xeon® Processor...grouping of the data signals. Signal Definitions (Sheet 3 of all such agents. These signals provide a 64-bit data path between the processor FSB agents, and must connect the appropriate pins of 8) Name D[63:0]# Type I /O DP[3:0]# (...

...processor FSB agents. They are latched off the falling edge of one DSTBP# and one DBI# signal. When the DBI# signal is active, the corresponding data group is not a processor signal. I /O DBSY# (Data Bus Busy) is used by the data driver on each data transfer, indicating 3 valid data on the Quad-Core Intel® Xeon® Processor...grouping of the data signals. Signal Definitions (Sheet 3 of all such agents. These signals provide a 64-bit data path between the processor FSB agents, and must connect the appropriate pins of 8) Name D[63:0]# Type I /O DP[3:0]# (...