Specification Update

Page 1

..., Intel® Virtualization Technology± and Intel® Trusted Execution Technologyŧ December 2010 Notice: The Intel® CoreTM2 Extreme and Intel® CoreTM2 Duo desktop processor may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Document Number: 313279-027 on 65 nm Process in this Specification Update. Intel® Core™2 Extreme Processor X6800Δ and Intel® Core...

..., Intel® Virtualization Technology± and Intel® Trusted Execution Technologyŧ December 2010 Notice: The Intel® CoreTM2 Extreme and Intel® CoreTM2 Duo desktop processor may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Document Number: 313279-027 on 65 nm Process in this Specification Update. Intel® Core™2 Extreme Processor X6800Δ and Intel® Core...

Specification Update

Page 2

...; Intel® Virtualization Technology requires a computer system with a processor, chipset, BIOS, operating system, device drivers, and applications enabled for conflicts or incompatibilities arising from published specifications. Processor numbers differentiate features within each processor family, not across different processor families. Intel reserves these for future definition and shall have no responsibility whatsoever for Intel 64. Check with Execute Disable Bit capability and a supporting operating system. Performance...

...; Intel® Virtualization Technology requires a computer system with a processor, chipset, BIOS, operating system, device drivers, and applications enabled for conflicts or incompatibilities arising from published specifications. Processor numbers differentiate features within each processor family, not across different processor families. Intel reserves these for future definition and shall have no responsibility whatsoever for Intel 64. Check with Execute Disable Bit capability and a supporting operating system. Performance...

Specification Update

Page 4

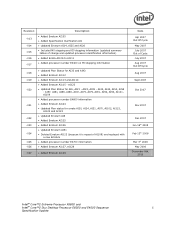

... Cycle Feb 2007 Mar 2007 Apr 2007 Apr 2007 Out Of Cycle 4 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update AI94 • Added L step information • Added processor number E4300 information • Updated Erratum AI70 • Added Erratum AI95-AI97 • Updated Component Identification information table • Added Erratum AI98 - AI90 • Corrected...

... Cycle Feb 2007 Mar 2007 Apr 2007 Apr 2007 Out Of Cycle 4 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update AI94 • Added L step information • Added processor number E4300 information • Updated Erratum AI70 • Added Erratum AI95-AI97 • Updated Component Identification information table • Added Erratum AI98 - AI90 • Corrected...

Specification Update

Page 5

... 2008 Mar 3rd 2008 May 2008 December 8th, 2010 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 5 Specification Update AI23, AI38 - AI57, AI61, AI66, AI69, AI72, AI75, AI79, AI91, AI92, AI94, AI101, AI109 • Added processor number E4600 information • Added Erratum AI124 • Updated Plan status for errata AI20, AI24, AI31, AI70...

... 2008 Mar 3rd 2008 May 2008 December 8th, 2010 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 5 Specification Update AI23, AI38 - AI57, AI61, AI66, AI69, AI72, AI75, AI79, AI91, AI92, AI94, AI101, AI109 • Added processor number E4600 information • Added Erratum AI124 • Updated Plan status for errata AI20, AI24, AI31, AI70...

Specification Update

Page 6

... specifications contained in the documents listed in other documents. Affected Documents Document Title Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Datasheet Document Number 313278-008 Related Documents Document Title Intel® 64 and IA-32 Architectures Software Developer's Manual Volume 1: Basic Architecture Intel® 64 and IA-32 Architectures Software Developer's Manual Volume 2A: Instruction Set...

... specifications contained in the documents listed in other documents. Affected Documents Document Title Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Datasheet Document Number 313278-008 Related Documents Document Title Intel® 64 and IA-32 Architectures Software Developer's Manual Volume 1: Basic Architecture Intel® 64 and IA-32 Architectures Software Developer's Manual Volume 2A: Instruction Set...

Specification Update

Page 7

... product specification or user documentation (datasheets, manuals, etc.). § Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 7 Specification Update Note: Errata remain in the processor identification information table. These changes will be incorporated in the next release of the specifications. Under these parts can range from mechanical only to distinguish between engineering samples. The NDA specification update has a processor identification...

... product specification or user documentation (datasheets, manuals, etc.). § Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 7 Specification Update Note: Errata remain in the processor identification information table. These changes will be incorporated in the next release of the specifications. Under these parts can range from mechanical only to distinguish between engineering samples. The NDA specification update has a processor identification...

Specification Update

Page 8

... Changes Summary Tables of Changes The following notations: Codes Used in Summary Table Stepping X: Erratum, Specification Change or Clarification that will be fixed in a future stepping of the document. 8 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update This table uses the following table indicates the Specification Changes, Errata, Specification Clarifications or Documentation Changes, which apply to...

... Changes Summary Tables of Changes The following notations: Codes Used in Summary Table Stepping X: Erratum, Specification Change or Clarification that will be fixed in a future stepping of the document. 8 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update This table uses the following table indicates the Specification Changes, Errata, Specification Clarifications or Documentation Changes, which apply to...

Specification Update

Page 9

... Dual-Core Intel® Xeon® processor 2.80 GHz Intel® Pentium® III processor Intel® Pentium® processor Extreme Edition and Intel® Pentium® D processor Dual-Core Intel® Xeon® processor 5000 series 64-bit Intel® Xeon® processor MP with 1MB L2 cache Mobile Intel® Pentium® III processor Intel® Celeron® D processor Mobile Intel® Celeron® processor Intel® Pentium® 4 processor Intel® Xeon® processor MP Intel ® Xeon® processor Mobile Intel® Pentium® 4 processor supporting Hyper...

... Dual-Core Intel® Xeon® processor 2.80 GHz Intel® Pentium® III processor Intel® Pentium® processor Extreme Edition and Intel® Pentium® D processor Dual-Core Intel® Xeon® processor 5000 series 64-bit Intel® Xeon® processor MP with 1MB L2 cache Mobile Intel® Pentium® III processor Intel® Celeron® D processor Mobile Intel® Celeron® processor Intel® Pentium® 4 processor Intel® Xeon® processor MP Intel ® Xeon® processor Mobile Intel® Pentium® 4 processor supporting Hyper...

Specification Update

Page 10

... Intel® Core™2 Duo Processor and Intel® Core™2 Extreme Processor on 45-nm Process Quad-Core Intel® Xeon® processor 3300 series Dual-Core Intel® Xeon® E3110 Processor Intel® Celeron® dual-core processor E1000 series Intel® Core™2 Extreme Processor QX9775Δ Intel® Atom™ processor Z5xx series The Specification Updates for the Pentium® processor, Pentium® Pro processor, and other Intel products do not use this convention. Summary Tables of a #GP Fault 10 Intel® Core™2 Extreme Processor X6800...

... Intel® Core™2 Duo Processor and Intel® Core™2 Extreme Processor on 45-nm Process Quad-Core Intel® Xeon® processor 3300 series Dual-Core Intel® Xeon® E3110 Processor Intel® Celeron® dual-core processor E1000 series Intel® Core™2 Extreme Processor QX9775Δ Intel® Atom™ processor Z5xx series The Specification Updates for the Pentium® processor, Pentium® Pro processor, and other Intel products do not use this convention. Summary Tables of a #GP Fault 10 Intel® Core™2 Extreme Processor X6800...

Specification Update

Page 11

... IA-32e Mode AI29 X X X X X No Fix #GP Fault is Not Generated on Writing IA32_MISC_ENABLE [34] When Execute Disable Bit is Not Supported AI30 X X Fixed (E)CX May Get Incorrectly Updated When Performing Fast String REP MOVS or Fast String REP STOS With Large Data Structures Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 11 Specification Update

... IA-32e Mode AI29 X X X X X No Fix #GP Fault is Not Generated on Writing IA32_MISC_ENABLE [34] When Execute Disable Bit is Not Supported AI30 X X Fixed (E)CX May Get Incorrectly Updated When Performing Fast String REP MOVS or Fast String REP STOS With Large Data Structures Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 11 Specification Update

Specification Update

Page 12

... NO B1 B2 L2 M0 G0 Plan ERRATA AI31 X X X X Fixed Performance Monitoring Events for Retired Loads (CBH) and Instructions Retired (C0H) May Not Be Accurate AI32 X X X X X No Fix Upper 32 bits of 'From' Address Reported through BTMs or BTSs May be Incorrect AI33 X X X Fixed Unsynchronized Cross-Modifying Code Operations Can Cause Unexpected Instruction Execution Results MSRs...

... NO B1 B2 L2 M0 G0 Plan ERRATA AI31 X X X X Fixed Performance Monitoring Events for Retired Loads (CBH) and Instructions Retired (C0H) May Not Be Accurate AI32 X X X X X No Fix Upper 32 bits of 'From' Address Reported through BTMs or BTSs May be Incorrect AI33 X X X Fixed Unsynchronized Cross-Modifying Code Operations Can Cause Unexpected Instruction Execution Results MSRs...

Specification Update

Page 13

... Buffer Overflow Status Will Not be Set for Non-Single-Step #DB Exception Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 13 Specification Update AI60 X X X X X No Fix MOV To/From Debug Registers Causes Debug Exception AI61 X X X X Fixed Debug Register May Contain Incorrect Information on a MOVSS or POPSS Instruction Followed by SYSRET AI62 X X X X X No...

... Buffer Overflow Status Will Not be Set for Non-Single-Step #DB Exception Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 13 Specification Update AI60 X X X X X No Fix MOV To/From Debug Registers Causes Debug Exception AI61 X X X X Fixed Debug Register May Contain Incorrect Information on a MOVSS or POPSS Instruction Followed by SYSRET AI62 X X X X X No...

Specification Update

Page 14

..., CR4 and the EXF4 Signal May be Incorrect after Shutdown AI94 X X X X Fixed Performance Monitoring Counter MACRO_INSTS.DECODED May Not Count Some Decoded Instructions AI95 X X X X Fixed The Stack Size May be Incorrect as a Result of VIP/VIF Check on SYSEXIT and SYSRET 14 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update

..., CR4 and the EXF4 Signal May be Incorrect after Shutdown AI94 X X X X Fixed Performance Monitoring Counter MACRO_INSTS.DECODED May Not Count Some Decoded Instructions AI95 X X X X Fixed The Stack Size May be Incorrect as a Result of VIP/VIF Check on SYSEXIT and SYSRET 14 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update

Specification Update

Page 21

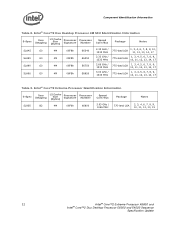

... LGA 1, 3, 4, 6, 7, 8, 9, 10, 11, 12, 13, 15 775-land LGA 1, 3, 4, 6, 7, 8, 9, 10, 11, 12, 13, 16 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 21 Specification Update Component Identification Information Table 1. Intel® Core™2 Duo Desktop Processor 2M SKU Identification Information S-Spec Core Stepping L2 Cache Size (bytes) Processor Signature Processor Number SL9SA B2 2M 06F6h E6300 SL9S9 B2 2M 06F6h E6400 SL9TB...

... LGA 1, 3, 4, 6, 7, 8, 9, 10, 11, 12, 13, 15 775-land LGA 1, 3, 4, 6, 7, 8, 9, 10, 11, 12, 13, 16 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 21 Specification Update Component Identification Information Table 1. Intel® Core™2 Duo Desktop Processor 2M SKU Identification Information S-Spec Core Stepping L2 Cache Size (bytes) Processor Signature Processor Number SL9SA B2 2M 06F6h E6300 SL9S9 B2 2M 06F6h E6400 SL9TB...

Specification Update

Page 22

... S-Spec Core Stepping L2 Cache Size (bytes) Processor Signature Processor Number SL9S5 B2 4M 06F6h X6800 Speed Core/Bus 2.93 GHz / 1066 MHz Package 775-land LGA Notes 2, 3, 4, 6, 7, 8, 9, 10, 11, 12, 13, 15 22 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update Intel® Core™2 Duo Desktop Processor 4M SKU Identification Information S-Spec SLAA5 SLA9X SLA9V SLA9U Core Stepping L2 Cache Size (bytes) Processor Signature Processor Number G0 4M 06FBh E6540 G0 4M 06FBh...

... S-Spec Core Stepping L2 Cache Size (bytes) Processor Signature Processor Number SL9S5 B2 4M 06F6h X6800 Speed Core/Bus 2.93 GHz / 1066 MHz Package 775-land LGA Notes 2, 3, 4, 6, 7, 8, 9, 10, 11, 12, 13, 15 22 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update Intel® Core™2 Duo Desktop Processor 4M SKU Identification Information S-Spec SLAA5 SLA9X SLA9V SLA9U Core Stepping L2 Cache Size (bytes) Processor Signature Processor Number G0 4M 06FBh E6540 G0 4M 06FBh...

Specification Update

Page 23

... or software. Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 23 Specification Update Implication: An interrupt may occur. Workaround: None identified. If there is set in the in MCi_ADDR, for Single-bit L2 ECC errors. The ISR associated with the new vector when a LVT entry is pipelined on Single-bit L2 ECC Errors May be used when writing the...

... or software. Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 23 Specification Update Implication: An interrupt may occur. Workaround: None identified. If there is set in the in MCi_ADDR, for Single-bit L2 ECC errors. The ISR associated with the new vector when a LVT entry is pipelined on Single-bit L2 ECC Errors May be used when writing the...

Specification Update

Page 25

...: Software may be preempted by the operating system and the instruction retried, a #GP fault will occur. Workaround: None identified. Implication: Operation systems that are resolved by another lower priority fault (e.g. Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 25 Specification Update However, if the preempting lower priority faults are pending prior...

...: Software may be preempted by the operating system and the instruction retried, a #GP fault will occur. Workaround: None identified. Implication: Operation systems that are resolved by another lower priority fault (e.g. Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 25 Specification Update However, if the preempting lower priority faults are pending prior...

Specification Update

Page 37

... the Core 1. Workaround: Clear the AC flag (bit 18) in compatibility mode • Bit 31 of the FPU Data (Operand) Pointer is set to all 1's instead of the expected value of all 0's in the FXSAVE memory image if all of Changes. Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 37 Specification Update Status: For the steppings affected...

... the Core 1. Workaround: Clear the AC flag (bit 18) in compatibility mode • Bit 31 of the FPU Data (Operand) Pointer is set to all 1's instead of the expected value of all 0's in the FXSAVE memory image if all of Changes. Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 37 Specification Update Status: For the steppings affected...

Specification Update

Page 38

... immediately after an Exit from SMM Problem: After a return from SMM (System Management Mode), the CPU will also be used . Concurrent Multi-processor Writes to Non-dirty Page May Result in the package may not be unexpectedly disabled. 38 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update Implication: The value of Changes.

... immediately after an Exit from SMM Problem: After a return from SMM (System Management Mode), the CPU will also be used . Concurrent Multi-processor Writes to Non-dirty Page May Result in the package may not be unexpectedly disabled. 38 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update Implication: The value of Changes.

Specification Update

Page 51

...-execution control is used to the Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3A, section "Buffering of one thread while another thread performs a cacheable write operation to the same address, the data stored may Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 51 Specification Update Status: For the steppings affected, see the...

...-execution control is used to the Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3A, section "Buffering of one thread while another thread performs a cacheable write operation to the same address, the data stored may Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 51 Specification Update Status: For the steppings affected, see the...