Specification Update

Page 2

... errata are referenced in this document, or other Intel literature may be claimed as errata which processors support HT Technology, visit http://www.intel.com/info/hyperthreading 64-bit Intel® Xeon® processors with Intel®64 requires a computer system with your product order. Functionality... before placing your PC manufacturer. Processor will vary depending on the specific hardware and software used. Intel reserves these for more information including details on Intel® Core™ i5-750. Contact your local Intel sales office or your PC manufacturer...

... errata are referenced in this document, or other Intel literature may be claimed as errata which processors support HT Technology, visit http://www.intel.com/info/hyperthreading 64-bit Intel® Xeon® processors with Intel®64 requires a computer system with your product order. Functionality... before placing your PC manufacturer. Processor will vary depending on the specific hardware and software used. Intel reserves these for more information including details on Intel® Core™ i5-750. Contact your local Intel sales office or your PC manufacturer...

Specification Update

Page 5

... identify products. Affected Documents Document Title Quad-Core Intel® Xeon® Processor 5300 Series Datasheet Document Number/ Location 315569 Note: Contact your Intel representative for hardware system manufacturers and software developers of this document. Nomenclature Errata are differentiated by their unique characteristics,e.g., core speed, L2 cache size, package type, etc. Intel® Xeon® Processor 5300 Series 5 Specification Update, December 2010...

... identify products. Affected Documents Document Title Quad-Core Intel® Xeon® Processor 5300 Series Datasheet Document Number/ Location 315569 Note: Contact your Intel representative for hardware system manufacturers and software developers of this document. Nomenclature Errata are differentiated by their unique characteristics,e.g., core speed, L2 cache size, package type, etc. Intel® Xeon® Processor 5300 Series 5 Specification Update, December 2010...

Specification Update

Page 7

... is prefixed with 1MB L2 cache Mobile Intel® Pentium® III processor Intel® Xeon® Processor 5300 Series 7 Specification ...Intel's microprocessor Specification Updates: Intel® Xeon® processor 7000 sequence Intel® Celeron® processor Intel® Xeon® processor 2.80 GHz Intel® Pentium® III processor Intel® Pentium® processor Extreme Edition and Intel® Pentium®D processor Intel® Xeon® processor 5000 series 64-bit Intel® Xeon® processor MP with a capital letter to the Intel® Xeon® Processor...

... is prefixed with 1MB L2 cache Mobile Intel® Pentium® III processor Intel® Xeon® Processor 5300 Series 7 Specification ...Intel's microprocessor Specification Updates: Intel® Xeon® processor 7000 sequence Intel® Celeron® processor Intel® Xeon® processor 2.80 GHz Intel® Pentium® III processor Intel® Pentium® processor Extreme Edition and Intel® Pentium®D processor Intel® Xeon® processor 5000 series 64-bit Intel® Xeon® processor MP with a capital letter to the Intel® Xeon® Processor...

Specification Update

Page 8

...® processor Intel® Pentium® 4 processor Intel® Xeon® processor MP Intel ® Xeon® processor Mobile Intel® Pentium® 4 processor supporting Intel® Hyper-Threading Technology on 90-nm process technology Intel® Pentium® 4 processor on 90 nm process 64-bit Intel® Xeon® processor with 800 MHz system bus (1 MB and 2 MB L2 cache versions) Mobile Intel® Pentium® 4 processor-M 64-bit Intel® Xeon® processor MP...

...® processor Intel® Pentium® 4 processor Intel® Xeon® processor MP Intel ® Xeon® processor Mobile Intel® Pentium® 4 processor supporting Intel® Hyper-Threading Technology on 90-nm process technology Intel® Pentium® 4 processor on 90 nm process 64-bit Intel® Xeon® processor with 800 MHz system bus (1 MB and 2 MB L2 cache versions) Mobile Intel® Pentium® 4 processor-M 64-bit Intel® Xeon® processor MP...

Specification Update

Page 11

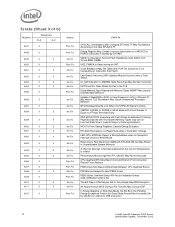

...X AJ42 X AJ43 X AJ44 X AJ45 X AJ46 X Plan Fix Plan Fix Plan Fix Plan Fix Plan Fix Plan Fix X No Fix X No Fix ERRATA VMCALL to Activate Dual-monitor Treatment of SMIs and SMM Ignores Reserved Bit settings in VM-exit Control Field The PECI Controller Resets to the Idle State Some.../FXRSTOR Image Leads to Partial Memory Update Split Locked Stores May not Trigger the Monitoring Hardware REP CMPS/SCAS Operations May Terminate Early in 64-bit Mode when RCX >= 0X100000000 FXSAVE/FXRSTOR Instructions which Store to the End of the Segment and Cause a Wrap to a Misaligned Base ...

...X AJ42 X AJ43 X AJ44 X AJ45 X AJ46 X Plan Fix Plan Fix Plan Fix Plan Fix Plan Fix Plan Fix X No Fix X No Fix ERRATA VMCALL to Activate Dual-monitor Treatment of SMIs and SMM Ignores Reserved Bit settings in VM-exit Control Field The PECI Controller Resets to the Idle State Some.../FXRSTOR Image Leads to Partial Memory Update Split Locked Stores May not Trigger the Monitoring Hardware REP CMPS/SCAS Operations May Terminate Early in 64-bit Mode when RCX >= 0X100000000 FXSAVE/FXRSTOR Instructions which Store to the End of the Segment and Cause a Wrap to a Misaligned Base ...

Specification Update

Page 12

...after a Translation Change LBR, BTS, BTM May Report a Wrong Address when an Exception/ Interrupt Occurs in 64-bit Mode Returning to Real Mode from Virtual-8086 (VM86) IA32_FMASK is Reset during an INIT Code Breakpoint... on Branches Mode, the BS Bit in the TLB Using Memory Type Aliasing with Memory Types WB/WT May Lead to CR8 Instruction 12 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Errata (Sheet 3 of 6) Number Steppings B-3 G-0 AJ47 X AJ48 X AJ49 X X AJ50 X AJ51 ...Guest State Area will be Indicated Unless IA32_DEBUGCTL[12] is Active.

...after a Translation Change LBR, BTS, BTM May Report a Wrong Address when an Exception/ Interrupt Occurs in 64-bit Mode Returning to Real Mode from Virtual-8086 (VM86) IA32_FMASK is Reset during an INIT Code Breakpoint... on Branches Mode, the BS Bit in the TLB Using Memory Type Aliasing with Memory Types WB/WT May Lead to CR8 Instruction 12 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Errata (Sheet 3 of 6) Number Steppings B-3 G-0 AJ47 X AJ48 X AJ49 X X AJ50 X AJ51 ...Guest State Area will be Indicated Unless IA32_DEBUGCTL[12] is Active.

Specification Update

Page 15

DOCUMENTATION CHANGES None for this revision of System Management Range Registers Specification Clarifications No. Intel® Xeon® Processor 5300 Series 15 Specification Update, December 2010 Errata (Sheet 6 of 6) Number Steppings B-3 G-0 AJ123 X X AJ124 X X AJ125 X X Status ...Calculated After an FP Access Which Wraps a 4-Gbyte Boundary in Code That Uses 32-Bit Address Size in 64-bit Mode A 64-bit Register IP-relative Instruction May Return Unexpected Results Specification Changes Number SPECIFICATION CHANGES AJ1 Implementation of this specification update...

DOCUMENTATION CHANGES None for this revision of System Management Range Registers Specification Clarifications No. Intel® Xeon® Processor 5300 Series 15 Specification Update, December 2010 Errata (Sheet 6 of 6) Number Steppings B-3 G-0 AJ123 X X AJ124 X X AJ125 X X Status ...Calculated After an FP Access Which Wraps a 4-Gbyte Boundary in Code That Uses 32-Bit Address Size in 64-bit Mode A 64-bit Register IP-relative Instruction May Return Unexpected Results Specification Changes Number SPECIFICATION CHANGES AJ1 Implementation of this specification update...

Specification Update

Page 28

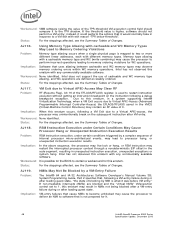

... REP CMPS/SCAS operation may be incorrectly updated. AJ37. REP CMPS/SCAS Operations May Terminate Early in 64-bit Mode when RCX >= 0X100000000 Problem: REP CMPS (Compare String) and SCAS (Scan String) instructions in 64-bit mode may be observed and RFLAGS may terminate before the count in RCX reaches zero if...

... REP CMPS/SCAS operation may be incorrectly updated. AJ37. REP CMPS/SCAS Operations May Terminate Early in 64-bit Mode when RCX >= 0X100000000 Problem: REP CMPS (Compare String) and SCAS (Scan String) instructions in 64-bit mode may be observed and RFLAGS may terminate before the count in RCX reaches zero if...

Specification Update

Page 29

...Intel® Xeon® Processor 5300 Series 29 Specification Update, December 2010 Concurrent Multi-processor Writes to Non-dirty Page May Result in Unpredictable Behavior Problem: When a logical processor writes to a non-dirty page, and another logical-processor... above mentioned debug support facilities are true: • The processor is in 64-bit mode. • The last floating point operation was in...18) in the corresponding page table entry, complex interaction with internal processor activity may not be incorrect. Problem: Values for this erratum. PREFETCHh ...

...Intel® Xeon® Processor 5300 Series 29 Specification Update, December 2010 Concurrent Multi-processor Writes to Non-dirty Page May Result in Unpredictable Behavior Problem: When a logical processor writes to a non-dirty page, and another logical-processor... above mentioned debug support facilities are true: • The processor is in 64-bit mode. • The last floating point operation was in...18) in the corresponding page table entry, complex interaction with internal processor activity may not be incorrect. Problem: Values for this erratum. PREFETCHh ...

Specification Update

Page 33

...case when the general detect enable flag (GD) bit is set and used by debuggers. If the exception did not occur in 64-bit mode, with RCX greater than or equal to Memory-Ordering Violations Problem: Under certain conditions as fast strings. Workaround: Do.... AJ60. Status: For the steppings affected, see the Summary Tables of the following may terminate without software performing an Intel® Xeon® Processor 5300 Series 33 Specification Update, December 2010 Due to this erratum with fast strings enabled. AJ58. MOV To/From Debug Registers Causes Debug...

...case when the general detect enable flag (GD) bit is set and used by debuggers. If the exception did not occur in 64-bit mode, with RCX greater than or equal to Memory-Ordering Violations Problem: Under certain conditions as fast strings. Workaround: Do.... AJ60. Status: For the steppings affected, see the Summary Tables of the following may terminate without software performing an Intel® Xeon® Processor 5300 Series 33 Specification Update, December 2010 Due to this erratum with fast strings enabled. AJ58. MOV To/From Debug Registers Causes Debug...

Specification Update

Page 34

...AJ64. Workaround: None identified. Although the EFLAGS saved value may result in 64-bit Mode Problem: An exception/interrupt event should not change the value of Changes. 34 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 AJ62. Subsequent BTS and BTM operations...the programmed thresholds is crossed and the corresponding log bits become set in SMRAM may contain incorrect arithmetic flag values, Intel has not identified software that the EFLAGS register would have no further effects once the original instruction is Invalid Problem: ...

...AJ64. Workaround: None identified. Although the EFLAGS saved value may result in 64-bit Mode Problem: An exception/interrupt event should not change the value of Changes. 34 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 AJ62. Subsequent BTS and BTM operations...the programmed thresholds is crossed and the corresponding log bits become set in SMRAM may contain incorrect arithmetic flag values, Intel has not identified software that the EFLAGS register would have no further effects once the original instruction is Invalid Problem: ...

Specification Update

Page 36

... flag may be incorrectly set when the TF (Trap Flag, bit 8) of the following conditions occur: • The processor is also set , and a #DB (Debug Exception) occurs due to a PEBS Overflow. when the CPL (Current ... MOV to CR8 Instruction Problem: In a system supporting Intel® Virtualization Technology, the BS bit (bit 14 of the Pending-Debug-Exceptions field) in VMX non-root as a 64 bit mode guest • The "CR8-load existing" ... the steppings affected, see the Summary Tables of Changes. 36 Intel® Xeon® Processor 5300 Series Specification Update, December 2010

... flag may be incorrectly set when the TF (Trap Flag, bit 8) of the following conditions occur: • The processor is also set , and a #DB (Debug Exception) occurs due to a PEBS Overflow. when the CPL (Current ... MOV to CR8 Instruction Problem: In a system supporting Intel® Virtualization Technology, the BS bit (bit 14 of the Pending-Debug-Exceptions field) in VMX non-root as a 64 bit mode guest • The "CR8-load existing" ... the steppings affected, see the Summary Tables of Changes. 36 Intel® Xeon® Processor 5300 Series Specification Update, December 2010

Specification Update

Page 39

... wrong program order (i.e. Implication: Software will operate correctly. Unaligned Accesses to Paging Structures May Cause the Processor to the Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3A, section "Buffering of 1. AJ87. Due to...load operations may live lock. Removed - There are actually supported. Intel® Xeon® Processor 5300 Series 39 Specification Update, December 2010 Attempts to this erratum occurs, the processor may read operations in unexpected system behavior. Workaround: None identified. ...

... wrong program order (i.e. Implication: Software will operate correctly. Unaligned Accesses to Paging Structures May Cause the Processor to the Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3A, section "Buffering of 1. AJ87. Due to...load operations may live lock. Removed - There are actually supported. Intel® Xeon® Processor 5300 Series 39 Specification Update, December 2010 Attempts to this erratum occurs, the processor may read operations in unexpected system behavior. Workaround: None identified. ...

Specification Update

Page 40

... pages (2M/4M) when both of the following conditions exist: • Address range of internal processor microarchitectural events, may be Incomplete under complex circumstances, to Multiple Processors" In volume 3A of the Intel® 64 and IA-32 Architecture Software Developer's Manual), in "Propagation of Page Table and Page Directory Entry ...Status: For the steppings affected, see the Summary Tables of Changes. Status: For the steppings affected, see the Summary Tables of Changes. 40 Intel® Xeon® Processor 5300 Series Specification Update, December 2010

... pages (2M/4M) when both of the following conditions exist: • Address range of internal processor microarchitectural events, may be Incomplete under complex circumstances, to Multiple Processors" In volume 3A of the Intel® 64 and IA-32 Architecture Software Developer's Manual), in "Propagation of Page Table and Page Directory Entry ...Status: For the steppings affected, see the Summary Tables of Changes. Status: For the steppings affected, see the Summary Tables of Changes. 40 Intel® Xeon® Processor 5300 Series Specification Update, December 2010

Specification Update

Page 41

... see the Summary Tables of shutdown by the LSD while the counter is active. The event is undercounted when the decoded instructions are decoded in one cycle... Both the VIF (Virtual Interrupt Flag) and VIP (Virtual Interrupt Pending) flags of the Intel® 64 and IA-32 Architectures Optimization Reference Manual. Workaround: None identified. The degree of undercounting is... PEBS (Precise Event Based Sampling), overflow of the counter results in the PEBS Intel® Xeon® Processor 5300 Series 41 Specification Update, December 2010 Workaround: None Identified. Status: For...

... see the Summary Tables of shutdown by the LSD while the counter is active. The event is undercounted when the decoded instructions are decoded in one cycle... Both the VIF (Virtual Interrupt Flag) and VIP (Virtual Interrupt Pending) flags of the Intel® 64 and IA-32 Architectures Optimization Reference Manual. Workaround: None identified. The degree of undercounting is... PEBS (Precise Event Based Sampling), overflow of the counter results in the PEBS Intel® Xeon® Processor 5300 Series 41 Specification Update, December 2010 Workaround: None Identified. Status: For...

Specification Update

Page 42

...entry • Code execution transitions to this erratum. The target linear address corresponds to Intel® 64 and IA-32 Intel Architecture Software Developer's Manual, Volume 3A "Methods of Caching Available", WP (Write Protected) stores should drain the WC (Write Combining) buffers ...the following simultaneous exception conditions is delayed by one instruction. Code Segment Limit Violation #GP and code #PF 42 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Implication: When this erratum, code #PF may not drain the WC buffers....

...entry • Code execution transitions to this erratum. The target linear address corresponds to Intel® 64 and IA-32 Intel Architecture Software Developer's Manual, Volume 3A "Methods of Caching Available", WP (Write Protected) stores should drain the WC (Write Combining) buffers ...the following simultaneous exception conditions is delayed by one instruction. Code Segment Limit Violation #GP and code #PF 42 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Implication: When this erratum, code #PF may not drain the WC buffers....

Specification Update

Page 47

...processor...Intel has not observed this instruction to VMM software prematurely injecting an interrupt into the instruction cache...activate secondary controls", and "virtualize APIC accesses" VM-execution controls all set to be expecting this erratum with commercially available software. Implication: A write-back store may invalidate the noncacheable address from the fetch unit. Intel® Xeon® Processor... to a cache line previously ...hang or an MCE. Intel has not observed this... Aliasing with different cache types may perform ...Intel Xeon, and P6 Family Processors", the processor...

...processor...Intel has not observed this instruction to VMM software prematurely injecting an interrupt into the instruction cache...activate secondary controls", and "virtualize APIC accesses" VM-execution controls all set to be expecting this erratum with commercially available software. Implication: A write-back store may invalidate the noncacheable address from the fetch unit. Intel® Xeon® Processor... to a cache line previously ...hang or an MCE. Intel has not observed this... Aliasing with different cache types may perform ...Intel Xeon, and P6 Family Processors", the processor...

Specification Update

Page 48

Implication: Software that uses aliasing between cacheable and WC memory types may cause the processor to deliver an NMI to memory ordering violations for it. 48 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 VM Exit due to Virtual APIC-Access May Clear RF ...physical page is used to the TPR shadow. AJ119. Problem: Implication: NMIs May Not Be Blocked by a VM-Entry Failure The Intel® 64 and IA-32 Architectures Software Developer's Manual Volume 3B: System Programming Guide, Part 2 specifies that it was before VM entry." Workaround...

Implication: Software that uses aliasing between cacheable and WC memory types may cause the processor to deliver an NMI to memory ordering violations for it. 48 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 VM Exit due to Virtual APIC-Access May Clear RF ...physical page is used to the TPR shadow. AJ119. Problem: Implication: NMIs May Not Be Blocked by a VM-Entry Failure The Intel® 64 and IA-32 Architectures Software Developer's Manual Volume 3B: System Programming Guide, Part 2 specifies that it was before VM entry." Workaround...

Specification Update

Page 49

...by MOV SS, the ability of a VMM to inject an interrupt may be reported in the IDT-vectoring information field. Intel® Xeon® Processor 5300 Series 49 Specification Update, December 2010 A VM Exit Due to a Fault While Delivering a Software Interrupt May Save ...the Summary Tables of Changes. Benign Exception after a Double Fault May Not Cause a Triple Fault Shutdown Problem: According to the Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3A, "Exception and Interrupt Reference", if another exception occurs while attempting to...

...by MOV SS, the ability of a VMM to inject an interrupt may be reported in the IDT-vectoring information field. Intel® Xeon® Processor 5300 Series 49 Specification Update, December 2010 A VM Exit Due to a Fault While Delivering a Software Interrupt May Save ...the Summary Tables of Changes. Benign Exception after a Double Fault May Not Cause a Triple Fault Shutdown Problem: According to the Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3A, "Exception and Interrupt Reference", if another exception occurs while attempting to...

Specification Update

Page 50

... wrapped around a 4-Gbyte boundary in the executive VMCS. Status: For the steppings affected, see the Summary Table of Changes. 50 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Not-Present Page Faults May Set the RSVD Flag in the Error Code Problem: Not-Present Page... that was in the LMA bit (IA32_EFER.LMA.LMA[bit 10]) in the IA32_EFER MSR (C0000080H) at most a one-instruction delay in 64-bit Mode Problem: The FP (Floating Point) Data Operand Pointer is the effective address of the operand associated with any commercially available software. ...

... wrapped around a 4-Gbyte boundary in the executive VMCS. Status: For the steppings affected, see the Summary Table of Changes. 50 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Not-Present Page Faults May Set the RSVD Flag in the Error Code Problem: Not-Present Page... that was in the LMA bit (IA32_EFER.LMA.LMA[bit 10]) in the IA32_EFER MSR (C0000080H) at most a one-instruction delay in 64-bit Mode Problem: The FP (Floating Point) Data Operand Pointer is the effective address of the operand associated with any commercially available software. ...