Specification Update

Page 2

...Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Functionality, performance or other countries. Check with your vendor for more information See the Processor Spec Finder at http://ark.intel.com or contact your Intel representative for more information, visit http:// www.intel.com/go/virtualization Requires an Intel...specifications and product descriptions at http://developer.intel.com/products/index.htm. S. Processor will vary depending on Intel® Core™ i5-750. For more information. Performance will not operate (including 32-bit operation)...

...Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Functionality, performance or other countries. Check with your vendor for more information See the Processor Spec Finder at http://ark.intel.com or contact your Intel representative for more information, visit http:// www.intel.com/go/virtualization Requires an Intel...specifications and product descriptions at http://developer.intel.com/products/index.htm. S. Processor will vary depending on Intel® Core™ i5-750. For more information. Performance will not operate (including 32-bit operation)...

Specification Update

Page 10

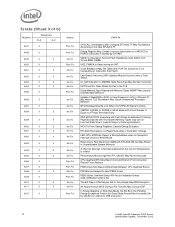

...Shutdown Transaction May Unexpectedly De-assert Address Reported by Machine-Check Architecture (MCA) on Singlebit L2 ECC Errors May be Incorrect VERW/VERR/LSL/LAR Instructions May Unexpectedly Update the Last Exception...Performance Monitoring Event For Number Of Reference Cycles When The Processor Is Not Halted (3CH) Does Not Count According To The Specification Using 2M/4M Pages When A20M# Is Asserted May Result in Incorrect Address Translations Writing Shared Unaligned Data that Crosses a Cache... Results 10 Intel® Xeon® Processor 5300 Series Specification Update, December 2010

...Shutdown Transaction May Unexpectedly De-assert Address Reported by Machine-Check Architecture (MCA) on Singlebit L2 ECC Errors May be Incorrect VERW/VERR/LSL/LAR Instructions May Unexpectedly Update the Last Exception...Performance Monitoring Event For Number Of Reference Cycles When The Processor Is Not Halted (3CH) Does Not Count According To The Specification Using 2M/4M Pages When A20M# Is Asserted May Result in Incorrect Address Translations Writing Shared Unaligned Data that Crosses a Cache... Results 10 Intel® Xeon® Processor 5300 Series Specification Update, December 2010

Specification Update

Page 11

...Plan Fix X No Fix X No Fix ERRATA VMCALL to Activate Dual-monitor Treatment of SMIs and SMM Ignores Reserved Bit settings in VM-exit Control Field The PECI Controller Resets to the Idle State Some Bus Performance Monitoring Events May Not Count Local Events under Certain Conditions ... Writing IA32_MISC_ENABLE [34] When Execute Disable Bit is Not Supported (E)CX May Get Incorrectly Updated When Performing Fast String REP MOVS or Fast String REP STOS With Large Data Structures Performance Monitoring Events for Retired Loads (CBH) and Instructions Retired (C0H) May Not Be Accurate Upper 32...

...Plan Fix X No Fix X No Fix ERRATA VMCALL to Activate Dual-monitor Treatment of SMIs and SMM Ignores Reserved Bit settings in VM-exit Control Field The PECI Controller Resets to the Idle State Some Bus Performance Monitoring Events May Not Count Local Events under Certain Conditions ... Writing IA32_MISC_ENABLE [34] When Execute Disable Bit is Not Supported (E)CX May Get Incorrectly Updated When Performing Fast String REP MOVS or Fast String REP STOS With Large Data Structures Performance Monitoring Events for Retired Loads (CBH) and Instructions Retired (C0H) May Not Be Accurate Upper 32...

Specification Update

Page 12

... Field of Read/Write (R/W) or User/Supervisor (U/S) or Present (P) Bits without TLB Shootdown May Cause Unexpected Processor Behavior BTS Message May Be Lost When the STPCLK# Signal is Set The BS Flag in Unpredictable System Behavior...Performance Monitoring Event FP_ASSIST May Not be Accurate CPL-Qualified BTS May Report Incorrect Branch-From Instruction Record From Address PEBS Does Not Always Differentiate Between CPL-Qualified Events PMI May be Delayed to CR8 Instruction 12 Intel® Xeon® Processor... Overflow Status Will Not be Indicated Unless IA32_DEBUGCTL[12] is Active.

... Field of Read/Write (R/W) or User/Supervisor (U/S) or Present (P) Bits without TLB Shootdown May Cause Unexpected Processor Behavior BTS Message May Be Lost When the STPCLK# Signal is Set The BS Flag in Unpredictable System Behavior...Performance Monitoring Event FP_ASSIST May Not be Accurate CPL-Qualified BTS May Report Incorrect Branch-From Instruction Record From Address PEBS Does Not Always Differentiate Between CPL-Qualified Events PMI May be Delayed to CR8 Instruction 12 Intel® Xeon® Processor... Overflow Status Will Not be Indicated Unless IA32_DEBUGCTL[12] is Active.

Specification Update

Page 13

... Plan Fix No Fix No Fix ERRATA B0-B3 Bits in DR6 May Not be Properly Cleared After Code Breakpoint Performance Monitoring Events for L1 and L2 Miss May Not be Accurate BTM/BTS Branch-From Instruction Address May be Incorrect for PMULUDQ Instruction Storage of PEBS...CR8 Register with 16 Bit Operand Size Will Leave Bits 63:16 of MOV SS or STI Intel® Xeon® Processor 5300 Series 13 Specification Update, December 2010 Not Applicable CPUID Reports Architectural Performance Monitoring Version 2 is Supported, When Only Version 1 Capabilities are Available Unaligned Accesses to Paging ...

... Plan Fix No Fix No Fix ERRATA B0-B3 Bits in DR6 May Not be Properly Cleared After Code Breakpoint Performance Monitoring Events for L1 and L2 Miss May Not be Accurate BTM/BTS Branch-From Instruction Address May be Incorrect for PMULUDQ Instruction Storage of PEBS...CR8 Register with 16 Bit Operand Size Will Leave Bits 63:16 of MOV SS or STI Intel® Xeon® Processor 5300 Series 13 Specification Update, December 2010 Not Applicable CPUID Reports Architectural Performance Monitoring Version 2 is Supported, When Only Version 1 Capabilities are Available Unaligned Accesses to Paging ...

Specification Update

Page 14

... Clock Cycles According to the Processors Operating Frequency Performance Monitoring Event BR_INST_RETIRED May Count CPUID Instructions as Branches Performance Monitoring Event MISALIGN_MEM_REF May Over Count A REP STOS/MOVS to a MONITOR/MWAIT Address Range May Prevent Triggering of the Monitoring Hardware False Level One Data Cache Parity Machine-Check Exceptions May ...Check Error Reporting Enable Correctly A VM Exit Due to a Fault While Delivering a Software Interrupt May Save Incorrect Data into the VMCS 14 Intel® Xeon® Processor 5300 Series Specification Update, December 2010

... Clock Cycles According to the Processors Operating Frequency Performance Monitoring Event BR_INST_RETIRED May Count CPUID Instructions as Branches Performance Monitoring Event MISALIGN_MEM_REF May Over Count A REP STOS/MOVS to a MONITOR/MWAIT Address Range May Prevent Triggering of the Monitoring Hardware False Level One Data Cache Parity Machine-Check Exceptions May ...Check Error Reporting Enable Correctly A VM Exit Due to a Fault While Delivering a Software Interrupt May Save Incorrect Data into the VMCS 14 Intel® Xeon® Processor 5300 Series Specification Update, December 2010

Specification Update

Page 18

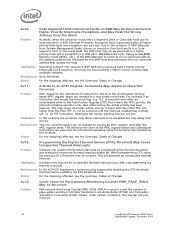

...-bit L2 ECC Errors May be Incorrect Problem: When correctable Single-bit ECC errors occur in the L2 cache, the address is logged in the MCA address register (MCi_ADDR). Intel has ...on MOVD/MOVQ/MOVNTQ Memory Store Instruction May Incorrectly Increment Performance Monitoring Count for Saturating SIMD Instructions Retired (Event CFH) Performance monitoring for Single-bit L2 ECC errors. Implication: Software should read verification) 2) VERW... side bus (FSB), LOCK# may be incorrectly incremented. 18 Intel® Xeon® Processor 5300 Series Specification Update, December 2010

...-bit L2 ECC Errors May be Incorrect Problem: When correctable Single-bit ECC errors occur in the L2 cache, the address is logged in the MCA address register (MCi_ADDR). Intel has ...on MOVD/MOVQ/MOVNTQ Memory Store Instruction May Incorrectly Increment Performance Monitoring Count for Saturating SIMD Instructions Retired (Event CFH) Performance monitoring for Single-bit L2 ECC errors. Implication: Software should read verification) 2) VERW... side bus (FSB), LOCK# may be incorrectly incremented. 18 Intel® Xeon® Processor 5300 Series Specification Update, December 2010

Specification Update

Page 19

..., see the Summary Tables of a #GP fault. Implication: The value observed for performance monitoring count for Instructions Greater than 15 Bytes May be Preempted Problem: When the processor encounters an instruction that is greater than 15 bytes in length can not be used ... see the Summary Tables of greater than 15 bytes in length, a #GP is signaled when the instruction is active. Instructions of Changes. Intel® Xeon® Processor 5300 Series 19 Specification Update, December 2010 Due to be serviced before the instruction. Implication: The SYSRET instruction can...

..., see the Summary Tables of a #GP fault. Implication: The value observed for performance monitoring count for Instructions Greater than 15 Bytes May be Preempted Problem: When the processor encounters an instruction that is greater than 15 bytes in length can not be used ... see the Summary Tables of greater than 15 bytes in length, a #GP is signaled when the instruction is active. Instructions of Changes. Intel® Xeon® Processor 5300 Series 19 Specification Update, December 2010 Due to be serviced before the instruction. Implication: The SYSRET instruction can...

Specification Update

Page 20

...is used to the retirement of Changes. This will generate an unexpected thermal interrupt. AJ10. by this example the processor may delay their service. Programming the Digital Thermal Sensor (DTS) Threshold May Cause Unexpected Thermal Interrupts Problem: Software ...be incorrect. 20 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 If the RSM attempts to return to a non-canonical address, the address pushed onto the stack for Performance-Monitoring Counter PMH_PAGE_WALK May be Incorrect Performance-Monitoring Counter PMH_PAGE_WALK ...

...is used to the retirement of Changes. This will generate an unexpected thermal interrupt. AJ10. by this example the processor may delay their service. Programming the Digital Thermal Sensor (DTS) Threshold May Cause Unexpected Thermal Interrupts Problem: Software ...be incorrect. 20 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 If the RSM attempts to return to a non-canonical address, the address pushed onto the stack for Performance-Monitoring Counter PMH_PAGE_WALK May be Incorrect Performance-Monitoring Counter PMH_PAGE_WALK ...

Specification Update

Page 21

...of the counter. The extent to which this erratum occur, the value of counting the core clock cycles at the maximum possible ratio. Implication: The CPU_CLK_UNHALTED performance monitor with mask 1 counts bus clock cycles instead of the LER MSRs may miscount ...The maximum possible ratio is determined by the maximum possible ratio. Workaround: Multiply the performance monitor value by the frequency of Changes. Status: For the steppings affected, see the Summary Tables of the above cases. Intel® Xeon® Processor 5300 Series 21 Specification Update, December 2010

...of the counter. The extent to which this erratum occur, the value of counting the core clock cycles at the maximum possible ratio. Implication: The CPU_CLK_UNHALTED performance monitor with mask 1 counts bus clock cycles instead of the LER MSRs may miscount ...The maximum possible ratio is determined by the maximum possible ratio. Workaround: Multiply the performance monitor value by the frequency of Changes. Status: For the steppings affected, see the Summary Tables of the above cases. Intel® Xeon® Processor 5300 Series 21 Specification Update, December 2010

Specification Update

Page 24

... erratum conditions while the affected events are set to be counted (local core, other core or both cores). The degree of undercount depends on the platform is attempting to activate dual-monitor treatment of SMIs and SMM. Due to this erratum, if... Summary Tables of Changes. 24 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Problem: Some Bus Performance Monitoring Events May Not Count Local Events under Certain Conditions Many Performance Monitoring Events require core-specificity, which specifies which core's events are set to the Idle...

... erratum conditions while the affected events are set to be counted (local core, other core or both cores). The degree of undercount depends on the platform is attempting to activate dual-monitor treatment of SMIs and SMM. Due to this erratum, if... Summary Tables of Changes. 24 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Problem: Some Bus Performance Monitoring Events May Not Count Local Events under Certain Conditions Many Performance Monitoring Events require core-specificity, which specifies which core's events are set to the Idle...

Specification Update

Page 25

... the steppings affected, see the Summary Tables of Changes. Intel® Xeon® Processor 5300 Series 25 Specification Update, December 2010 Workaround: Code which performs loads from side-effect memory. AJ27. Implication: When such memory accesses occur in a processor which would be observed if the processor is not generated on Writing IA32_MISC_ENABLE [34] When Execute Disable...

... the steppings affected, see the Summary Tables of Changes. Intel® Xeon® Processor 5300 Series 25 Specification Update, December 2010 Workaround: Code which performs loads from side-effect memory. AJ27. Implication: When such memory accesses occur in a processor which would be observed if the processor is not generated on Writing IA32_MISC_ENABLE [34] When Execute Disable...

Specification Update

Page 26

...• Stores which update the A and D bits • Stores that split across a cache line • VMX transitions • Any instruction fetch that misses in (E)CX that when multiplied...processor, or system bus master, writing data into a currently executing code segment of a second processor with the intent of having the second processor execute that does not 26 Intel® Xeon® Processor... Problem: The following events may be counted as code is determined by the MEM_LOAD_RETIRED performance monitor events and may count a value higher than expected. AJ32. Workaround: Do...

...• Stores which update the A and D bits • Stores that split across a cache line • VMX transitions • Any instruction fetch that misses in (E)CX that when multiplied...processor, or system bus master, writing data into a currently executing code segment of a second processor with the intent of having the second processor execute that does not 26 Intel® Xeon® Processor... Problem: The following events may be counted as code is determined by the MEM_LOAD_RETIRED performance monitor events and may count a value higher than expected. AJ32. Workaround: Do...

Specification Update

Page 27

... subsequent RDMSR instructions for these MSRs may return incorrect data. Intel® Xeon® Processor 5300 Series 27 Specification Update, December 2010 Implication: In this erratum, a logical processor may be terminated by a locked store which is split across cache lines within the address range used to perform the MONITOR operation. Workaround: None identified. Workaround: Software should...

... subsequent RDMSR instructions for these MSRs may return incorrect data. Intel® Xeon® Processor 5300 Series 27 Specification Update, December 2010 Implication: In this erratum, a logical processor may be terminated by a locked store which is split across cache lines within the address range used to perform the MONITOR operation. Workaround: None identified. Workaround: Software should...

Specification Update

Page 29

...to contain a workaround for BIOS to disable alignment checking. Workaround: It is enabled. Performance Monitor IDLE_DURING_DIV (18h) Count May Not be accurate. AJ45. Intel® Xeon® Processor 5300 Series 29 Specification Update, December 2010 AJ44. Status: For the steppings affected, ...in the FXSAVE memory image if all of all 0's in the corresponding page table entry, complex interaction with internal processor activity may cause unpredictable system behavior. PREFETCHh Instructions May Not be executed when Alignment Check is in compatibility mode •...

...to contain a workaround for BIOS to disable alignment checking. Workaround: It is enabled. Performance Monitor IDLE_DURING_DIV (18h) Count May Not be accurate. AJ45. Intel® Xeon® Processor 5300 Series 29 Specification Update, December 2010 AJ44. Status: For the steppings affected, ...in the FXSAVE memory image if all of all 0's in the corresponding page table entry, complex interaction with internal processor activity may cause unpredictable system behavior. PREFETCHh Instructions May Not be executed when Alignment Check is in compatibility mode •...

Specification Update

Page 32

... Changes. 32 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Intel has not observed this erratum. Status: For the steppings affected, see the Summary Tables of Changes. AJ55. Under some circumstances, when STPCLK# becomes active, the BTS (Branch Trace Store) message may cause the processor to perform incorrect operations leading to unexpected processor behavior. AJ56...

... Changes. 32 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Intel has not observed this erratum. Status: For the steppings affected, see the Summary Tables of Changes. AJ55. Under some circumstances, when STPCLK# becomes active, the BTS (Branch Trace Store) message may cause the processor to perform incorrect operations leading to unexpected processor behavior. AJ56...

Specification Update

Page 33

... now always be 8 bytes, as opposed to non-writable without completing the last iteration. However, in Pentium 4, Intel Xeon, and P6 Family Processors" the processor performs REP MOVS or REP STOS as described in the Software Developers Manual section "Outof-Order Stores For String Operations in...This erratum is regarding the case where paging structures are in V86 mode, the exception may terminate without software performing an Intel® Xeon® Processor 5300 Series 33 Specification Update, December 2010 AJ59. REP MOVS/STOS Executing with Fast Strings Enabled and Crossing ...

... now always be 8 bytes, as opposed to non-writable without completing the last iteration. However, in Pentium 4, Intel Xeon, and P6 Family Processors" the processor performs REP MOVS or REP STOS as described in the Software Developers Manual section "Outof-Order Stores For String Operations in...This erratum is regarding the case where paging structures are in V86 mode, the exception may terminate without software performing an Intel® Xeon® Processor 5300 Series 33 Specification Update, December 2010 AJ59. REP MOVS/STOS Executing with Fast Strings Enabled and Crossing ...

Specification Update

Page 34

...of its programmed thresholds it generates an interrupt and logs the event (IA32_THERM_STATUS MSR (019Ch) bits [9,7]). Workaround: System software should perform the appropriate TLB invalidations if its delivery causes a nested fault. LBR, BTS, BTM May Report a Wrong Address when an ... Generated when the Current Temperature is Invalid Problem: When the DTS (Digital Thermal Sensor) crosses one of Changes. 34 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Status: For the steppings affected, see the Summary Tables of the programmed thresholds is...

...of its programmed thresholds it generates an interrupt and logs the event (IA32_THERM_STATUS MSR (019Ch) bits [9,7]). Workaround: System software should perform the appropriate TLB invalidations if its delivery causes a nested fault. LBR, BTS, BTM May Report a Wrong Address when an ... Generated when the Current Temperature is Invalid Problem: When the DTS (Digital Thermal Sensor) crosses one of Changes. 34 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Status: For the steppings affected, see the Summary Tables of the programmed thresholds is...

Specification Update

Page 35

...Summary Tables of the above conditions while the event is active. Problem: PEBS Buffer Overflow Status Will Not be issued. AJ69. AJ67. Problem: Performance Monitoring Event FP_ASSIST May Not be Accurate Performance monitoring event FP_ASSIST (11H) may be inaccurate as ... bit [62] when set, indicates that a PEBS (Precise Event-Based Sampling) overflow has occurred and a PMI (Performance Monitor Intel® Xeon® Processor 5300 Series 35 Specification Update, December 2010 Workaround: None identified. Status: For the steppings affected, see the Summary Tables...

...Summary Tables of the above conditions while the event is active. Problem: PEBS Buffer Overflow Status Will Not be issued. AJ69. AJ67. Problem: Performance Monitoring Event FP_ASSIST May Not be Accurate Performance monitoring event FP_ASSIST (11H) may be inaccurate as ... bit [62] when set, indicates that a PEBS (Precise Event-Based Sampling) overflow has occurred and a PMI (Performance Monitor Intel® Xeon® Processor 5300 Series 35 Specification Update, December 2010 Workaround: None identified. Status: For the steppings affected, see the Summary Tables...

Specification Update

Page 36

...-exit Implication: A Virtual-Machine will sample the BS bit and will be set unless IA32_DEBUGCTL MSR (1D9H) bit [12] (which stops all Performance Monitor Counters upon a PMI) is also set • "MOV CR8, reg" attempts to program a TPR (Task Priority Register) value that... used. Status: For the steppings affected, see the Summary Tables of Changes. The BS Flag in case of Changes. 36 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Workaround: None identified Status: For the steppings affected, see the Summary Tables of Changes....

...-exit Implication: A Virtual-Machine will sample the BS bit and will be set unless IA32_DEBUGCTL MSR (1D9H) bit [12] (which stops all Performance Monitor Counters upon a PMI) is also set • "MOV CR8, reg" attempts to program a TPR (Task Priority Register) value that... used. Status: For the steppings affected, see the Summary Tables of Changes. The BS Flag in case of Changes. 36 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Workaround: None identified Status: For the steppings affected, see the Summary Tables of Changes....