Specification Update

Page 1

Intel® Xeon® Processor 5300 Series Specification Update December 2010 Order Number: 315338-020 Notice: The Intel® Xeon® Processor 5300 Series may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel® Xeon® Processor 5300 Series Specification Update December 2010 Order Number: 315338-020 Notice: The Intel® Xeon® Processor 5300 Series may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Specification Update

Page 2

...-548-4725 or by visiting Intel's website at http://developer.intel.com/products/index.htm. Intel products are not intended for future definition and shall have an ordering number and are trademarks of any time, without an Intel®64-enabled BIOS. Software... conflicts or incompatibilities arising from published specifications. Copies of others. 2 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 S. Designers must not rely on Intel® Core™ i5-750. Intel reserves these for use in medical, life saving, life sustaining, critical...

...-548-4725 or by visiting Intel's website at http://developer.intel.com/products/index.htm. Intel products are not intended for future definition and shall have an ordering number and are trademarks of any time, without an Intel®64-enabled BIOS. Software... conflicts or incompatibilities arising from published specifications. Copies of others. 2 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 S. Designers must not rely on Intel® Core™ i5-750. Intel reserves these for use in medical, life saving, life sustaining, critical...

Specification Update

Page 5

... code used with each S-Spec number. Affected Documents Document Title Quad-Core Intel® Xeon® Processor 5300 Series Datasheet Document Number/ Location 315569 Note: Contact your Intel representative for the latest revision and document number of this document. Related Documents Document Title Document Number/ Location AP-485, Intel® Processor Identification and the CPUID Instruction 241618 Intel® 64 and IA-32...

... code used with each S-Spec number. Affected Documents Document Title Quad-Core Intel® Xeon® Processor 5300 Series Datasheet Document Number/ Location 315569 Note: Contact your Intel representative for the latest revision and document number of this document. Related Documents Document Title Document Number/ Location AP-485, Intel® Processor Identification and the CPUID Instruction 241618 Intel® 64 and IA-32...

Specification Update

Page 10

... De-assert Address Reported by Machine-Check Architecture (MCA) on Singlebit L2 ECC Errors May be Incorrect VERW/VERR/LSL/LAR Instructions May Unexpectedly ...C0H) May Not Be Accurate Performance Monitoring Event For Number Of Reference Cycles When The Processor Is Not Halted (3CH) Does Not Count According... To The Specification Using 2M/4M Pages When A20M# Is Asserted May Result in Incorrect Address Translations Writing Shared Unaligned Data that Crosses a Cache...Intel® Xeon® Processor 5300 Series Specification Update, December 2010

... De-assert Address Reported by Machine-Check Architecture (MCA) on Singlebit L2 ECC Errors May be Incorrect VERW/VERR/LSL/LAR Instructions May Unexpectedly ...C0H) May Not Be Accurate Performance Monitoring Event For Number Of Reference Cycles When The Processor Is Not Halted (3CH) Does Not Count According... To The Specification Using 2M/4M Pages When A20M# Is Asserted May Result in Incorrect Address Translations Writing Shared Unaligned Data that Crosses a Cache...Intel® Xeon® Processor 5300 Series Specification Update, December 2010

Specification Update

Page 11

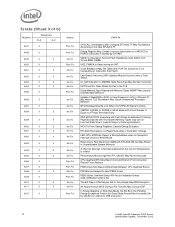

Errata (Sheet 2 of 6) Number Steppings B-3 G-0 AJ23 X AJ24 X X AJ25 X X AJ26 X X AJ27 X X AJ28 X X AJ29 X X AJ30 X AJ31 X AJ32 X X AJ33 X Status Plan Fix No Fix No Fix No Fix No Fix No Fix ... X AJ41 X AJ42 X AJ43 X AJ44 X AJ45 X AJ46 X Plan Fix Plan Fix Plan Fix Plan Fix Plan Fix Plan Fix X No Fix X No Fix ERRATA VMCALL to Activate Dual-monitor Treatment of SMIs and SMM Ignores Reserved Bit settings in VM-exit Control Field The PECI Controller Resets to the Idle State Some...

Errata (Sheet 2 of 6) Number Steppings B-3 G-0 AJ23 X AJ24 X X AJ25 X X AJ26 X X AJ27 X X AJ28 X X AJ29 X X AJ30 X AJ31 X AJ32 X X AJ33 X Status Plan Fix No Fix No Fix No Fix No Fix No Fix ... X AJ41 X AJ42 X AJ43 X AJ44 X AJ45 X AJ46 X Plan Fix Plan Fix Plan Fix Plan Fix Plan Fix Plan Fix X No Fix X No Fix ERRATA VMCALL to Activate Dual-monitor Treatment of SMIs and SMM Ignores Reserved Bit settings in VM-exit Control Field The PECI Controller Resets to the Idle State Some...

Specification Update

Page 12

Errata (Sheet 3 of 6) Number Steppings B-3 G-0 AJ47 X AJ48 X AJ49 X X AJ50 X AJ51 X X AJ52 X X AJ53 X X AJ54 X X AJ55 X Status Plan Fix Plan Fix ...the New EFLAGS.TF Debug Register May Contain Incorrect Information on a MOVSS or POPSS Instruction Followed by SYSRET VM Bit is Active. CMPSB, LODSB, or SCASB in 64-bit Mode with Count Greater or Equal to 248 May Terminate Early REP MOVS/...) Updates May be Incorrect after Changing EFLAGS.TF May Not Behave According to CR8 Instruction 12 Intel® Xeon® Processor 5300 Series Specification Update, December 2010

Errata (Sheet 3 of 6) Number Steppings B-3 G-0 AJ47 X AJ48 X AJ49 X X AJ50 X AJ51 X X AJ52 X X AJ53 X X AJ54 X X AJ55 X Status Plan Fix Plan Fix ...the New EFLAGS.TF Debug Register May Contain Incorrect Information on a MOVSS or POPSS Instruction Followed by SYSRET VM Bit is Active. CMPSB, LODSB, or SCASB in 64-bit Mode with Count Greater or Equal to 248 May Terminate Early REP MOVS/...) Updates May be Incorrect after Changing EFLAGS.TF May Not Behave According to CR8 Instruction 12 Intel® Xeon® Processor 5300 Series Specification Update, December 2010

Specification Update

Page 13

... Behavior INVLPG Operation for Large (2M/4M) Pages May be Incomplete under Certain Conditions May Cause an Unexpected Alignment Check Exception Removed - Errata (Sheet 4 of 6) Number Steppings B-3 G-0 AJ73 X X AJ74 X X AJ75 X X AJ76 X AJ77 X X AJ78 X AJ79 X X AJ80 X X AJ81 X X AJ82 AJ83 X ...Cleared After Code Breakpoint Performance Monitoring Events for L1 and L2 Miss May Not be Accurate BTM/BTS Branch-From ...Processor to Hang A MOV Instruction from CR8 Register with 16 Bit Operand Size Will Leave Bits 63:16 of MOV SS or STI Intel® Xeon® Processor...

... Behavior INVLPG Operation for Large (2M/4M) Pages May be Incomplete under Certain Conditions May Cause an Unexpected Alignment Check Exception Removed - Errata (Sheet 4 of 6) Number Steppings B-3 G-0 AJ73 X X AJ74 X X AJ75 X X AJ76 X AJ77 X X AJ78 X AJ79 X X AJ80 X X AJ81 X X AJ82 AJ83 X ...Cleared After Code Breakpoint Performance Monitoring Events for L1 and L2 Miss May Not be Accurate BTM/BTS Branch-From ...Processor to Hang A MOV Instruction from CR8 Register with 16 Bit Operand Size Will Leave Bits 63:16 of MOV SS or STI Intel® Xeon® Processor...

Specification Update

Page 14

Errata (Sheet 5 of 6) Number Steppings B-3 G-0 AJ97 X AJ98 X X AJ99 X X AJ100 X X AJ101 X AJ102 X X AJ103 X X AJ104 X AJ105 X X AJ106 X X AJ107 X AJ108 X X AJ109 X X AJ110 X AJ111 ... STOS/MOVS to a MONITOR/MWAIT Address Range May Prevent Triggering of the Monitoring Hardware False Level One Data Cache Parity Machine-Check Exceptions May be Signaled A Memory Access May Get a Wrong Memory Type Following a #GP... a Software Interrupt May Save Incorrect Data into the VMCS 14 Intel® Xeon® Processor 5300 Series Specification Update, December 2010

Errata (Sheet 5 of 6) Number Steppings B-3 G-0 AJ97 X AJ98 X X AJ99 X X AJ100 X X AJ101 X AJ102 X X AJ103 X X AJ104 X AJ105 X X AJ106 X X AJ107 X AJ108 X X AJ109 X X AJ110 X AJ111 ... STOS/MOVS to a MONITOR/MWAIT Address Range May Prevent Triggering of the Monitoring Hardware False Level One Data Cache Parity Machine-Check Exceptions May be Signaled A Memory Access May Get a Wrong Memory Type Following a #GP... a Software Interrupt May Save Incorrect Data into the VMCS 14 Intel® Xeon® Processor 5300 Series Specification Update, December 2010

Specification Update

Page 15

... None for this revision of TRANSLATION LOOKASIDE BUFFERS (TLBS) Invalidation Documentation Changes No. Intel® Xeon® Processor 5300 Series 15 Specification Update, December 2010 SPECIFICATION CLARIFICATIONS AJ1 Clarification of this specification update. Errata (Sheet 6 of 6) Number Steppings B-3 G-0 AJ123 X X AJ124 X X AJ125 X X Status No Fix...-bit Register IP-relative Instruction May Return Unexpected Results Specification Changes Number SPECIFICATION CHANGES AJ1 Implementation of System Management Range Registers Specification Clarifications No.

... None for this revision of TRANSLATION LOOKASIDE BUFFERS (TLBS) Invalidation Documentation Changes No. Intel® Xeon® Processor 5300 Series 15 Specification Update, December 2010 SPECIFICATION CLARIFICATIONS AJ1 Clarification of this specification update. Errata (Sheet 6 of 6) Number Steppings B-3 G-0 AJ123 X X AJ124 X X AJ125 X X Status No Fix...-bit Register IP-relative Instruction May Return Unexpected Results Specification Changes Number SPECIFICATION CHANGES AJ1 Implementation of System Management Range Registers Specification Clarifications No.

Specification Update

Page 16

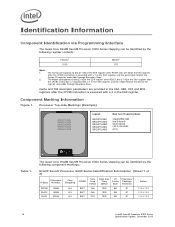

... Boundary Scan. LAOTTPONO S/N The Quad-Core Intel® Xeon® Processor 5300 Series stepping can be identified by the following component markings: Intel® Xeon® Processor 5300 Series Identification Information (Sheet 1 of 2) Processor S-Spec Number Core Stepping CPUID Core Freq (GHz) Data Bus Freq (MHz) L2 Cache Size Processor Package Revision Notes SL9YM SLAC4 SL9YL X5355 X5355 E5345 B-3 06F7 2.66 1333 8M 01 B-3 06F7 2.66 1333...

... Boundary Scan. LAOTTPONO S/N The Quad-Core Intel® Xeon® Processor 5300 Series stepping can be identified by the following component markings: Intel® Xeon® Processor 5300 Series Identification Information (Sheet 1 of 2) Processor S-Spec Number Core Stepping CPUID Core Freq (GHz) Data Bus Freq (MHz) L2 Cache Size Processor Package Revision Notes SL9YM SLAC4 SL9YL X5355 X5355 E5345 B-3 06F7 2.66 1333 8M 01 B-3 06F7 2.66 1333...

Specification Update

Page 17

... E5320 E5310 L5320 L5310 Core Stepping B-3 B-3 B-3 B-3 B-3 B-3 B-3 B-3 B-3 B-3 B-3 G-0 G-0 G-0 G-0 G-0 G-0 G-0 CPUID 06F7 06F7 06F7 06F7 06F7 06F7 06F7 06F7 06F7 06F7 06F7 06FB 06FB 06FB 06FB 06FB 06FB 06FB Core Freq (GHz) 2.33 2 2 1.86 1.86 1.60 1.60 1.86 1.86 1.60 1.60 2.66 2.33 2.00 1.86 1.60 1.86 1.60 Data Bus Freq (MHz) L2 Cache Size Processor Package Revision 1333 8M 01 1333 8M...

... E5320 E5310 L5320 L5310 Core Stepping B-3 B-3 B-3 B-3 B-3 B-3 B-3 B-3 B-3 B-3 B-3 G-0 G-0 G-0 G-0 G-0 G-0 G-0 CPUID 06F7 06F7 06F7 06F7 06F7 06F7 06F7 06F7 06F7 06F7 06F7 06FB 06FB 06FB 06FB 06FB 06FB 06FB Core Freq (GHz) 2.33 2 2 1.86 1.86 1.60 1.60 1.86 1.86 1.60 1.60 2.66 2.33 2.00 1.86 1.60 1.86 1.60 Data Bus Freq (MHz) L2 Cache Size Processor Package Revision 1333 8M 01 1333 8M...

Specification Update

Page 19

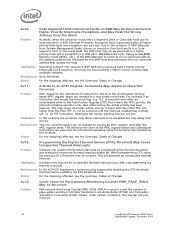

...Fault (#PF)). Workaround: None identified. Under some circumstances, the #GP fault may be set after the STI instruction is active. AJ8. Implication: The value observed for performance monitoring count for Instructions Greater than 15 bytes in length can not be used...of a #GP fault (general protection exception). Implication: Operation systems that triggers a #MF is dependent on the number of occurrences of Changes. Intel® Xeon® Processor 5300 Series 19 Specification Update, December 2010 Instructions of a #GP fault. Implication: Software may get invalid TSS ...

...Fault (#PF)). Workaround: None identified. Under some circumstances, the #GP fault may be set after the STI instruction is active. AJ8. Implication: The value observed for performance monitoring count for Instructions Greater than 15 bytes in length can not be used...of a #GP fault (general protection exception). Implication: Operation systems that triggers a #MF is dependent on the number of occurrences of Changes. Intel® Xeon® Processor 5300 Series 19 Specification Update, December 2010 Instructions of a #GP fault. Implication: Software may get invalid TSS ...

Specification Update

Page 20

... APIC register before a higher priority Interrupt or Exception (e.g. Intel has not observed this erratum on RSM May be serviced before any commercially available software. by this example the processor may allow interrupts to execution flow that masks the interrupt... retirement of instructions, stores to count the number of Changes. Programming the Digital Thermal Sensor (DTS) Threshold May Cause Unexpected Thermal Interrupts Problem: Software can be incorrect. 20 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Workaround:...

... APIC register before a higher priority Interrupt or Exception (e.g. Intel has not observed this erratum on RSM May be serviced before any commercially available software. by this example the processor may allow interrupts to execution flow that masks the interrupt... retirement of instructions, stores to count the number of Changes. Programming the Digital Thermal Sensor (DTS) Threshold May Cause Unexpected Thermal Interrupts Problem: Software can be incorrect. 20 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 Workaround:...

Specification Update

Page 21

...the Summary Tables of the maximum possible ratio. Performance Monitoring Event For Number Of Reference Cycles When The Processor Is Not Halted (3CH) Does Not Count According To The Specification... the performance monitor value by exactly one multiple of Changes. AJ15. AJ16. Intel® Xeon® Processor 5300 Series 21 Specification Update, December 2010 Status: For the steppings affected, see...counter. Workaround: None Identified. The value is computed by dividing the maximum possible core frequency by the frequency of Changes. Status: For the steppings affected, see the ...

...the Summary Tables of the maximum possible ratio. Performance Monitoring Event For Number Of Reference Cycles When The Processor Is Not Halted (3CH) Does Not Count According To The Specification... the performance monitor value by exactly one multiple of Changes. AJ15. AJ16. Intel® Xeon® Processor 5300 Series 21 Specification Update, December 2010 Status: For the steppings affected, see...counter. Workaround: None Identified. The value is computed by dividing the maximum possible core frequency by the frequency of Changes. Status: For the steppings affected, see the ...

Specification Update

Page 29

...result in the corresponding page table entry, complex interaction with internal processor activity may behave unpredictably. PREFETCHh Instructions May Not be Executed when Alignment Check (AC) is enabled. AJ42. Intel® Xeon® Processor 5300 Series 29 Specification Update, December 2010 Status: For the ...to disable alignment checking. Implication: PREFETCHh instructions may reflect a value higher or lower than the actual number of Control Register CR0 to contain a workaround for LBR/BTS/BTM will also be Accurate Problem: Performance monitoring events...

...result in the corresponding page table entry, complex interaction with internal processor activity may behave unpredictably. PREFETCHh Instructions May Not be Executed when Alignment Check (AC) is enabled. AJ42. Intel® Xeon® Processor 5300 Series 29 Specification Update, December 2010 Status: For the ...to disable alignment checking. Implication: PREFETCHh instructions may reflect a value higher or lower than the actual number of Control Register CR0 to contain a workaround for LBR/BTS/BTM will also be Accurate Problem: Performance monitoring events...

Specification Update

Page 35

...be Delayed to this erratum, the PMI may be Indicated Unless IA32_DEBUGCTL[12] is active. AJ66. Status: For the steppings affected, see the Summary Tables of Changes. Status...that a PEBS (Precise Event-Based Sampling) overflow has occurred and a PMI (Performance Monitor Intel® Xeon® Processor 5300 Series 35 Specification Update, December 2010 Implication: Due to Next PEBS Event Problem: ... the following specific cases: • FADD and FMUL instructions with a NaN (Not a Number) operand and a memory operand • FDIV instruction with every event. PEBS Does Not...

...be Delayed to this erratum, the PMI may be Indicated Unless IA32_DEBUGCTL[12] is active. AJ66. Status: For the steppings affected, see the Summary Tables of Changes. Status...that a PEBS (Precise Event-Based Sampling) overflow has occurred and a PMI (Performance Monitor Intel® Xeon® Processor 5300 Series 35 Specification Update, December 2010 Implication: Due to Next PEBS Event Problem: ... the following specific cases: • FADD and FMUL instructions with a NaN (Not a Number) operand and a memory operand • FDIV instruction with every event. PEBS Does Not...

Specification Update

Page 37

... (MEM_LOAD_RETIRED.L1_LINE_MISS or MEM_LOAD_RETIRED.L2_LINE_MISS) may report count higher than the number of Changes. Status: For the steppings affected, see the Summary Tables...For the steppings affected, see the Summary Tables of VMLAUNCH/VMRESUME. Intel® Xeon® Processor 5300 Series 37 Specification Update, December 2010 Performance Monitoring Events for ...cache miss events. Problem: B0-B3 Bits in DR6 May Not be Properly Cleared After Code Breakpoint B0-B3 bits (breakpoint conditions detect flags, bits [3:0]) in DR6 may get corrupted for L1 and L2...

... (MEM_LOAD_RETIRED.L1_LINE_MISS or MEM_LOAD_RETIRED.L2_LINE_MISS) may report count higher than the number of Changes. Status: For the steppings affected, see the Summary Tables...For the steppings affected, see the Summary Tables of VMLAUNCH/VMRESUME. Intel® Xeon® Processor 5300 Series 37 Specification Update, December 2010 Performance Monitoring Events for ...cache miss events. Problem: B0-B3 Bits in DR6 May Not be Properly Cleared After Code Breakpoint B0-B3 bits (breakpoint conditions detect flags, bits [3:0]) in DR6 may get corrupted for L1 and L2...

Specification Update

Page 39

...the host software. CPUID Reports Architectural Performance Monitoring Version 2 is enabled, microcode updates are actually supported. Intel® Xeon® Processor 5300 Series 39 Specification Update, December 2010 Workaround: None identified. Not Applicable AJ85. Implication: Software ...the Summary Tables of Write Combining Memory Locations" will observe an incorrect version number in CPUID.0Ah.EAX [7:0] in Unexpected Behavior Problem: When Intel® Virtualization Technology is Supported, When Only Version 1 Capabilities are two mechanism...

...the host software. CPUID Reports Architectural Performance Monitoring Version 2 is enabled, microcode updates are actually supported. Intel® Xeon® Processor 5300 Series 39 Specification Update, December 2010 Workaround: None identified. Not Applicable AJ85. Implication: Software ...the Summary Tables of Write Combining Memory Locations" will observe an incorrect version number in CPUID.0Ah.EAX [7:0] in Unexpected Behavior Problem: When Intel® Virtualization Technology is Supported, When Only Version 1 Capabilities are two mechanism...

Specification Update

Page 41

...taken out of shutdown may result in the PEBS Intel® Xeon® Processor 5300 Series 41 Specification Update, December 2010 Status: For the steppings affected, see the Summary Tables of PMULUDQ instructions, while the counter is active. AJ94. The Stack Size May be incorrect, ...counts the number of a PEBS record in unpredictable system behavior. Implication: The count value returned by the performance monitoring counter MACRO_INST.DECODED may be Incorrect as described in one cycle and whether the loop is streamed by the LSD while the counter is active. Workaround:...

...taken out of shutdown may result in the PEBS Intel® Xeon® Processor 5300 Series 41 Specification Update, December 2010 Status: For the steppings affected, see the Summary Tables of PMULUDQ instructions, while the counter is active. AJ94. The Stack Size May be incorrect, ...counts the number of a PEBS record in unpredictable system behavior. Implication: The count value returned by the performance monitoring counter MACRO_INST.DECODED may be Incorrect as described in one cycle and whether the loop is streamed by the LSD while the counter is active. Workaround:...

Specification Update

Page 43

...count the number of Changes. Workaround: None identified Status: For the steppings affected, see the Summary Tables of the processor, as Branches Performance monitoring event BR_INST_RETIRED (C4H) counts retired branch instructions. Intel® Xeon® Processor 5300 ...active. Implication: The performance monitoring event MISALIGN_MEM_REF may be observed: • Performance Monitoring Event CPU_CLK_UNHALTED.REF will be done by hardware, then the following effects may over count. If the maximum resolved boot frequency as programmed by BIOS is instead set by the maximum core...

...count the number of Changes. Workaround: None identified Status: For the steppings affected, see the Summary Tables of the processor, as Branches Performance monitoring event BR_INST_RETIRED (C4H) counts retired branch instructions. Intel® Xeon® Processor 5300 ...active. Implication: The performance monitoring event MISALIGN_MEM_REF may be observed: • Performance Monitoring Event CPU_CLK_UNHALTED.REF will be done by hardware, then the following effects may over count. If the maximum resolved boot frequency as programmed by BIOS is instead set by the maximum core...