Intel BX80605I7870 - Core i7 2.93 GHz Processor Support and Manuals

Get Help and Manuals for this Intel item

This item is in your list!

View All Support Options Below

Free Intel BX80605I7870 manuals!

Problems with Intel BX80605I7870?

Ask a Question

Free Intel BX80605I7870 manuals!

Problems with Intel BX80605I7870?

Ask a Question

Popular Intel BX80605I7870 Manual Pages

Data Sheet - Page 2

... cause the product to specifications and product descriptions at any time, without an Intel 64-enabled BIOS. The Intel® Core™ i7 Processor Extreme Edition and Intel® Core™ i7 Processor may contain design defects or errors known as errata which may make changes to deviate from future changes to represent proportional or quantitative increases in medical, life saving...

Data Sheet - Page 8

Tables

1-1 References...13 2-1 Functions Specifically Handled by the Processor 18 2-2 Device 0, Function 0: Generic Non-core Registers 19 2-3 Device 0, Function 1: System Address Decoder Registers 20 2-4 Device 2, Function 0: Intel QPI Link 0 Registers 21 2-5 Device 2, Function 1: Intel QPI Physical 0 Registers 22 2-6 Device 3, Function 0: Integrated Memory Controller Registers 23 2-7 Device...

Data Sheet - Page 11

...in non-executable memory the processor raises an error to enable smaller, quieter systems.

The Intel® Core™ i7 processor Extreme Edition and Intel® Core™ i7 processor are multi-core processors, based on 45 nm process technology. Enhanced Intel SpeedStep Technology allows trade-offs to a low level. See the Intel Architecture Software Developer's Manual for some classes of...

Data Sheet - Page 12

.... • Intel® Virtualization Technology (Intel® VT) - A set of Intel 64. The processor (in packaging or exposed to any supply voltages, have any clocks.

• Intel® Core™ i7 processor Extreme Edition and Intel® Core™ i7 processor - Refer to http://developer.intel.com/ for future reference on Intel 64 architecture and programming model can be...

Data Sheet - Page 13

...™ i7 Processor Extreme Edition and Intel® Core™ i7 Processor and LGA1366 Socket Thermal and Mechanical Design Guide

Intel® 64 and IA-32 Intel® Architecture Software Developer's Manual

• Volume 1: Basic Architecture • Volume 2A: Instruction Set Reference, A-M • Volume 2B: Instruction Set Reference, N-Z • Volume 3A: System Programming Guide, Part...

Data Sheet - Page 15

... to clear this bit, a one must be written to it. Read/Write 1 Set: A register bit can be read and written by software. Hardware will have no ...supported. Hardware or a configuration bit can be either read only. A register bit with in this bit has no effect. This document highlights registers which do not apply to the particular processor's Specification Update for the processor...

Data Sheet - Page 16

...PCI Local Bus Specification, Revision 2.2 requires that the values of 2C41h. Some of the processor registers described in...set required to processors supporting registered DIMMs.

• Device 4: Integrated Memory Controller Channel 0. Device 0, Function 1 contains the System Address Decode registers and resides at DID of 2C01h.

• Device 2: Intel QPI. Upon a reset, the processor sets...

Data Sheet - Page 17

...to processors supporting sparing, mirroring, and scrubbing RAS features. Datasheet

17 Functions Specifically Handled by the max bus range setting and processor ...processor socket. Device configuration is derived by the Processor

Component

Register Group

Intel QuickPath Architecture Generic Non-core Registers

Intel QuickPath Architecture System Address Decoder

Intel QPI Link 0

Intel...

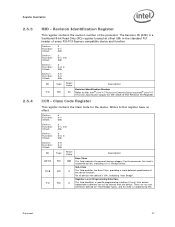

Data Sheet - Page 37

...is hardwired to the Intel® Core™ i7 Processor Extreme Edition and Intel® Core™ i7

Processor Specification Update for the device.... Identification Number

7:0

RO

0h Refer to 00h.

Register Description

2.5.3 2.5.4

RID -

Class Code Register

This register contains the Class Code for the value of the device function. For all devices the default is hardwired to ...

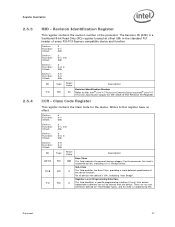

Data Sheet - Page 41

...29:28 RW

Reset Value

Description

PAM3_HIENABLE. 0D4000h-0D7FFFh Attribute (HIENABLE). Reads are serviced by DRAM.

Datasheet

41 Interrupt Status

If this device generates an interrupt, then this... 0 and this Interrupt Status bit is a 1, will the device's/function's INTx# signal be set for legacy device 0, function 0 at the configuration address offset 34h from 0D4000h to 0D7FFFh.

...

Data Sheet - Page 44

... 1 SMM space DRAM is not accessible to update the

display even when SMM is active. Code references may still access SMM space DRAM. This ...security. Global SMRAM Enable (G_SMRAME)

If set to be cleared by a Reset. Only SMM space between A0000h

and BFFFFh is supported so this bit has to 1 via a... IOH and non-core have this lock. Software should ensure that no application

software (or BIOS itself)...

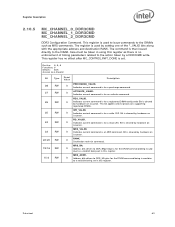

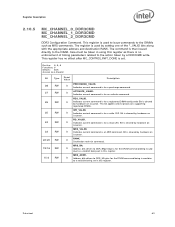

Data Sheet - Page 47

...set for any active channel when

INIT_DONE is required to processors supporting registered DIMMs.

MC_CONTROL

This register is active.

CHANNEL1_ACTIVE

When set by software. This bit is required to be

set....

Register Description

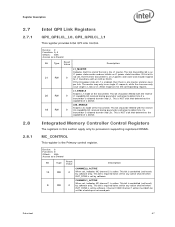

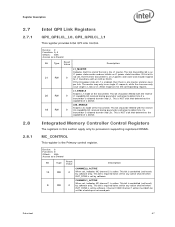

2.7

2.7.1

2.8

2.8.1

Intel QPI Link Registers

QPI_QPILCL_L0, QPI_QPILCL_L1

This register provides Intel QPI Link Control.

This bit should ...

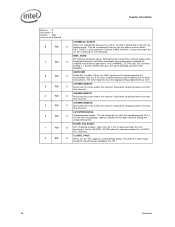

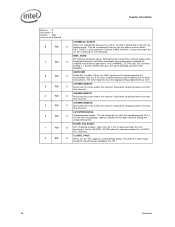

Data Sheet - Page 48

... registers must both be appropriately programmed as a Dword

8

RW

0

7

WO

0

6

RW

0

5

RW

0

4

RW

0

3

RW

0

2

RW

0

1

RW

0

0

RW

0

CHANNEL0_ACTIVE When set, indicate MC channel 0 is controlled (set , the MC supports a Closed Page policy. AUTOPRECHARGE. Autoprecharge enable.

Equivalent to pulling warm reset for a lockstep or mirrored pair. Equivalent to pulling warm...

Data Sheet - Page 63

...is cleared by hardware on

issuance. Device: 4, 5, 6 Function: 0 Offset: 60h Access as there is set in this register. This bit applies only to DDR_MA pins for command. Bit is for a precharge command.

MRS_ADDR.

0

Address bits driven to processors supporting

registered DIMMs.

WR_VALID.

0

Indicates current command is for a read CAS. RD_VALID.

0

Indicates current command...

Data Sheet - Page 82

... for upper 32B half cacheline.

01 = Inject the ECC code word for lower 32B half cacheline.

00 = No masking will be applied.

0

REPEAT_EN.

1 = ECC errors will cause an uncorrectable error to be injected on the channel until the bit is set. i.e. 7:0 and 15:8 or 23:16 and 31:24). Flipping bits in the MC_CHANNEL_X_ADDR_MATCH...

Intel BX80605I7870 Reviews

Do you have an experience with the Intel BX80605I7870 that you would like to share?

Earn 750 points for your review!

We have not received any reviews for Intel yet.

Earn 750 points for your review!