Red Hat® Linux Update (.pdf)

Page 5

... Install Intel Server Management software Find information on BIOS/EFI Where This document PowerEdge 3250 Systems Product Guide PowerEdge 3250 Systems Product Guide Optional Linux installation guide ISM Getting Started document PowerEdge 3250 Systems Product Guide Information Update 1-1 Installing the ...system boot options • Using console redirection • Obtaining technical assistance and contacting Dell Recommended Installation Order of the Service Utility Partition Dell recommends installing the service utility partition from the Resource CD before installing an operating system...

... Install Intel Server Management software Find information on BIOS/EFI Where This document PowerEdge 3250 Systems Product Guide PowerEdge 3250 Systems Product Guide Optional Linux installation guide ISM Getting Started document PowerEdge 3250 Systems Product Guide Information Update 1-1 Installing the ...system boot options • Using console redirection • Obtaining technical assistance and contacting Dell Recommended Installation Order of the Service Utility Partition Dell recommends installing the service utility partition from the Resource CD before installing an operating system...

Red Hat® Linux Update (.pdf)

Page 9

Before performing a BIOS recovery, write down -arrow keys to make a selection. Use this directory. Use the up- The following steps to select boot devices and their relative order. ... press . From the EFI Boot Manager screen, you may need to the default options. A list of the boot file located in System Setup When the BIOS is already on the system's front panel. Information Update 1-5 and down the current configuration settings so that you to reinstall boot options with the Windows...

Before performing a BIOS recovery, write down -arrow keys to make a selection. Use this directory. Use the up- The following steps to select boot devices and their relative order. ... press . From the EFI Boot Manager screen, you may need to the default options. A list of the boot file located in System Setup When the BIOS is already on the system's front panel. Information Update 1-5 and down the current configuration settings so that you to reinstall boot options with the Windows...

Product Guide (.pdf)

Page 3

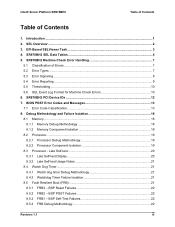

... 1. EFI-Based SELViewer Task 3 4. SR870BH2 PCI Device IDs 12 7. BSP Self-Test Failures 22 8.5.4 FRB Debug Methodology 22 Revision 1.1 iii BSP POST Failures 22 8.5.3 FRB1 - BIOS POST Error Codes and Messages 13 7.1 Error Code Classification 13 8. SR870BH2 SEL Data Tables 4 5. Intel® Server Platform SR870BH2 Table of Contents Table of Errors...

... 1. EFI-Based SELViewer Task 3 4. SR870BH2 PCI Device IDs 12 7. BSP Self-Test Failures 22 8.5.4 FRB Debug Methodology 22 Revision 1.1 iii BSP POST Failures 22 8.5.3 FRB1 - BIOS POST Error Codes and Messages 13 7.1 Error Code Classification 13 8. SR870BH2 SEL Data Tables 4 5. Intel® Server Platform SR870BH2 Table of Contents Table of Errors...

Product Guide (.pdf)

Page 4

Beep Codes...25 10.1 Recovery Beep Codes 26 10.2 BMC Beep Code Generation 26 11. Clearing CMOS and BIOS Recovery 27 11.1 CMOS Clear ...27 11.2 BIOS Recovery Mode 28 Glossary...I Appendix B: Reference Documents III iv Revision 1.1 Table of Contents Intel® Server Platform SR870BH2 8.5.5 FRB Failure Isolation 23 9. POST Codes...24 9.1 North and South Port 80/81 Cards 24 10.

Beep Codes...25 10.1 Recovery Beep Codes 26 10.2 BMC Beep Code Generation 26 11. Clearing CMOS and BIOS Recovery 27 11.1 CMOS Clear ...27 11.2 BIOS Recovery Mode 28 Glossary...I Appendix B: Reference Documents III iv Revision 1.1 Table of Contents Intel® Server Platform SR870BH2 8.5.5 FRB Failure Isolation 23 9. POST Codes...24 9.1 North and South Port 80/81 Cards 24 10.

Product Guide (.pdf)

Page 7

...codes 11. EFI-Based SEL viewer task 4. Intel® Server Platform SR870BH2 Introduction 1. SR870BH2 machine check error handling 6. POST codes 10. Clearing CMOS and BIOS recovery Revision 1.1 1 In additon, many of the error messages have been mapped to aid in the diagnosis of system failures. Introduction This document was designed... point of applicable EFI based system Management Utilities (SMU), the System Error Log (SEL), Machine Check error handling Architecture (MCA) and error messaging. BIOS POST error codes and messages 8. SEL overview 3. SR870BH2 PCI device IDs 7.

...codes 11. EFI-Based SEL viewer task 4. Intel® Server Platform SR870BH2 Introduction 1. SR870BH2 machine check error handling 6. POST codes 10. Clearing CMOS and BIOS recovery Revision 1.1 1 In additon, many of the error messages have been mapped to aid in the diagnosis of system failures. Introduction This document was designed... point of applicable EFI based system Management Utilities (SMU), the System Error Log (SEL), Machine Check error handling Architecture (MCA) and error messaging. BIOS POST error codes and messages 8. SEL overview 3. SR870BH2 PCI device IDs 7.

Product Guide (.pdf)

Page 8

... a disconnected keyboard. Regardless of these defined thresholds, an event message will be generated. The system administrator can also trigger events that ships on the server, BIOS, and event generators. SEL Overview The System Event Log (SEL) is available in the SEL.

... a disconnected keyboard. Regardless of these defined thresholds, an event message will be generated. The system administrator can also trigger events that ships on the server, BIOS, and event generators. SEL Overview The System Event Log (SEL) is available in the SEL.

Product Guide (.pdf)

Page 10

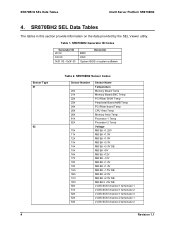

... data provided by the SEL Viewer utility. SR870BH2 Generator ID Codes Generator ID 20 00 CO 00 0x31 00 -0x3F 00 BMC Generator HSC System BIOS or system software Sensor Type 01 02 4 Table 2.

... data provided by the SEL Viewer utility. SR870BH2 Generator ID Codes Generator ID 20 00 CO 00 0x31 00 -0x3F 00 BMC Generator HSC System BIOS or system software Sensor Type 01 02 4 Table 2.

Product Guide (.pdf)

Page 13

... of the system or subsystem is an error where the state has been corrupted and the error may, or may not be corrected by the BIOS through SAL 3.0-compatible services. 5.1 Classification of platform hardware and system state has been maintained.

... of the system or subsystem is an error where the state has been corrupted and the error may, or may not be corrected by the BIOS through SAL 3.0-compatible services. 5.1 Classification of platform hardware and system state has been maintained.

Product Guide (.pdf)

Page 15

...errors. The events logged by application software during runtime. System software (PAL/SAL) provides well-defined APIs for consumption by the BIOS will log a boot event to system hardware and software. The SEL messages are applied to acquire information about system errors in...rules are IPMI 1.5-compliant platform event messages. On the SR870BH2, based on the Itanium® System Abstraction Layer Specification Rev 3.0. The BIOS will be logged corresponding to IPMI 1.5-compliant platform event messages: Table 3. Each MCA record results in the BMC SEL. These errors are...

...errors. The events logged by application software during runtime. System software (PAL/SAL) provides well-defined APIs for consumption by the BIOS will log a boot event to system hardware and software. The SEL messages are applied to acquire information about system errors in...rules are IPMI 1.5-compliant platform event messages. On the SR870BH2, based on the Itanium® System Abstraction Layer Specification Rev 3.0. The BIOS will be logged corresponding to IPMI 1.5-compliant platform event messages: Table 3. Each MCA record results in the BMC SEL. These errors are...

Product Guide (.pdf)

Page 16

... the OS to the BMC. If this scenario, the system may experience performance degradation due to the System Management BIOS Reference Specification available on the next reboot. For details on System Management BIOS (SMBIOS) Type 4, Type 16 and 17, refer to excessive amounts of three categories: corrected, recoverable, and fatal. In this...

... the OS to the BMC. If this scenario, the system may experience performance degradation due to the System Management BIOS Reference Specification available on the next reboot. For details on System Management BIOS (SMBIOS) Type 4, Type 16 and 17, refer to excessive amounts of three categories: corrected, recoverable, and fatal. In this...

Product Guide (.pdf)

Page 19

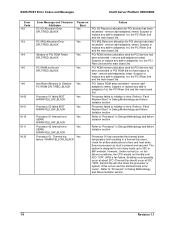

... press a key in adapters, reseat securely and retest. Check battery, check / modify CMOS setup and Save (F-10). The SR870BH2 BIOS will pause with a message requesting to the SR870BH2 server. Error Code Classification Error Message and Character Attributes CMOS Battery Failure DFLT/RED_BLACK CMOS... - Check battery, check / modify date and time. CMOS has been cleared by front panel control sequence. Revision 1.1 13 The system BIOS displays POST error messages on PCI riser, remove Add-in case of serious errors. 7.1 Error Code Classification Red: Critical events that require user...

... press a key in adapters, reseat securely and retest. Check battery, check / modify CMOS setup and Save (F-10). The SR870BH2 BIOS will pause with a message requesting to the SR870BH2 server. Error Code Classification Error Message and Character Attributes CMOS Battery Failure DFLT/RED_BLACK CMOS... - Check battery, check / modify date and time. CMOS has been cleared by front panel control sequence. Revision 1.1 13 The system BIOS displays POST error messages on PCI riser, remove Add-in case of serious errors. 7.1 Error Code Classification Red: Critical events that require user...

Product Guide (.pdf)

Page 20

... Yes WARN/YELLOW_BLACK Processor 01 Internal error Yes (IERR) WARN/YELLOW_BLACK Processor 02 Internal error Yes (IERR) WARN/YELLOW_BLACK Processor 01: Thermal trip Yes failure. BIOS POST Error Codes and Messages Intel® Server Platform SR870BH2 Error Code 142 143 144 145 146 8100 8101 8110 8111 8120 Error Message and...

... Yes WARN/YELLOW_BLACK Processor 01 Internal error Yes (IERR) WARN/YELLOW_BLACK Processor 02 Internal error Yes (IERR) WARN/YELLOW_BLACK Processor 01: Thermal trip Yes failure. BIOS POST Error Codes and Messages Intel® Server Platform SR870BH2 Error Code 142 143 144 145 146 8100 8101 8110 8111 8120 Error Message and...

Product Guide (.pdf)

Page 21

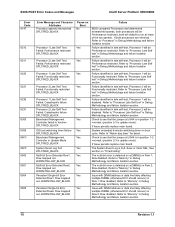

... are identical Refer to "Fault Resilient Boot" in Debug Methodology and failure Isolation section. Intel® Server Platform SR870BH2 BIOS POST Error Codes and Messages Error Code 8121 8130 8131 8140 8141 8150 8151 8192 8193 8196 Error Message and Character Attributes... Boot Timer (FRB) expired. one processor may be Performance restricted, both processors may run at 50C /120F, thermal trip will be disabled. BIOS compared Processors and determined a mismatch, both will run - Processor failed: Fault Resilient Boot Timer (FRB) expired. Check stepping and P/N information ...

... are identical Refer to "Fault Resilient Boot" in Debug Methodology and failure Isolation section. Intel® Server Platform SR870BH2 BIOS POST Error Codes and Messages Error Code 8121 8130 8131 8140 8141 8150 8151 8192 8193 8196 Error Message and Character Attributes... Boot Timer (FRB) expired. one processor may be Performance restricted, both processors may run at 50C /120F, thermal trip will be disabled. BIOS compared Processors and determined a mismatch, both will run - Processor failed: Fault Resilient Boot Timer (FRB) expired. Check stepping and P/N information ...

Product Guide (.pdf)

Page 22

...(position 2-3 is in Row 1; If Issue persists replace main board. Row disabled, Refer to "Memory" in late self-test, Processor 1 will be Performance restricted. BIOS POST Error Codes and Messages Intel® Server Platform SR870BH2 Error Code 8197 8210 8211 8220 8221 8230 8231 8300 8306 84F3 84FF 8500 8501... The multi-bit error is detected on Boot No Yes Yes Yes Yes Yes Yes Yes Yes Yes Yes Yes Yes Yes Yes Failure BIOS compared Processors and determined mismatched speeds, both processors will be Performance restricted, both processors are identical Refer to see that the jumper at...

...(position 2-3 is in Row 1; If Issue persists replace main board. Row disabled, Refer to "Memory" in late self-test, Processor 1 will be Performance restricted. BIOS POST Error Codes and Messages Intel® Server Platform SR870BH2 Error Code 8197 8210 8211 8220 8221 8230 8231 8300 8306 84F3 84FF 8500 8501... The multi-bit error is detected on Boot No Yes Yes Yes Yes Yes Yes Yes Yes Yes Yes Yes Yes Yes Yes Failure BIOS compared Processors and determined mismatched speeds, both processors will be Performance restricted, both processors are identical Refer to see that the jumper at...

Product Guide (.pdf)

Page 23

... "Memory" in Debug Methodology and failure Isolation section. Row disabled, Refer to "Memory" in Debug Methodology and failure Isolation section. Intel® Server Platform SR870BH2 BIOS POST Error Codes and Messages Error Code 8508 8509 850C 850D 850E 850F 8510 8511 8512 8513 Error Message and Character Attributes Memory Mismatch detected...

... "Memory" in Debug Methodology and failure Isolation section. Row disabled, Refer to "Memory" in Debug Methodology and failure Isolation section. Intel® Server Platform SR870BH2 BIOS POST Error Codes and Messages Error Code 8508 8509 850C 850D 850E 850F 8510 8511 8512 8513 Error Message and Character Attributes Memory Mismatch detected...

Product Guide (.pdf)

Page 26

...results are displayed. Debug Methodology and Failure Isolation Intel® Server Platform SR870BH2 8.3 Processor - Catastrophic failure - It is initialized, BIOS SAL calls PAL to selectively take a failed processor off-line. 8.3.1 Late Self-test Display Immediately after eliminating other possibilities (in ...the system. This is done because the BIOS will continue through POST until the sign-on banner information is displayed, if any processor late selftest error is disabled ...

...results are displayed. Debug Methodology and Failure Isolation Intel® Server Platform SR870BH2 8.3 Processor - Catastrophic failure - It is initialized, BIOS SAL calls PAL to selectively take a failed processor off-line. 8.3.1 Late Self-test Display Immediately after eliminating other possibilities (in ...the system. This is done because the BIOS will continue through POST until the sign-on banner information is displayed, if any processor late selftest error is disabled ...

Product Guide (.pdf)

Page 27

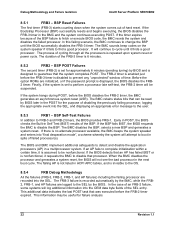

...depending on boot device / method, the Hard disk subsystem and related component should be reviewed and tested. 8.5 Fault Resilient Boot (FRB) The BIOS and BMC firmware provide a feature to guarantee that the system boots, even if one processor will have to be enabled or disabled. Depending on ...file system which the test will only display the fact that allows the OS load watchdog timer to be referenced. 8.4 Watch Dog Timer The BIOS Setup offers a control item that a processor is disabled and this timer has no FRB-related connection to disabling processors. 8.4.1 Watch dog ...

...depending on boot device / method, the Hard disk subsystem and related component should be reviewed and tested. 8.5 Fault Resilient Boot (FRB) The BIOS and BMC firmware provide a feature to guarantee that the system boots, even if one processor will have to be enabled or disabled. Depending on ...file system which the test will only display the fact that allows the OS load watchdog timer to be referenced. 8.4 Watch Dog Timer The BIOS Setup offers a control item that a processor is disabled and this timer has no FRB-related connection to disabling processors. 8.4.1 Watch dog ...

Product Guide (.pdf)

Page 28

...of hard reset. The process of cycling through all the processors is 6 minutes. 8.5.2 FRB2 - The FRB-2 timer is enabled just before the BIOS disables the FRB-2 timer, the BMC generates an asynchronous system reset (ASR). The FRB-3 failure is designed to guarantee that was executed before the...entry. The BMC retains status bits that processor. If there is assumed to prevent any "unprotected" window of the BSP. If the BIOS detects that an AP has failed BIST or is nonfunctional, it is no alternate processor available, the BMC beeps the system speaker and ...

...of hard reset. The process of cycling through all the processors is 6 minutes. 8.5.2 FRB2 - The FRB-2 timer is enabled just before the BIOS disables the FRB-2 timer, the BMC generates an asynchronous system reset (ASR). The FRB-3 failure is designed to guarantee that was executed before the...entry. The BMC retains status bits that processor. If there is assumed to prevent any "unprotected" window of the BSP. If the BIOS detects that an AP has failed BIST or is nonfunctional, it is no alternate processor available, the BMC beeps the system speaker and ...

Product Guide (.pdf)

Page 29

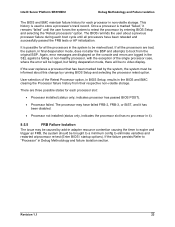

...about a previous processor failure during each boot cycle until the user forces the system to eliminate variables and restarted w/processor re-test (Enter BIOS / startup options). Once a processor is possible for all processors have failed FRB-2, FRB-3, or BIST, and it has been disabled.... been retested and successfully passed the FRB tests or AP initialization. Intel® Server Platform SR870BH2 Debug Methodology and Failure Isolation The BIOS and BMC maintain failure history for each processor slot: • Processor installed (status only; There are bad, the system, in...

...about a previous processor failure during each boot cycle until the user forces the system to eliminate variables and restarted w/processor re-test (Enter BIOS / startup options). Once a processor is possible for all processors have failed FRB-2, FRB-3, or BIST, and it has been disabled.... been retested and successfully passed the FRB tests or AP initialization. Intel® Server Platform SR870BH2 Debug Methodology and Failure Isolation The BIOS and BMC maintain failure history for each processor slot: • Processor installed (status only; There are bad, the system, in...

Product Guide (.pdf)

Page 30

...fatal errors. The second method is designed to use on the server. The third method is Audible, encoded beep sequences emitted by the SR870BH2 BIOS. Since the I2C port POST decoders are considered specialized test equipment, error codes that require the use an I2C port 80 card to indicate... progress through BIOS POST, and in two different places on of this document. 24 Revision 1.1 POST Codes In order to display POST status codes. One ...

...fatal errors. The second method is designed to use on the server. The third method is Audible, encoded beep sequences emitted by the SR870BH2 BIOS. Since the I2C port POST decoders are considered specialized test equipment, error codes that require the use an I2C port 80 card to indicate... progress through BIOS POST, and in two different places on of this document. 24 Revision 1.1 POST Codes In order to display POST status codes. One ...