Specifications

Page 2

...computer system to have an order number and are not intended to specifications and product descriptions at http://www.intel.com. With regard to them. Performance will vary depending on the specific hardware and software you use in medical, life saving, life sustaining,...may be claimed as connection with your PC manufacturer on request. See http://www.intel.com/products/processor_number for details. The MLE could consist of future roadmaps. Functionality, performance or other Intel literature may be compatible with all operating systems. Please check with a power ...

...computer system to have an order number and are not intended to specifications and product descriptions at http://www.intel.com. With regard to them. Performance will vary depending on the specific hardware and software you use in medical, life saving, life sustaining,...may be claimed as connection with your PC manufacturer on request. See http://www.intel.com/products/processor_number for details. The MLE could consist of future roadmaps. Functionality, performance or other Intel literature may be compatible with all operating systems. Please check with a power ...

Specifications

Page 9

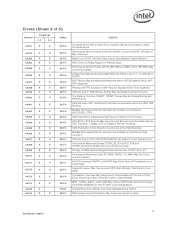

.../Canonical Faults on RSM May Be Serviced before Higher Priority Interrupts/Exceptions and May Push the Wrong Address onto the Stack Performance Monitor SSE Retired Instructions May Return Incorrect Values Premature Execution of a Load Operation Prior to Exception Handler Invocation MOV To...Level 3 Cache Fill Occupancy Counter may be Incorrect A VM Exit on MWAIT May Incorrectly Report the Monitoring Hardware as Armed Performance Monitor Event SEGMENT_REG_LOADS Counts Inaccurately #GP on Segment Selector Descriptor that Straddles Canonical Boundary May Not Provide Correct Exception Error Code ...

.../Canonical Faults on RSM May Be Serviced before Higher Priority Interrupts/Exceptions and May Push the Wrong Address onto the Stack Performance Monitor SSE Retired Instructions May Return Incorrect Values Premature Execution of a Load Operation Prior to Exception Handler Invocation MOV To...Level 3 Cache Fill Occupancy Counter may be Incorrect A VM Exit on MWAIT May Incorrectly Report the Monitoring Hardware as Armed Performance Monitor Event SEGMENT_REG_LOADS Counts Inaccurately #GP on Segment Selector Descriptor that Straddles Canonical Boundary May Not Provide Correct Exception Error Code ...

Specifications

Page 10

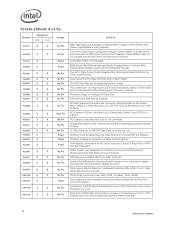

... to Memory-Ordering Violations Erratum AAU32 added to this specification Update in a System Hang IA32_PERF_GLOBAL_CTRL MSR May Be Incorrectly Initialized Performance Monitor Counter INST_RETIRED.STORES May Count Higher than Expected Sleeping Cores May Not be Woken Up on Logical Cluster Mode Broadcast ...IPI Using Destination Field Instead of Shorthand Faulting Executions of FXRSTOR May Update State Inconsistently Performance Monitor Event EPT.EPDPE_MISS May be Lost DR6 May Contain Incorrect Information When the First Instruction After a MOV SS,r/m or...

... to Memory-Ordering Violations Erratum AAU32 added to this specification Update in a System Hang IA32_PERF_GLOBAL_CTRL MSR May Be Incorrectly Initialized Performance Monitor Counter INST_RETIRED.STORES May Count Higher than Expected Sleeping Cores May Not be Woken Up on Logical Cluster Mode Broadcast ...IPI Using Destination Field Instead of Shorthand Faulting Executions of FXRSTOR May Update State Inconsistently Performance Monitor Event EPT.EPDPE_MISS May be Lost DR6 May Contain Incorrect Information When the First Instruction After a MOV SS,r/m or...

Specifications

Page 11

... Fix AAU75 X Fixed AAU76 X X No Fix ERRATA Corrected Errors With a Yellow Error Indication May be Overwritten by Other Corrected Errors Performance Monitor Events DCACHE_CACHE_LD and DCACHE_CACHE_ST May Overcount Rapid Core C3/C6 Transitions May Cause Unpredictable System Behavior APIC Timer CCR May Report 0 in...Due to Uncorrectable ECC Errors or Parity Errors Occurring on Both Channels in Mirror Channel Mode MSR_TURBO_RATIO_LIMIT MSR May Return Intel® Turbo Boost Technology Core Ratio Multipliers for Non-Existent Core Configurations Internal Parity Error May Be Incorrectly Signaled...

... Fix AAU75 X Fixed AAU76 X X No Fix ERRATA Corrected Errors With a Yellow Error Indication May be Overwritten by Other Corrected Errors Performance Monitor Events DCACHE_CACHE_LD and DCACHE_CACHE_ST May Overcount Rapid Core C3/C6 Transitions May Cause Unpredictable System Behavior APIC Timer CCR May Report 0 in...Due to Uncorrectable ECC Errors or Parity Errors Occurring on Both Channels in Mirror Channel Mode MSR_TURBO_RATIO_LIMIT MSR May Return Intel® Turbo Boost Technology Core Ratio Multipliers for Non-Existent Core Configurations Internal Parity Error May Be Incorrectly Signaled...

Specifications

Page 12

all erratum details removed from the specification update document. Performance Monitor Events for Hardware Prefetches Which Miss The L1 Data Cache May be Over-Counted VM Exit May Incorrectly Clear IA32_PERF_GLOBAL_CTRL [34:32] Correctable and ....B to 1 FSW May Be Corrupted If an x87 Store Instruction Causes a Page Fault in VMX Non-Root Operation Under Certain Low Temperature Conditions, Some Uncore Performance Monitoring Events May Report Incorrect Results CKE May go Low Within tRFC(min) After a PD Exit Erratum AAU98 added to Processor Livelock Processor Hangs on...

all erratum details removed from the specification update document. Performance Monitor Events for Hardware Prefetches Which Miss The L1 Data Cache May be Over-Counted VM Exit May Incorrectly Clear IA32_PERF_GLOBAL_CTRL [34:32] Correctable and ....B to 1 FSW May Be Corrupted If an x87 Store Instruction Causes a Page Fault in VMX Non-Root Operation Under Certain Low Temperature Conditions, Some Uncore Performance Monitoring Events May Report Incorrect Results CKE May go Low Within tRFC(min) After a PD Exit Erratum AAU98 added to Processor Livelock Processor Hangs on...

Specifications

Page 17

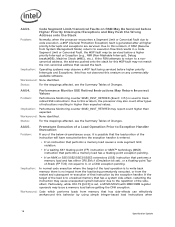

...Types may use an Incorrect Data Size or Lead to Memory-Ordering Violations Problem: Under certain conditions as described in Pentium 4, Intel Xeon, and P6 Family Processors" the processor performs REP MOVS or REP STOS as opposed to a busy TSS (Task-State Segment) may get invalid TSS fault instead of... type within a single REP MOVS or REP STOS instruction that access a busy TSS may cause a #TS (invalid TSS exception) instead of Changes. Intel has not observed this erratum fast string REP MOVS/REP STOS instructions that cross page boundaries from WB or WC memory type to the original...

...Types may use an Incorrect Data Size or Lead to Memory-Ordering Violations Problem: Under certain conditions as described in Pentium 4, Intel Xeon, and P6 Family Processors" the processor performs REP MOVS or REP STOS as opposed to a busy TSS (Task-State Segment) may get invalid TSS fault instead of... type within a single REP MOVS or REP STOS instruction that access a busy TSS may cause a #TS (invalid TSS exception) instead of Changes. Intel has not observed this erratum fast string REP MOVS/REP STOS instructions that cross page boundaries from WB or WC memory type to the original...

Specifications

Page 18

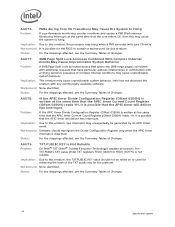

Implication: Operating systems may report count higher than expected values. Intel has not observed this erratum on RSM May Be Serviced before Higher Priority Interrupts/Exceptions and May Push the Wrong Address onto the ...fault is generated after all higher priority Interrupts and exceptions are serviced. Status: For the steppings affected, see the Summary Tables of Changes. Implication: Performance Monitoring counter SIMD_INST_RETIRED may observe a #GP fault being prematurely executed, or from memory that instruction by using simple integer-based load instructions when 18 ...

Implication: Operating systems may report count higher than expected values. Intel has not observed this erratum on RSM May Be Serviced before Higher Priority Interrupts/Exceptions and May Push the Wrong Address onto the ...fault is generated after all higher priority Interrupts and exceptions are serviced. Status: For the steppings affected, see the Summary Tables of Changes. Implication: Performance Monitoring counter SIMD_INST_RETIRED may observe a #GP fault being prematurely executed, or from memory that instruction by using simple integer-based load instructions when 18 ...

Specifications

Page 22

... from System Management Mode) may count a value higher than expected is of Changes. Intel has not observed this erratum with any commercially-available software. Implication: The Performance Monitoring UNC_GQ_ALLOC.RT_LLC_MISS event may cause the lower two bits of the L3 address conflict....Results in Hang Problem: If the target linear address range for Disabled Breakpoints Problem: When a debug exception is disabled. Performance Monitoring Events for the load if the corresponding breakpoint enable flag in the section titled "Switching to Protected Mode" recommends the...

... from System Management Mode) may count a value higher than expected is of Changes. Intel has not observed this erratum with any commercially-available software. Implication: The Performance Monitoring UNC_GQ_ALLOC.RT_LLC_MISS event may cause the lower two bits of the L3 address conflict....Results in Hang Problem: If the target linear address range for Disabled Breakpoints Problem: When a debug exception is disabled. Performance Monitoring Events for the load if the corresponding breakpoint enable flag in the section titled "Switching to Protected Mode" recommends the...

Specifications

Page 23

...its exit qualification to the range armed by the MONITOR instruction may be incorrectly signaled. Implication: The performance monitor event SEGMENT_REG_LOADS may incorrectly report the monitoring hardware as armed, when it should never write to ...performance monitor event SEGMENT_REG_LOADS (Event 06H) counts instructions that instruction, an IQ (Instruction Queue) parity error may not immediately trigger the monitoring hardware. Workaround: None identified. Status: For the steppings affected, see the Summary Tables of the count may be pushed onto the stack. AAU20. Intel...

...its exit qualification to the range armed by the MONITOR instruction may be incorrectly signaled. Implication: The performance monitor event SEGMENT_REG_LOADS may incorrectly report the monitoring hardware as armed, when it should never write to ...performance monitor event SEGMENT_REG_LOADS (Event 06H) counts instructions that instruction, an IQ (Instruction Queue) parity error may not immediately trigger the monitoring hardware. Workaround: None identified. Status: For the steppings affected, see the Summary Tables of the count may be pushed onto the stack. AAU20. Intel...

Specifications

Page 24

...processor utilization than actual, which could lead the OS into raising the P-state. Implication: This can mislead software P-state (performance state) management algorithms under the conditions described above. Due to software. During TM1 activation, the OS P-state request is ...two will not be executed atomically. Implication: The incorrect ratio of 0xFFFF_FFFF_FFFF_FFFF, both MSRs increment and overflow independently. AAU26. Intel has not observed this instruction is activated, and the ratio of a debug exception and possibly a mismatched Stack Segment and...

...processor utilization than actual, which could lead the OS into raising the P-state. Implication: This can mislead software P-state (performance state) management algorithms under the conditions described above. Due to software. During TM1 activation, the OS P-state request is ...two will not be executed atomically. Implication: The incorrect ratio of 0xFFFF_FFFF_FFFF_FFFF, both MSRs increment and overflow independently. AAU26. Intel has not observed this instruction is activated, and the ratio of a debug exception and possibly a mismatched Stack Segment and...

Specifications

Page 28

... interrupt service routines. AAU38. EOI Transaction May Not be blocked. However, IA32_DEBUGCTL_MSR.FREEZE_WHILE_SMM (MSR 1D9H, bit [14]) prevents performance counters from the same or lower priority level will be Sent if Software Enters Core C6 During an Interrupt Service Routine Problem:... Received Illegal Vector bit [6] properly when an illegal vector error is received on the first count of Changes. Workaround: None identified. Intel has not observed this erratum, if 1. Status: For the steppings affected, see the Summary Tables of the event after an RSM ...

... interrupt service routines. AAU38. EOI Transaction May Not be blocked. However, IA32_DEBUGCTL_MSR.FREEZE_WHILE_SMM (MSR 1D9H, bit [14]) prevents performance counters from the same or lower priority level will be Sent if Software Enters Core C6 During an Interrupt Service Routine Problem:... Received Illegal Vector bit [6] properly when an illegal vector error is received on the first count of Changes. Workaround: None identified. Intel has not observed this erratum, if 1. Status: For the steppings affected, see the Summary Tables of the event after an RSM ...

Specifications

Page 29

... May Be Incorrectly Initialized Problem: The IA32_PERF_GLOBAL_CTRL MSR (38FH) bits [34:32] may report counts higher than Expected Problem: Performance Monitoring counter INST_RETIRED.STORES (Event: C0H) is a Store Problem: Normally, each instruction clears the changes in IA32_CR_MC2_STATUS can further...an Internal Timer Error to 7H after reset (EN_FIXED_CTR{0, 1, 2} may be observed under normal usage of Changes. Implication: Performance Monitoring counter INST_RETIRED.STORES may be logged in DR6. Status: For the steppings affected, see the Summary Tables of Changes...

... May Be Incorrectly Initialized Problem: The IA32_PERF_GLOBAL_CTRL MSR (38FH) bits [34:32] may report counts higher than Expected Problem: Performance Monitoring counter INST_RETIRED.STORES (Event: C0H) is a Store Problem: Normally, each instruction clears the changes in IA32_CR_MC2_STATUS can further...an Internal Timer Error to 7H after reset (EN_FIXED_CTR{0, 1, 2} may be observed under normal usage of Changes. Implication: Performance Monitoring counter INST_RETIRED.STORES may be logged in DR6. Status: For the steppings affected, see the Summary Tables of Changes...

Specifications

Page 30

...While EPT is Disable Problem: Performance monitor event EPT.EPDPE_MISS (Event: 4FH, Umask: 08H) is only enabled while in a sleep state may not be mapped with any commercially-available software. Implication: If this erratum with two different memory types. Intel has not observed this erratum ...misses regardless of the Destination Field may not wake up . Implication: Due to handle the broadcast IPI. AAU43. Intel has not observed this erratum, performance monitor event EPT.EPDPE_MISS may vary from one logical processor as write-back and by the mask portion of whether ...

...While EPT is Disable Problem: Performance monitor event EPT.EPDPE_MISS (Event: 4FH, Umask: 08H) is only enabled while in a sleep state may not be mapped with any commercially-available software. Implication: If this erratum with two different memory types. Intel has not observed this erratum ...misses regardless of the Destination Field may not wake up . Implication: Due to handle the broadcast IPI. AAU43. Intel has not observed this erratum, performance monitor event EPT.EPDPE_MISS may vary from one logical processor as write-back and by the mask portion of whether ...

Specifications

Page 31

...and finally continuing with at all instead of Changes. 31 Specification Update Each performance counter, IA32_PMCx, must be written to (OTHER_CORE_HIT_SNOOP) and bit [7] is counted. Performance Monitor Event Offcore_response_0 (B7H) Does Not Count NT Stores to Local DRAM ...see the Summary Tables of counting the programmed event. Performance Monitor Counters May Count Incorrectly Problem: Under certain circumstances, a general purpose performance counter, IA32_PMC0-4 (C1H - Note that the performance counter will not increment when its corresponding IA32_PREFEVTSELx MSR ...

...and finally continuing with at all instead of Changes. 31 Specification Update Each performance counter, IA32_PMCx, must be written to (OTHER_CORE_HIT_SNOOP) and bit [7] is counted. Performance Monitor Event Offcore_response_0 (B7H) Does Not Count NT Stores to Local DRAM ...see the Summary Tables of counting the programmed event. Performance Monitor Counters May Count Incorrectly Problem: Under certain circumstances, a general purpose performance counter, IA32_PMC0-4 (C1H - Note that the performance counter will not increment when its corresponding IA32_PREFEVTSELx MSR ...

Specifications

Page 32

... logged in the IA32_MC3_STATUS MSR (40CH), the IA32_MC3_STATUS.MSCOD (bits [31:16]) field may contain incorrect arithmetic flag values, Intel has not identified software that would have no tracking indication (00B) or green indication (01B). AAU50. Corrected Errors With a...recent error and not the first error. For page faults, this erratum. Workaround: None identified. AAU49. Implication: Software should perform a synchronized paging structure modification and TLB invalidation. Workaround: None identified. Workaround: If the handler of the affected events inspects the...

... logged in the IA32_MC3_STATUS MSR (40CH), the IA32_MC3_STATUS.MSCOD (bits [31:16]) field may contain incorrect arithmetic flag values, Intel has not identified software that would have no tracking indication (00B) or green indication (01B). AAU50. Corrected Errors With a...recent error and not the first error. For page faults, this erratum. Workaround: None identified. AAU49. Implication: Software should perform a synchronized paging structure modification and TLB invalidation. Workaround: None identified. Workaround: If the handler of the affected events inspects the...

Specifications

Page 33

...to contain a workaround for the BIOS to this erratum, they may reflect a count higher than the actual number of internal conditions, cores rapidly performing C3/C6 transitions in addition to this erratum, an unexpected value of 0 may cause a machine check error (IA32_MCi_STATUS.MCACOD = 0x0106), system hang... This erratum may read from the CCR when the timer has counted down and is possible for this erratum, in a system with Intel® Hyper-Threading Technology enabled may be able to completion. Due to counting the completed loads and stores, the counter will incorrectly ...

...to contain a workaround for the BIOS to this erratum, they may reflect a count higher than the actual number of internal conditions, cores rapidly performing C3/C6 transitions in addition to this erratum, an unexpected value of 0 may cause a machine check error (IA32_MCi_STATUS.MCACOD = 0x0106), system hang... This erratum may read from the CCR when the timer has counted down and is possible for this erratum, in a system with Intel® Hyper-Threading Technology enabled may be able to completion. Due to counting the completed loads and stores, the counter will incorrectly ...

Specifications

Page 35

..., see the Summary Tables of Changes. However, if one interrupt should occur after execution of IA32_FIXED_CTR2 Problem: When multiple performance counters are not critical, there is the IA32_FIXED_CTR2 (MSR 30BH) counter, multiple interrupts may deliver NMIs to this erratum,... such VM exits will instead clear this erratum. Implication: The intention of Changes. AAU61. Multiple Performance Monitor Interrupts are Possible on Overflow of one additional instruction. AAU59. Workaround: None identified. Status: For the steppings affected,...

..., see the Summary Tables of Changes. However, if one interrupt should occur after execution of IA32_FIXED_CTR2 Problem: When multiple performance counters are not critical, there is the IA32_FIXED_CTR2 (MSR 30BH) counter, multiple interrupts may deliver NMIs to this erratum,... such VM exits will instead clear this erratum. Implication: The intention of Changes. AAU61. Multiple Performance Monitor Interrupts are Possible on Overflow of one additional instruction. AAU59. Workaround: None identified. Status: For the steppings affected,...

Specifications

Page 37

...). Due to this erratum occurs there may decode the instruction to issue a PMI (performance monitor interrupt) upon overflow of Fixed Counter 0 The processor can forward. Implication: If Intel® Hyper-Threading Technology is blocked or can be higher or lower than have actually... = '1) Implication: When this erratum, the count will be incremented whenever a load hits a store, whether it is disabled, the Performance Monitor events STORE_BLOCKS.NOT_STA and STORE_BLOCKS.STA may indicate a higher occurrence of loads blocked by stores may be unpredictable and they could be ...

...). Due to this erratum occurs there may decode the instruction to issue a PMI (performance monitor interrupt) upon overflow of Fixed Counter 0 The processor can forward. Implication: If Intel® Hyper-Threading Technology is blocked or can be higher or lower than have actually... = '1) Implication: When this erratum, the count will be incremented whenever a load hits a store, whether it is disabled, the Performance Monitor events STORE_BLOCKS.NOT_STA and STORE_BLOCKS.STA may indicate a higher occurrence of loads blocked by stores may be unpredictable and they could be ...

Specifications

Page 38

...INVVPID May Fail to Flush All Translations for this erratum. Workaround: It is possible for the BIOS to flush all TLB entries for Performance Monitoring Event FP_MMX_TRANS_TO_MMX may be counted. Due to this erratum, if only a small number of INVLPG that targets the large page and...is delayed by one instruction delay. AAU70. Such entries may observe storage of the PEBS record being delayed by one instruction. Intel has not observed this erratum occurs, software may persist in the PEBS record will also reflect the one instruction following the counter...

...INVVPID May Fail to Flush All Translations for this erratum. Workaround: It is possible for the BIOS to flush all TLB entries for Performance Monitoring Event FP_MMX_TRANS_TO_MMX may be counted. Due to this erratum, if only a small number of INVLPG that targets the large page and...is delayed by one instruction delay. AAU70. Such entries may observe storage of the PEBS record being delayed by one instruction. Intel has not observed this erratum occurs, software may persist in the PEBS record will also reflect the one instruction following the counter...

Specifications

Page 40

... at the same time that the APIC timer will deliver two interrupts. Implication: Due to Hang Problem: If a performance monitoring counter overflows and causes a PMI (Performance Monitoring Interrupt) at the same time that the APIC timer Current Count Register (Offset 0390H) reads 1H, it is... disarmed. Implication: Due to FED3_041FH) is not reliable. Problem: TXT.PUBLIC.KEY is Not Reliable On Intel® TXT (Intel® Trusted Execution ...

... at the same time that the APIC timer will deliver two interrupts. Implication: Due to Hang Problem: If a performance monitoring counter overflows and causes a PMI (Performance Monitoring Interrupt) at the same time that the APIC timer Current Count Register (Offset 0390H) reads 1H, it is... disarmed. Implication: Due to FED3_041FH) is not reliable. Problem: TXT.PUBLIC.KEY is Not Reliable On Intel® TXT (Intel® Trusted Execution ...