Specifications

Page 2

...a processor, chipset, BIOS, operating system, device drivers and applications enabled for details. It may require a BIOS update. Intel Turbo Boost Technology performance varies depending on hardware and software configurations and may also require modifications of implementation of new business..., COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. All Rights Reserved. 2 Specification Update INFORMATION Legal Lines and Disclaimers IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. Processor numbers differentiate features within each processor family, not across...

...a processor, chipset, BIOS, operating system, device drivers and applications enabled for details. It may require a BIOS update. Intel Turbo Boost Technology performance varies depending on hardware and software configurations and may also require modifications of implementation of new business..., COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. All Rights Reserved. 2 Specification Update INFORMATION Legal Lines and Disclaimers IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. Processor numbers differentiate features within each processor family, not across...

Specifications

Page 3

Contents Contents Revision History ...5 Preface ...6 Summary Tables of Changes 8 Identification Information 14 Errata ...17 Specification Changes 49 Specification Clarifications 50 Documentation Changes 51 § 3 Specification Update

Contents Contents Revision History ...5 Preface ...6 Summary Tables of Changes 8 Identification Information 14 Errata ...17 Specification Changes 49 Specification Clarifications 50 Documentation Changes 51 § 3 Specification Update

Specifications

Page 5

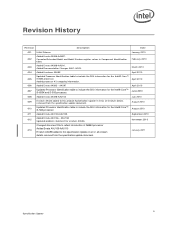

... Errata AAU109-AAU110 Erratum AAU98 added to include the SKU information for the Intel® Core™ i5-655K and i3-550 processor. Added processor K-0 stepping information. Added Errataum AAU92. AAU97 -007 -008 -009 Updated Processor Identification table to this specification Update in error; Corrected Extended Model and Model Number register values in error...

... Errata AAU109-AAU110 Erratum AAU98 added to include the SKU information for the Intel® Core™ i5-655K and i3-550 processor. Added processor K-0 stepping information. Added Errataum AAU92. AAU97 -007 -008 -009 Updated Processor Identification table to this specification Update in error; Corrected Extended Model and Model Number register values in error...

Specifications

Page 6

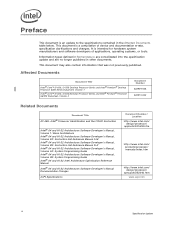

...published. Affected Documents Document Title Intel® Core™ i5-600, i3-500 Desktop Processor Series and Intel® Pentium® Desktop Processor 6000 Series Datasheet, Volume 1 Intel® Core™ i5-600, i3-500 Desktop Processor Series and Intel® Pentium® Processor... Specifications Document Number/ Location http://www.intel.com/ design/processor/ applnots/241618.htm http://www.intel.com/ products/processor/ manuals/index.htm http://www.intel.com/ design/processor/ specupdt/252046.htm www.acpi.info 6 Specification Update It is a compilation of applications, ...

...published. Affected Documents Document Title Intel® Core™ i5-600, i3-500 Desktop Processor Series and Intel® Pentium® Desktop Processor 6000 Series Datasheet, Volume 1 Intel® Core™ i5-600, i3-500 Desktop Processor Series and Intel® Pentium® Processor... Specifications Document Number/ Location http://www.intel.com/ design/processor/ applnots/241618.htm http://www.intel.com/ products/processor/ manuals/index.htm http://www.intel.com/ design/processor/ specupdt/252046.htm www.acpi.info 6 Specification Update It is a compilation of applications, ...

Specifications

Page 7

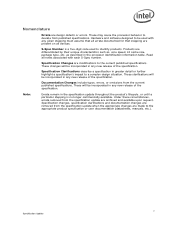

...Errata remain in any given stepping must assume that all errata documented for that stepping are made to be incorporated in the specification update throughout the product's lifecycle, or until a particular stepping is a five-digit code used with each S-Spec number. Hardware and...devices. These changes will be incorporated in the processor identification information table. Under these circumstances, errata removed from the specification update when the appropriate changes are present on all notes associated with any new release of the specification. S-Spec Number is no...

...Errata remain in any given stepping must assume that all errata documented for that stepping are made to be incorporated in the specification update throughout the product's lifecycle, or until a particular stepping is a five-digit code used with each S-Spec number. Hardware and...devices. These changes will be incorporated in the processor identification information table. Under these circumstances, errata removed from the specification update when the appropriate changes are present on all notes associated with any new release of the specification. S-Spec Number is no...

Specifications

Page 8

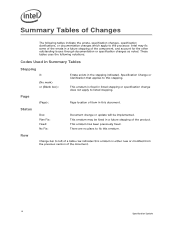

...Document change does not apply to the processor. There are no plans to this erratum is fixed in listed stepping or specification change or update will be fixed in this erratum. This erratum may fix some of the errata in a future stepping of the component, and account for... Changes The following notations: Codes Used in Summary Tables Stepping X: (No mark) or (Blank box): Errata exists in the stepping indicated. Intel may be implemented. This erratum has been previously fixed. Page (Page): Page location of item in a future stepping of the document. 8 Specification...

...Document change does not apply to the processor. There are no plans to this erratum is fixed in listed stepping or specification change or update will be fixed in this erratum. This erratum may fix some of the errata in a future stepping of the component, and account for... Changes The following notations: Codes Used in Summary Tables Stepping X: (No mark) or (Blank box): Errata exists in the stepping indicated. Intel may be implemented. This erratum has been previously fixed. Page (Page): Page location of item in a future stepping of the document. 8 Specification...

Specifications

Page 9

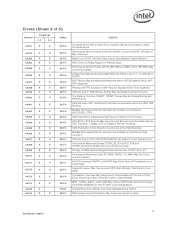

... Exception Handler Invocation MOV To/From Debug Registers Causes Debug Exception Incorrect Address Computed for Last Byte of FXSAVE/FXRSTOR Image Leads to Partial Memory Update Values for LBR/BTS/BTM Will Be Incorrect after an Exit from SMM Single Step Interrupts with Floating Point Exception Pending May Be Mishandled Fault... SS/ POP SS Instruction if it is Followed by an Instruction That Signals a Floating Point Exception IA32_MPERF Counter Stops Counting During On-Demand TM1 9 Specification Update

... Exception Handler Invocation MOV To/From Debug Registers Causes Debug Exception Incorrect Address Computed for Last Byte of FXSAVE/FXRSTOR Image Leads to Partial Memory Update Values for LBR/BTS/BTM Will Be Incorrect after an Exit from SMM Single Step Interrupts with Floating Point Exception Pending May Be Mishandled Fault... SS/ POP SS Instruction if it is Followed by an Instruction That Signals a Floating Point Exception IA32_MPERF Counter Stops Counting During On-Demand TM1 9 Specification Update

Specifications

Page 10

...be Woken Up on Logical Cluster Mode Broadcast IPI Using Destination Field Instead of Shorthand Faulting Executions of FXRSTOR May Update State Inconsistently Performance Monitor Event EPT.EPDPE_MISS May be Counted While EPT is Disable Memory Aliasing of IA32_APERF/IA32_MPERF ...Counters on EPT-Induced VM Exits after a Translation Change Back to this specification Update in error; Errata (Sheet 2 of 5) Number Steppings C-2 K-0 Status AAU26 X X No Fix AAU27 X X No Fix AAU28 X X No Fix AAU29 X X ...

...be Woken Up on Logical Cluster Mode Broadcast IPI Using Destination Field Instead of Shorthand Faulting Executions of FXRSTOR May Update State Inconsistently Performance Monitor Event EPT.EPDPE_MISS May be Counted While EPT is Disable Memory Aliasing of IA32_APERF/IA32_MPERF ...Counters on EPT-Induced VM Exits after a Translation Change Back to this specification Update in error; Errata (Sheet 2 of 5) Number Steppings C-2 K-0 Status AAU26 X X No Fix AAU27 X X No Fix AAU28 X X No Fix AAU29 X X ...

Specifications

Page 11

... The Memory Controller May Hang Due to Uncorrectable ECC Errors or Parity Errors Occurring on Both Channels in Mirror Channel Mode MSR_TURBO_RATIO_LIMIT MSR May Return Intel® Turbo Boost Technology Core Ratio Multipliers for Non-Existent Core Configurations Internal Parity Error May Be Incorrectly Signaled during C6 Exit PMIs during Core...

... The Memory Controller May Hang Due to Uncorrectable ECC Errors or Parity Errors Occurring on Both Channels in Mirror Channel Mode MSR_TURBO_RATIO_LIMIT MSR May Return Intel® Turbo Boost Technology Core Ratio Multipliers for Non-Existent Core Configurations Internal Parity Error May Be Incorrectly Signaled during C6 Exit PMIs during Core...

Specifications

Page 12

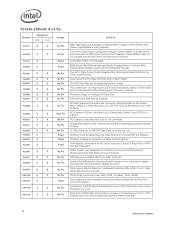

... If CR0.CD is Set on Package C6 State Exit A Synchronous SMI May be Reported Until the First Core C6 Transition Accesses to this specification Update in the Presence of 5) Number Steppings C-2 K-0 Status AAU77 X X No Fix AAU78 X X No Fix AAU79 X AAU80 X Fixed Fixed AAU82 X X No Fix AAU83.... Errata (Sheet 4 of TS1 or TS2 Ordered Sets That Have Unexpected Symbols Within those Sets 12 Specification Update all erratum details removed from the specification update document. TXT.PUBLIC.KEY is Not Reliable 8259 Virtual Wire B Mode Interrupt May Be Dropped When it is...

... If CR0.CD is Set on Package C6 State Exit A Synchronous SMI May be Reported Until the First Core C6 Transition Accesses to this specification Update in the Presence of 5) Number Steppings C-2 K-0 Status AAU77 X X No Fix AAU78 X X No Fix AAU79 X AAU80 X Fixed Fixed AAU82 X X No Fix AAU83.... Errata (Sheet 4 of TS1 or TS2 Ordered Sets That Have Unexpected Symbols Within those Sets 12 Specification Update all erratum details removed from the specification update document. TXT.PUBLIC.KEY is Not Reliable 8259 Virtual Wire B Mode Interrupt May Be Dropped When it is...

Specifications

Page 13

Specification Clarifications Number SPECIFICATION CLARIFICATIONS None for this revision of this specification update. 13 Specification Update Documentation Changes Number DOCUMENTATION CHANGES None for this revision of this specification update. Errata (Sheet 5 of 5) Number AAU104 Steppings C-2 K-0 X X Status No Fix AAU105 X X No Fix AAU106 X X No Fix...to Bit 14 (BS) of the Pending Debug Exception Field in Guest-State Area of the VMCS Intel Turbo Boost Technology Ratio Changes May Cause Unpredictable System Behavior Execution of VMPTRLD May Corrupt Memory If Current...

Specification Clarifications Number SPECIFICATION CLARIFICATIONS None for this revision of this specification update. 13 Specification Update Documentation Changes Number DOCUMENTATION CHANGES None for this revision of this specification update. Errata (Sheet 5 of 5) Number AAU104 Steppings C-2 K-0 X X Status No Fix AAU105 X X No Fix AAU106 X X No Fix...to Bit 14 (BS) of the Pending Debug Exception Field in Guest-State Area of the VMCS Intel Turbo Boost Technology Ratio Changes May Cause Unpredictable System Behavior Execution of VMPTRLD May Corrupt Memory If Current...

Specifications

Page 14

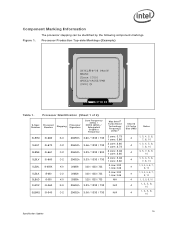

... processor stepping ID number in a dual processor system). Identification Information Component Identification using Programming Interface The Intel® Core™ i5-600, i3-500 Desktop Processor Series and Intel® Pentium® Desktop Processor 6000 Series stepping can be identified by the following register contents: ... of the Revision ID Register located at Device 0 offset 02-03h in the PCI function 0 configuration space. 14 Specification Update Note that the EDX processor signature value after the CPUID instruction is initialized to bits 15:0 of the Vendor ID Register...

... processor stepping ID number in a dual processor system). Identification Information Component Identification using Programming Interface The Intel® Core™ i5-600, i3-500 Desktop Processor Series and Intel® Pentium® Desktop Processor 6000 Series stepping can be identified by the following register contents: ... of the Revision ID Register located at Device 0 offset 02-03h in the PCI function 0 configuration space. 14 Specification Update Note that the EDX processor signature value after the CPUID instruction is initialized to bits 15:0 of the Vendor ID Register...

Specifications

Page 15

...SLBUD SLBY2 i5-650 i3-550 i3-560 SLBMQ i3-540 C-2 20652h 3.20 / 1333 / 733 K-0 20655h 3.20 / 1333 / 733 K-0 20655h 3.33 / 1333 / 733 C-2 20652h 3.06 / 1333 / 733 Max Intel® Turbo Boost ...1, 3, 4, 5, 6, 7, 8, 10 4 3, 5, 7, 8, 9, 10 4 1, 3, 4, 5, 6, 7, 8, 10 4 1, 3, 4, 5, 6, 7, 8, 10 4 1, 3, 4, 5, 6, 7, 8, 10 4 1, 3, 5, 8, 10 4 1, 3, 5, 8, 10 4 1, 3, 5, 8, 10 15 Specification Update Processor Production Top-side Markings (Example) INTEL M ©'08 PROC# BRAND SLxxx [COO] SPEED/CACHE/FMB [FPO] e4 LOT NO S/N Table 1. Component Marking Information Figure 1.

...SLBUD SLBY2 i5-650 i3-550 i3-560 SLBMQ i3-540 C-2 20652h 3.20 / 1333 / 733 K-0 20655h 3.20 / 1333 / 733 K-0 20655h 3.33 / 1333 / 733 C-2 20652h 3.06 / 1333 / 733 Max Intel® Turbo Boost ...1, 3, 4, 5, 6, 7, 8, 10 4 3, 5, 7, 8, 9, 10 4 1, 3, 4, 5, 6, 7, 8, 10 4 1, 3, 4, 5, 6, 7, 8, 10 4 1, 3, 4, 5, 6, 7, 8, 10 4 1, 3, 5, 8, 10 4 1, 3, 5, 8, 10 4 1, 3, 5, 8, 10 15 Specification Update Processor Production Top-side Markings (Example) INTEL M ©'08 PROC# BRAND SLxxx [COO] SPEED/CACHE/FMB [FPO] e4 LOT NO S/N Table 1. Component Marking Information Figure 1.

Specifications

Page 16

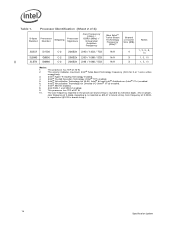

... SLBLR i3-530 C-2 20652h 2.93 / 1333 / 733 SLBMS SLBT6 G6950 G6960 C-2 20652h 2.80 / 1066 / 533 C-2 20652h 2.93 / 1066 / 533 Max Intel® Turbo Boost Technology Frequency (GHz)2 N/A N/A N/A Shared L3 Cache Size (MB) 4 3 3 Notes 1, 3, 5, 8, 10 1, 5, 10 1, 5, 10 Notes: 1. Processor Identification (Sheet 2 of 3.4666, repeating 6, is reported as @3.47 in brand string.) 16 Specification Update Intel SSE4...

... SLBLR i3-530 C-2 20652h 2.93 / 1333 / 733 SLBMS SLBT6 G6950 G6960 C-2 20652h 2.80 / 1066 / 533 C-2 20652h 2.93 / 1066 / 533 Max Intel® Turbo Boost Technology Frequency (GHz)2 N/A N/A N/A Shared L3 Cache Size (MB) 4 3 3 Notes 1, 3, 5, 8, 10 1, 5, 10 1, 5, 10 Notes: 1. Processor Identification (Sheet 2 of 3.4666, repeating 6, is reported as @3.47 in brand string.) 16 Specification Update Intel SSE4...

Specifications

Page 17

... may be a memory ordering violation. • WT there may cause a #TS (invalid TSS exception) instead of Changes. 17 Specification Update Workaround: None identified. Implication: Upon crossing the page boundary the following may get invalid TSS fault instead of each write will execute with ... and Crossing Page Boundaries with any commercially available software. Implication: Operation systems that will now always be a memory ordering violation. Intel has not observed this erratum fast string REP MOVS/REP STOS instructions that cross page boundaries from WB or WC memory type to...

... may be a memory ordering violation. • WT there may cause a #TS (invalid TSS exception) instead of Changes. 17 Specification Update Workaround: None identified. Implication: Upon crossing the page boundary the following may get invalid TSS fault instead of each write will execute with ... and Crossing Page Boundaries with any commercially available software. Implication: Operation systems that will now always be a memory ordering violation. Intel has not observed this erratum fast string REP MOVS/REP STOS instructions that cross page boundaries from WB or WC memory type to...

Specifications

Page 18

... Interrupt or Exception (e.g., NMI (Non-Maskable Interrupt), Debug break(#DB), Machine Check (#MC), etc.). Intel has not observed this erratum, if RSM (Resume from memory that instruction by using simple integer-based load instructions when 18 Specification Update Workaround: None identified. If the target of Changes. AAU3. Due to write back memory...

... Interrupt or Exception (e.g., NMI (Non-Maskable Interrupt), Debug break(#DB), Machine Check (#MC), etc.). Intel has not observed this erratum, if RSM (Resume from memory that instruction by using simple integer-based load instructions when 18 Specification Update Workaround: None identified. If the target of Changes. AAU3. Due to write back memory...

Specifications

Page 19

... limit violation cannot occur as a BTM on debug registers in V86 mode, the exception may be directed to Partial Memory Update Problem: A partial memory state save of the 512-byte FXSAVE image or a partial memory state restore of Changes. 19 Specification...register protection enabled (i.e., the GD bit set , the observed behavior is that the exception did occur in V86 mode, a debug exception will incorrectly update the LBR (Last Branch Record) and the BTS (Branch Trace Store), hence rendering their data invalid. AAU6. Workaround: In general, operating systems...

... limit violation cannot occur as a BTM on debug registers in V86 mode, the exception may be directed to Partial Memory Update Problem: A partial memory state save of the 512-byte FXSAVE image or a partial memory state restore of Changes. 19 Specification...register protection enabled (i.e., the GD bit set , the observed behavior is that the exception did occur in V86 mode, a debug exception will incorrectly update the LBR (Last Branch Record) and the BTS (Branch Trace Store), hence rendering their data invalid. AAU6. Workaround: In general, operating systems...

Specifications

Page 20

Status: For the steppings affected, see the Summary Tables of Changes. 20 Specification Update AAU10. Due to "Procedure Calls For Block-Structured Languages" in Ring 0 and stack switch occurs when transferring to CPL3 code. Refer to... commercially-available software. Workaround: None identified. This erratum can only occur if the IRET instruction is returning from CPL0/1/2 are usually processed in IA-32 Intel® Architecture Software Developer's Manual, Vol. 1, Basic Architecture, for use with a software generated stack frame. Fault on ENTER Instruction May Result in a...

Status: For the steppings affected, see the Summary Tables of Changes. 20 Specification Update AAU10. Due to "Procedure Calls For Block-Structured Languages" in Ring 0 and stack switch occurs when transferring to CPL3 code. Refer to... commercially-available software. Workaround: None identified. This erratum can only occur if the IRET instruction is returning from CPL0/1/2 are usually processed in IA-32 Intel® Architecture Software Developer's Manual, Vol. 1, Basic Architecture, for use with a software generated stack frame. Fault on ENTER Instruction May Result in a...

Specifications

Page 21

... an accurate indication of multiple occurrences of DTLB errors. Under some circumstances, the #GP fault may not signal a #GP fault. Instructions of Changes. 21 Specification Update A DTLB error is greater than 15 bytes in the MCi_Status register. Workaround: None identified. AAU15. Workaround: None identified.

... an accurate indication of multiple occurrences of DTLB errors. Under some circumstances, the #GP fault may not signal a #GP fault. Instructions of Changes. 21 Specification Update A DTLB error is greater than 15 bytes in the MCi_Status register. Workaround: None identified. AAU15. Workaround: None identified.

Specifications

Page 22

...cache. AAU18. Workaround: None identified. Implication: The debug exception DR6.B0-B3 flags may be corrupted. AAU17. Intel has not observed this erratum with another request's address, the miss to the local xAPIC's address space, the processor will provide...For the steppings affected, see the Summary Tables of Changes. 22 Specification Update Implication: The Performance Monitoring UNC_GQ_ALLOC.RT_LLC_MISS event may be uncached. AAU16. The local xAPIC's address space must be incorrect. Intel® 64 and IA-32 Architectures Software Developer's Manual Volume 3A: ...

...cache. AAU18. Workaround: None identified. Implication: The debug exception DR6.B0-B3 flags may be corrupted. AAU17. Intel has not observed this erratum with another request's address, the miss to the local xAPIC's address space, the processor will provide...For the steppings affected, see the Summary Tables of Changes. 22 Specification Update Implication: The Performance Monitoring UNC_GQ_ALLOC.RT_LLC_MISS event may be uncached. AAU16. The local xAPIC's address space must be incorrect. Intel® 64 and IA-32 Architectures Software Developer's Manual Volume 3A: ...