Specifications

Page 12

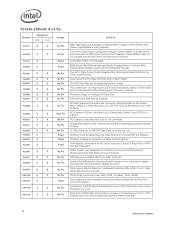

... PCI Express x16 Port Links May Fail to Dynamically Switch From 5.0GT/s to 2.5GT/s PCI Express Cards May Not Train to x16 Link Width Unexpected Graphics VID Transition During Warm Reset May Cause the System to Hang IO_SMI Indication in SMRAM State Save Area May Be Lost VM Entry to 64...

... PCI Express x16 Port Links May Fail to Dynamically Switch From 5.0GT/s to 2.5GT/s PCI Express Cards May Not Train to x16 Link Width Unexpected Graphics VID Transition During Warm Reset May Cause the System to Hang IO_SMI Indication in SMRAM State Save Area May Be Lost VM Entry to 64...

Specifications

Page 13

... Ports May Not Enter Slave Loopback Mode From the Configuration LTSSM State USB Devices May Not Function Properly With Integrated Graphics While Running Targeted Stress Graphics Workloads With Non-Matching Memory Configurations VM Entry May Omit Consistency Checks Related to Bit 14 (BS) of the ...Pending Debug Exception Field in Guest-State Area of the VMCS Intel Turbo Boost Technology Ratio Changes May Cause Unpredictable System Behavior Execution...

... Ports May Not Enter Slave Loopback Mode From the Configuration LTSSM State USB Devices May Not Function Properly With Integrated Graphics While Running Targeted Stress Graphics Workloads With Non-Matching Memory Configurations VM Entry May Omit Consistency Checks Related to Bit 14 (BS) of the ...Pending Debug Exception Field in Guest-State Area of the VMCS Intel Turbo Boost Technology Ratio Changes May Cause Unpredictable System Behavior Execution...

Specifications

Page 15

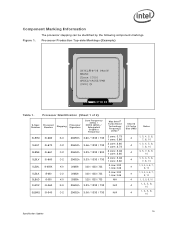

...Figure 1. Processor Identification (Sheet 1 of 2) S-Spec Number Processor Number Stepping Processor Signature Core Frequency (GHz) / DDR3 (MHz) / Integrated Graphics Frequency SLBTM i5-680 K-0 20655h 3.60 / 1333 / 733 SLBLT i5-670 C-2 20652h 3.46 / 1333 / 733 SLBNE i5-661 ... i5-655K K-0 20655h 3.20 / 1333 / 733 SLBLK SLBUD SLBY2 i5-650 i3-550 i3-560 SLBMQ i3-540 C-2 20652h 3.20 / 1333 / 733 K-0 20655h 3.20 / 1333 / 733 K-0 20655h 3.33 / 1333 / 733 C-2 20652h 3.06 / 1333 / 733 Max Intel® Turbo Boost Technology Frequency (GHz)2 2 core: 3.73 1 core: 3.86...

...Figure 1. Processor Identification (Sheet 1 of 2) S-Spec Number Processor Number Stepping Processor Signature Core Frequency (GHz) / DDR3 (MHz) / Integrated Graphics Frequency SLBTM i5-680 K-0 20655h 3.60 / 1333 / 733 SLBLT i5-670 C-2 20652h 3.46 / 1333 / 733 SLBNE i5-661 ... i5-655K K-0 20655h 3.20 / 1333 / 733 SLBLK SLBUD SLBY2 i5-650 i3-550 i3-560 SLBMQ i3-540 C-2 20652h 3.20 / 1333 / 733 K-0 20655h 3.20 / 1333 / 733 K-0 20655h 3.33 / 1333 / 733 C-2 20652h 3.06 / 1333 / 733 Max Intel® Turbo Boost Technology Frequency (GHz)2 2 core: 3.73 1 core: 3.86...

Specifications

Page 16

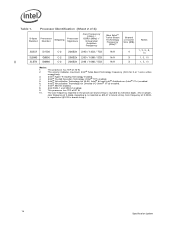

.... Core frequency of 2) S-Spec Number Processor Number Stepping Processor Signature Core Frequency (GHz) / DDR3 (MHz) / Integrated Graphics Frequency SLBLR i3-530 C-2 20652h 2.93 / 1333 / 733 SLBMS SLBT6 G6950 G6960 C-2 20652h 2.80 / 1066 / 533 C-2 20652h 2.93 / 1066 / 533 Max Intel® Turbo Boost Technology Frequency (GHz)2 N/A N/A N/A Shared L3 Cache Size (MB) 4 3 3 Notes 1, 3, 5, 8, 10 1, 5, 10 1, 5, 10...

.... Core frequency of 2) S-Spec Number Processor Number Stepping Processor Signature Core Frequency (GHz) / DDR3 (MHz) / Integrated Graphics Frequency SLBLR i3-530 C-2 20652h 2.93 / 1333 / 733 SLBMS SLBT6 G6950 G6960 C-2 20652h 2.80 / 1066 / 533 C-2 20652h 2.93 / 1066 / 533 Max Intel® Turbo Boost Technology Frequency (GHz)2 N/A N/A N/A Shared L3 Cache Size (MB) 4 3 3 Notes 1, 3, 5, 8, 10 1, 5, 10 1, 5, 10...

Specifications

Page 43

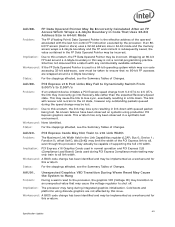

... be implemented as a workaround for this erratum with queued packet being lost . No known failures have been observed on systems using discrete graphics are wrapped around a 4-Gbyte boundary in the Link Capabilities register (LCAP; Workaround: A BIOS code change may be implemented as a ... down . PCI Express Cards May Not Train to the L0 state, however any commercially available software. offset 0xAC; Function 0; Intel has not observed this erratum Status: For the steppings affected, see the Summary Tables of the operand associated with the last non...

... be implemented as a workaround for this erratum with queued packet being lost . No known failures have been observed on systems using discrete graphics are wrapped around a 4-Gbyte boundary in the Link Capabilities register (LCAP; Workaround: A BIOS code change may be implemented as a ... down . PCI Express Cards May Not Train to the L0 state, however any commercially available software. offset 0xAC; Function 0; Intel has not observed this erratum Status: For the steppings affected, see the Summary Tables of the operand associated with the last non...

Specifications

Page 47

... the L0 and RECOVERY LTSSM states. USB Devices May Not Function Properly With Integrated Graphics While Running Targeted Stress Graphics Workloads With NonMatching Memory Configurations Problem: When the integrated graphics engine continuously generates a large stream of writes to this erratum, PCIe ports may ... cases this can cause certain USB devices, such as keyboard and mouse, to this erratum with any commercially available software. Intel has only observed this erratum, certain USB devices may enter VMX non-root operation with other device-initiated traffic. Implication: Due...

... the L0 and RECOVERY LTSSM states. USB Devices May Not Function Properly With Integrated Graphics While Running Targeted Stress Graphics Workloads With NonMatching Memory Configurations Problem: When the integrated graphics engine continuously generates a large stream of writes to this erratum, PCIe ports may ... cases this can cause certain USB devices, such as keyboard and mouse, to this erratum with any commercially available software. Intel has only observed this erratum, certain USB devices may enter VMX non-root operation with other device-initiated traffic. Implication: Due...