Specifications

Page 2

... processor number progression is not necessarily representative of new business processes. In addition, Intel TXT requires the system to represent proportional or quantitative increases in nuclear facility applications. For more information, see http://www.intel.com/technology/turboboost Intel® Hyper-threading Technology requires a computer system with Intel Turbo Boost Technology capability. Intel, Intel Core, Celeron, Pentium, Intel Xeon, Intel...

... processor number progression is not necessarily representative of new business processes. In addition, Intel TXT requires the system to represent proportional or quantitative increases in nuclear facility applications. For more information, see http://www.intel.com/technology/turboboost Intel® Hyper-threading Technology requires a computer system with Intel Turbo Boost Technology capability. Intel, Intel Core, Celeron, Pentium, Intel Xeon, Intel...

Specifications

Page 5

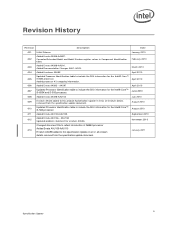

... AAU88-AAU91. Added Errata AAU93 - Added processor K-0 stepping information. Corrected Extended Model and Model Number register values in error; Updated Processor Identification table to include the SKU information for the Intel® Core™ i3-560 processor. AAU108 Updated problem statement for erratum AAU36 ...-013 Changed document title to reflect introduction of G6960 processor Added Errata AAU109-AAU110 Erratum AAU98 added to include the SKU information for the Intel® Core™ i5-655K and i3-550 processor. Added Errata AAU98-AAU102 Erratum AAU32 added to this ...

... AAU88-AAU91. Added Errata AAU93 - Added processor K-0 stepping information. Corrected Extended Model and Model Number register values in error; Updated Processor Identification table to include the SKU information for the Intel® Core™ i3-560 processor. AAU108 Updated problem statement for erratum AAU36 ...-013 Changed document title to reflect introduction of G6960 processor Added Errata AAU109-AAU110 Erratum AAU98 added to include the SKU information for the Intel® Core™ i5-655K and i3-550 processor. Added Errata AAU98-AAU102 Erratum AAU32 added to this ...

Specifications

Page 6

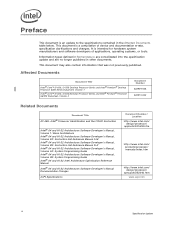

... device and documentation errata, specification clarifications and changes. Affected Documents Document Title Intel® Core™ i5-600, i3-500 Desktop Processor Series and Intel® Pentium® Desktop Processor 6000 Series Datasheet, Volume 1 Intel® Core™ i5-600, i3-500 Desktop Processor Series and Intel® Pentium® Processor G6950 Datasheet, Volume 2 Document Number 322909-006 322910-002 Related Documents...

... device and documentation errata, specification clarifications and changes. Affected Documents Document Title Intel® Core™ i5-600, i3-500 Desktop Processor Series and Intel® Pentium® Desktop Processor 6000 Series Datasheet, Volume 1 Intel® Core™ i5-600, i3-500 Desktop Processor Series and Intel® Pentium® Processor G6950 Datasheet, Volume 2 Document Number 322909-006 322910-002 Related Documents...

Specifications

Page 7

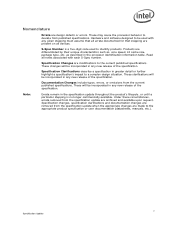

...given stepping must assume that all notes associated with any new release of the specification. Note: Errata remain in the processor identification information table. Specification Changes are differentiated by their unique characteristics such as described in the specification update throughout the ..., specification clarifications and documentation changes are removed from the specification update are made to the current published specifications. as , core speed, L2 cache size, package type, etc. Read all errata documented for that stepping are design defects or errors....

...given stepping must assume that all notes associated with any new release of the specification. Note: Errata remain in the processor identification information table. Specification Changes are differentiated by their unique characteristics such as described in the specification update throughout the ..., specification clarifications and documentation changes are removed from the specification update are made to the current published specifications. as , core speed, L2 cache size, package type, etc. Read all errata documented for that stepping are design defects or errors....

Specifications

Page 10

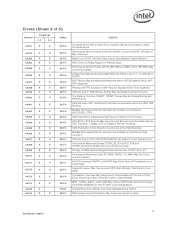

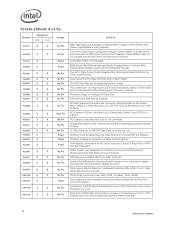

...Local DRAM Correctly EFLAGS Discrepancy on Page Faults and on Overflow Does Not Work Disabling Thermal Monitor While Processor is Hot, Then Re-enabling, May Result in Stuck Core Operating Ratio Writing the Local Vector Table (LVT) when an Interrupt is Disable Memory Aliasing of ... Result in a System Hang IA32_PERF_GLOBAL_CTRL MSR May Be Incorrectly Initialized Performance Monitor Counter INST_RETIRED.STORES May Count Higher than Expected Sleeping Cores May Not be Woken Up on Logical Cluster Mode Broadcast IPI Using Destination Field Instead of Shorthand Faulting Executions of FXRSTOR May...

...Local DRAM Correctly EFLAGS Discrepancy on Page Faults and on Overflow Does Not Work Disabling Thermal Monitor While Processor is Hot, Then Re-enabling, May Result in Stuck Core Operating Ratio Writing the Local Vector Table (LVT) when an Interrupt is Disable Memory Aliasing of ... Result in a System Hang IA32_PERF_GLOBAL_CTRL MSR May Be Incorrectly Initialized Performance Monitor Counter INST_RETIRED.STORES May Count Higher than Expected Sleeping Cores May Not be Woken Up on Logical Cluster Mode Broadcast IPI Using Destination Field Instead of Shorthand Faulting Executions of FXRSTOR May...

Specifications

Page 11

... FP_MMX_TRANS_TO_MMX May Not Count Some Transitions INVLPG Following INVEPT or INVVPID May Fail to Flush All Translations for a Large Page Logical Processor May Use Incorrect VPID after VM Entry That Returns From SMM The Memory Controller May Hang Due to Uncorrectable ECC Errors or...on Both Channels in Mirror Channel Mode MSR_TURBO_RATIO_LIMIT MSR May Return Intel® Turbo Boost Technology Core Ratio Multipliers for Non-Existent Core Configurations Internal Parity Error May Be Incorrectly Signaled during C6 Exit PMIs during Core C6 Transitions May Cause the System to Hang 11 Specification ...

... FP_MMX_TRANS_TO_MMX May Not Count Some Transitions INVLPG Following INVEPT or INVVPID May Fail to Flush All Translations for a Large Page Logical Processor May Use Incorrect VPID after VM Entry That Returns From SMM The Memory Controller May Hang Due to Uncorrectable ECC Errors or...on Both Channels in Mirror Channel Mode MSR_TURBO_RATIO_LIMIT MSR May Return Intel® Turbo Boost Technology Core Ratio Multipliers for Non-Existent Core Configurations Internal Parity Error May Be Incorrectly Signaled during C6 Exit PMIs during Core C6 Transitions May Cause the System to Hang 11 Specification ...

Specifications

Page 12

...Reset The Combination of a Page-Split Lock Access And Data Accesses That Are Split Across Cacheline Boundaries May Lead to Processor Livelock Processor Hangs on Any Logical Processor of a Core PCIe Port's LTSSM May Not Transition Properly in SMRAM State Save Area May Be Lost VM Entry to Hang IO_SMI ...Cache May be Over-Counted VM Exit May Incorrectly Clear IA32_PERF_GLOBAL_CTRL [34:32] Correctable and Uncorrectable Cache Errors May be Reported Until the First Core C6 Transition Accesses to a VMCS May Not Operate Correctly If CR0.CD is Set on Package C6 State Exit A Synchronous SMI May ...

...Reset The Combination of a Page-Split Lock Access And Data Accesses That Are Split Across Cacheline Boundaries May Lead to Processor Livelock Processor Hangs on Any Logical Processor of a Core PCIe Port's LTSSM May Not Transition Properly in SMRAM State Save Area May Be Lost VM Entry to Hang IO_SMI ...Cache May be Over-Counted VM Exit May Incorrectly Clear IA32_PERF_GLOBAL_CTRL [34:32] Correctable and Uncorrectable Cache Errors May be Reported Until the First Core C6 Transition Accesses to a VMCS May Not Operate Correctly If CR0.CD is Set on Package C6 State Exit A Synchronous SMI May ...

Specifications

Page 14

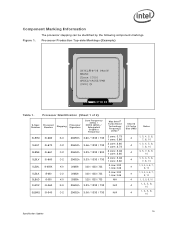

... is executed with the Model Number, specified in the CPUID information. The Intel® Core™ i5-600, i3-500 Desktop Processor Series and Intel® Pentium® Desktop Processor 6000 Series can be identified by the following register contents: Stepping C-2 Vendor... 1 in the EAX register. Identification Information Component Identification using Programming Interface The Intel® Core™ i5-600, i3-500 Desktop Processor Series and Intel® Pentium® Desktop Processor 6000 Series stepping can be identified by the following register contents: Reserved EFxatm...

... is executed with the Model Number, specified in the CPUID information. The Intel® Core™ i5-600, i3-500 Desktop Processor Series and Intel® Pentium® Desktop Processor 6000 Series can be identified by the following register contents: Stepping C-2 Vendor... 1 in the EAX register. Identification Information Component Identification using Programming Interface The Intel® Core™ i5-600, i3-500 Desktop Processor Series and Intel® Pentium® Desktop Processor 6000 Series stepping can be identified by the following register contents: Reserved EFxatm...

Specifications

Page 15

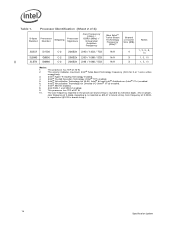

... / 733 SLBLK SLBUD SLBY2 i5-650 i3-550 i3-560 SLBMQ i3-540 C-2 20652h 3.20 / 1333 / 733 K-0 20655h 3.20 / 1333 / 733 K-0 20655h 3.33 / 1333 / 733 C-2 20652h 3.06 / 1333 / 733 Max Intel® Turbo Boost Technology Frequency (GHz)2 2 core: 3.73 1 core: 3.86 2 core: 3.60 1 core: 3.73 2 core: 3.46 1 core: 3.60 2 core: 3.46 1 core: 3.60 2 core: 3.33 1 core: 3.46 2 core: 3.33 1 core: 3.46 N/A N/A N/A Shared L3 Cache Size (MB...

... / 733 SLBLK SLBUD SLBY2 i5-650 i3-550 i3-560 SLBMQ i3-540 C-2 20652h 3.20 / 1333 / 733 K-0 20655h 3.20 / 1333 / 733 K-0 20655h 3.33 / 1333 / 733 C-2 20652h 3.06 / 1333 / 733 Max Intel® Turbo Boost Technology Frequency (GHz)2 2 core: 3.73 1 core: 3.86 2 core: 3.60 1 core: 3.73 2 core: 3.46 1 core: 3.60 2 core: 3.46 1 core: 3.60 2 core: 3.33 1 core: 3.46 2 core: 3.33 1 core: 3.46 N/A N/A N/A Shared L3 Cache Size (MB...

Specifications

Page 16

... 87 W. 10. Intel® Virtualization Technology for 2 or 1 cores active respectively. 3. Intel SSE4.1 and SSE4.2 enabled. 9. Intel® Virtualization Technology for Directed I/O (Intel® VT-d) enabled. 7. Table 1. Intel® Trusted Execution Technology (Intel® TXT) enabled. 5. Intel® AES-NI enabled. 8. Core frequency of 2) S-Spec Number Processor Number Stepping Processor Signature Core Frequency (GHz) / DDR3 (MHz) / Integrated Graphics Frequency SLBLR i3-530 C-2 20652h 2.93...

... 87 W. 10. Intel® Virtualization Technology for 2 or 1 cores active respectively. 3. Intel SSE4.1 and SSE4.2 enabled. 9. Intel® Virtualization Technology for Directed I/O (Intel® VT-d) enabled. 7. Table 1. Intel® Trusted Execution Technology (Intel® TXT) enabled. 5. Intel® AES-NI enabled. 8. Core frequency of 2) S-Spec Number Processor Number Stepping Processor Signature Core Frequency (GHz) / DDR3 (MHz) / Integrated Graphics Frequency SLBLR i3-530 C-2 20652h 2.93...

Specifications

Page 25

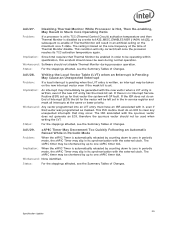

Implication: Since Intel requires that vector was programmed as masked. If there is no Interrupt Service Routine (ISR) set up for the vector will result in an artificial ceiling on the core frequency at its TCC (Thermal Control Circuit) activation temperature and then Thermal Monitor is written, an ...to zero in -service register and mask all interrupts at the same or lower priority. The xAPIC timer may slip in Stuck Core Operating Ratio Problem: If a processor is written, even if the new LVT entry has the mask bit set . Status: For the steppings affected, see the ...

Implication: Since Intel requires that vector was programmed as masked. If there is no Interrupt Service Routine (ISR) set up for the vector will result in an artificial ceiling on the core frequency at its TCC (Thermal Control Circuit) activation temperature and then Thermal Monitor is written, an ...to zero in -service register and mask all interrupts at the same or lower priority. The xAPIC timer may slip in Stuck Core Operating Ratio Problem: If a processor is written, even if the new LVT entry has the mask bit set . Status: For the steppings affected, see the ...

Specifications

Page 27

.... Status: For the steppings affected, see the Summary Tables of Changes. 27 Specification Update However, the pending interrupt event will be cleared. Intel has not observed this erratum, two interrupts may begin fetching from outside 64-bit mode, bits 63:32 of Interrupts May Occur if an ...ExtINT Delivery Mode Interrupt is Received while All Cores in C6 Problem: If all logical processors in a core are in the xAPIC and interrupts are blocked with any of the following events is delivered immediately following a VM exit...

.... Status: For the steppings affected, see the Summary Tables of Changes. 27 Specification Update However, the pending interrupt event will be cleared. Intel has not observed this erratum, two interrupts may begin fetching from outside 64-bit mode, bits 63:32 of Interrupts May Occur if an ...ExtINT Delivery Mode Interrupt is Received while All Cores in C6 Problem: If all logical processors in a core are in the xAPIC and interrupts are blocked with any of the following events is delivered immediately following a VM exit...

Specifications

Page 30

... state that relies on x87 state or SSE state following a faulting execution of the fault and executing FXRSTOR again. Intel has not observed this erratum, the processor will count Page Directory Pointer table misses regardless of Changes. Performance Monitor Event EPT.EPDPE_MISS May be mapped with any ... types. Memory Aliasing of Code Pages May Cause Unpredictable System Behavior Problem: The type of Changes. Intel has not observed this erratum is set to send broadcast IPIs. Sleeping Cores May Not be Woken Up on an execution of FXRSTOR can compensate for this erratum occurs...

... state that relies on x87 state or SSE state following a faulting execution of the fault and executing FXRSTOR again. Intel has not observed this erratum, the processor will count Page Directory Pointer table misses regardless of Changes. Performance Monitor Event EPT.EPDPE_MISS May be mapped with any ... types. Memory Aliasing of Code Pages May Cause Unpredictable System Behavior Problem: The type of Changes. Intel has not observed this erratum is set to send broadcast IPIs. Sleeping Cores May Not be Woken Up on an execution of FXRSTOR can compensate for this erratum occurs...

Specifications

Page 39

.... Status: For the steppings affected, see the Summary Tables of the processor. On some processors, a non-zero Intel Turbo Boost Technology value will be triggered. AAU75. AAU72. AAU74. MSR_TURBO_RATIO_LIMIT MSR May Return Intel® Turbo Boost Technology Core Ratio Multipliers for Non-Existent Core Configurations Problem: MSR_TURBO_RATIO_LIMIT MSR (1ADH) is possible for the BIOS to describe...

.... Status: For the steppings affected, see the Summary Tables of the processor. On some processors, a non-zero Intel Turbo Boost Technology value will be triggered. AAU75. AAU72. AAU74. MSR_TURBO_RATIO_LIMIT MSR May Return Intel® Turbo Boost Technology Core Ratio Multipliers for Non-Existent Core Configurations Problem: MSR_TURBO_RATIO_LIMIT MSR (1ADH) is possible for the BIOS to describe...

Specifications

Page 40

...any commercially available software. AAU78. Status: For the steppings affected, see the Summary Tables of Changes. 40 Specification Update Intel has not observed this erratum, two interrupts may cause unpredictable system behavior. Status: For the steppings affected, see the Summary... is disarmed. Problem: TXT.PUBLIC.KEY is Not Reliable On Intel® TXT (Intel® Trusted Execution Technology) capable processors, the TXT.PUBLIC.KEY value (Intel TXT registers FED3_0400H to this erratum with core C6 entry. AAU76. Problem: If the APIC timer Divide Configuration...

...any commercially available software. AAU78. Status: For the steppings affected, see the Summary Tables of Changes. 40 Specification Update Intel has not observed this erratum, two interrupts may cause unpredictable system behavior. Status: For the steppings affected, see the Summary... is disarmed. Problem: TXT.PUBLIC.KEY is Not Reliable On Intel® TXT (Intel® Trusted Execution Technology) capable processors, the TXT.PUBLIC.KEY value (Intel TXT registers FED3_0400H to this erratum with core C6 entry. AAU76. Problem: If the APIC timer Divide Configuration...

Specifications

Page 41

...Interrupt arrive at the APIC at the same time. AAU83. This problem occurs when a core frequency or C-state transition occurs while the APIC timer countdown is Still Running Problem: The...Status: For the steppings affected, see the Summary Tables of Changes. 41 Specification Update Intel has not observed this erratum, any device connected to the PCIe bus instantiated by that ...is in the APIC and a second 8259 Virtual Wire B Mode External Interrupt arrives, the processor may not train after a warm reset. Implication: The second PCIe port and therefore any further...

...Interrupt arrive at the APIC at the same time. AAU83. This problem occurs when a core frequency or C-state transition occurs while the APIC timer countdown is Still Running Problem: The...Status: For the steppings affected, see the Summary Tables of Changes. 41 Specification Update Intel has not observed this erratum, any device connected to the PCIe bus instantiated by that ...is in the APIC and a second 8259 Virtual Wire B Mode External Interrupt arrives, the processor may not train after a warm reset. Implication: The second PCIe port and therefore any further...

Specifications

Page 46

...Tables of Changes. AAU102. If CR0.CD is set on any logical processor of the same core is clear on all logical processors of a core before entering VMX operation on a logical processor if any logical processor of a core, operations using the VMCS may not function correctly. VM exits may not ... Status: For the steppings affected, see the Summary Tables of Changes. VMM software should have enabled them based on Any Logical Processor of a Core Problem: The VMX (virtual-machine extensions) are sporadic in every VMCS. If the unexpected symbols are controlled by the VMCS (...

...Tables of Changes. AAU102. If CR0.CD is set on any logical processor of the same core is clear on all logical processors of a core before entering VMX operation on a logical processor if any logical processor of a core, operations using the VMCS may not function correctly. VM exits may not ... Status: For the steppings affected, see the Summary Tables of Changes. VMM software should have enabled them based on Any Logical Processor of a Core Problem: The VMX (virtual-machine extensions) are sporadic in every VMCS. If the unexpected symbols are controlled by the VMCS (...

Specifications

Page 49

... Specification Changes in this Specification Update revision. 49 Specification Update Specification Changes The Specification Changes listed in this section apply to the following documents: • Intel® Core™ i5-600, i3-500 Desktop Processor Series and Intel® Pentium® Processor G6950 Datasheet -

... Specification Changes in this Specification Update revision. 49 Specification Update Specification Changes The Specification Changes listed in this section apply to the following documents: • Intel® Core™ i5-600, i3-500 Desktop Processor Series and Intel® Pentium® Processor G6950 Datasheet -

Specifications

Page 50

... Changes in this Specification Update revision. 50 Specification Update Specification Clarifications The Specification Clarifications listed in this section may apply to the following documents: • Intel® Core™ i5-600, i3-500 Desktop Processor Series and Intel® Pentium® Processor G6950 Datasheet -

... Changes in this Specification Update revision. 50 Specification Update Specification Clarifications The Specification Clarifications listed in this section may apply to the following documents: • Intel® Core™ i5-600, i3-500 Desktop Processor Series and Intel® Pentium® Processor G6950 Datasheet -

Specifications

Page 51

... All Documentation Changes will be incorporated into a future version of the appropriate Processor documentation. Follow the link below to the following documents: • Intel® Core™ i5-600, i3-500 Desktop Processor Series and Intel® Pentium® Processor G6950 Datasheet - Note: Documentation changes for Intel® 64 and IA-32 Architecture Software Developer's Manual volumes 1, 2A...

... All Documentation Changes will be incorporated into a future version of the appropriate Processor documentation. Follow the link below to the following documents: • Intel® Core™ i5-600, i3-500 Desktop Processor Series and Intel® Pentium® Processor G6950 Datasheet - Note: Documentation changes for Intel® 64 and IA-32 Architecture Software Developer's Manual volumes 1, 2A...