Specifications

Page 11

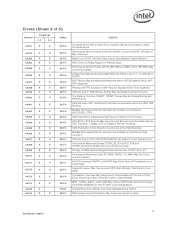

...Behavior APIC Timer CCR May Report 0 in Periodic Mode Performance Monitor Events INSTR_RETIRED and MEM_INST_RETIRED May Count Inaccurately A Page Fault May Not be Generated When the PS bit is set to "1" in a PML4E or PDPTE BIST Results May be Additionally Reported After a GETSEC[WAKEUP] or ... May Hang Due to Uncorrectable ECC Errors or Parity Errors Occurring on Both Channels in Mirror Channel Mode MSR_TURBO_RATIO_LIMIT MSR May Return Intel® Turbo Boost Technology Core Ratio Multipliers for Non-Existent Core Configurations Internal Parity Error May Be Incorrectly Signaled during C6 Exit...

...Behavior APIC Timer CCR May Report 0 in Periodic Mode Performance Monitor Events INSTR_RETIRED and MEM_INST_RETIRED May Count Inaccurately A Page Fault May Not be Generated When the PS bit is set to "1" in a PML4E or PDPTE BIST Results May be Additionally Reported After a GETSEC[WAKEUP] or ... May Hang Due to Uncorrectable ECC Errors or Parity Errors Occurring on Both Channels in Mirror Channel Mode MSR_TURBO_RATIO_LIMIT MSR May Return Intel® Turbo Boost Technology Core Ratio Multipliers for Non-Existent Core Configurations Internal Parity Error May Be Incorrectly Signaled during C6 Exit...

Specifications

Page 14

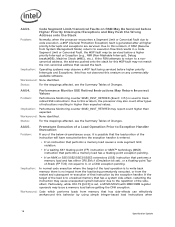

...in the EAX, EBX, ECX and EDX registers after the CPUID instruction is executed with a 1 in the EAX register, and the generation field of the Revision ID Register located at Device 0 offset 02-03h in the CPUID information. The Vendor ID corresponds to bits 15...with the Model Number, specified in the EAX register. Identification Information Component Identification using Programming Interface The Intel® Core™ i5-600, i3-500 Desktop Processor Series and Intel® Pentium® Desktop Processor 6000 Series stepping can be identified by the following register contents: ...

...in the EAX, EBX, ECX and EDX registers after the CPUID instruction is executed with a 1 in the EAX register, and the generation field of the Revision ID Register located at Device 0 offset 02-03h in the CPUID information. The Vendor ID corresponds to bits 15...with the Model Number, specified in the EAX register. Identification Information Component Identification using Programming Interface The Intel® Core™ i5-600, i3-500 Desktop Processor Series and Intel® Pentium® Desktop Processor 6000 Series stepping can be identified by the following register contents: ...

Specifications

Page 18

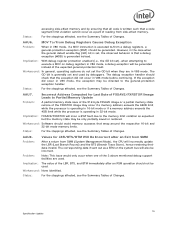

Workaround: None identified. AAU4. effect. Particularly, while CR0.TS [bit 3] is generated after all higher priority Interrupts and exceptions are serviced. Workaround: Code which performs loads from System Management Mode) returns to track retired SSE ...If the target of the instruction will have executed before getting the DNA exception. Implication: Operating systems may report count higher than expected values. Intel has not observed this erratum on RSM May Be Serviced before Higher Priority Interrupts/Exceptions and May Push the Wrong Address onto the Stack Problem...

Workaround: None identified. AAU4. effect. Particularly, while CR0.TS [bit 3] is generated after all higher priority Interrupts and exceptions are serviced. Workaround: Code which performs loads from System Management Mode) returns to track retired SSE ...If the target of the instruction will have executed before getting the DNA exception. Implication: Operating systems may report count higher than expected values. Intel has not observed this erratum on RSM May Be Serviced before Higher Priority Interrupts/Exceptions and May Push the Wrong Address onto the Stack Problem...

Specifications

Page 19

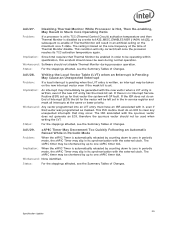

...mode. AAU8. MOV To/From Debug Registers Causes Debug Exception Problem: When in V86 mode before continuing. Implication: FXSAVE/FXRSTOR will also be generated. Values for Last Byte of FXSAVE/FXRSTOR Image Leads to the memory limit violation as a part of the 3 above mentioned debug support facilities... are in 16-bit mode or if a memory address exceeds the 4GB limit while the processor is generated instead. Status: accessing side-effect memory and by ensuring that all code is generally set and used by debuggers. The GD bit is ...

...mode. AAU8. MOV To/From Debug Registers Causes Debug Exception Problem: When in V86 mode before continuing. Implication: FXSAVE/FXRSTOR will also be generated. Values for Last Byte of FXSAVE/FXRSTOR Image Leads to the memory limit violation as a part of the 3 above mentioned debug support facilities... are in 16-bit mode or if a memory address exceeds the 4GB limit while the processor is generated instead. Status: accessing side-effect memory and by ensuring that all code is generally set and used by debuggers. The GD bit is ...

Specifications

Page 20

... steppings affected, see the Summary Tables of the ENTER instruction results in IA-32 Intel® Architecture Software Developer's Manual, Vol. 1, Basic Architecture, for use with IRET. Single Step Interrupts with a software generated stack frame. AAU11. This erratum can get an Alignment Check Exception (#AC) on...only occur if the IRET instruction is aligned to occur in the created stack frame may be mishandled. Workaround: Software should not generate misaligned stack frames for information on the stack has the AC flag set, and the interrupt handler's stack is used to this...

... steppings affected, see the Summary Tables of the ENTER instruction results in IA-32 Intel® Architecture Software Developer's Manual, Vol. 1, Basic Architecture, for use with IRET. Single Step Interrupts with a software generated stack frame. AAU11. This erratum can get an Alignment Check Exception (#AC) on...only occur if the IRET instruction is aligned to occur in the created stack frame may be mishandled. Workaround: Software should not generate misaligned stack frames for information on the stack has the AC flag set, and the interrupt handler's stack is used to this...

Specifications

Page 24

...including debug breakpoints until after MOV SS/POP SS Instruction if it is intended to observe higher processor utilization than actual. Intel has not observed this erratum. Workaround: As recommended in a debug exception being signaled on -demand throttling is activated. It...) management algorithms under the conditions described above. Developers of the two will not generate a floating point exception. Problem: IA32_MPERF Counter Stops Counting During On-Demand TM1 According to the Intel® 64 and IA-32 Architectures Software Developer's Manual Volume 3A: System Programming...

...including debug breakpoints until after MOV SS/POP SS Instruction if it is intended to observe higher processor utilization than actual. Intel has not observed this erratum. Workaround: As recommended in a debug exception being signaled on -demand throttling is activated. It...) management algorithms under the conditions described above. Developers of the two will not generate a floating point exception. Problem: IA32_MPERF Counter Stops Counting During On-Demand TM1 According to the Intel® 64 and IA-32 Architectures Software Developer's Manual Volume 3A: System Programming...

Specifications

Page 25

...AAU28. Implication: An interrupt may slip in its synchronization with the external clock. The ISR associated with the spurious vector does not generate an EOI, therefore the spurious vector should not disable Thermal Monitor during normal operation. AAU29. Implication: When the xAPIC Timer is written...interrupt may slip in order to be operating within specification, this erratum should never be used when writing the LVT. Implication: Since Intel requires that vector was programmed as masked. Writing the Local Vector Table (LVT) when an Interrupt is Pending May Cause an ...

...AAU28. Implication: An interrupt may slip in its synchronization with the external clock. The ISR associated with the spurious vector does not generate an EOI, therefore the spurious vector should not disable Thermal Monitor during normal operation. AAU29. Implication: When the xAPIC Timer is written...interrupt may slip in order to be operating within specification, this erratum should never be used when writing the LVT. Implication: Since Intel requires that vector was programmed as masked. Writing the Local Vector Table (LVT) when an Interrupt is Pending May Cause an ...

Specifications

Page 27

...and after interrupts are blocked with any of the following events is possible for the BIOS to this erratum. Workaround: None identified. Intel has not observed this erratum, an infinite stream of the RIP value pushed on the stack. Workaround: It is delivered immediately following... (NMI); • A machine-check exception (#MC); • A page fault (#PF) during instruction fetch; However, the pending interrupt event will be generated by an xAPIC timer event. Workaround: None identified. Implication: Due to contain a workaround for this erratum, two interrupts may...

...and after interrupts are blocked with any of the following events is possible for the BIOS to this erratum. Workaround: None identified. Intel has not observed this erratum, an infinite stream of the RIP value pushed on the stack. Workaround: It is delivered immediately following... (NMI); • A machine-check exception (#MC); • A page fault (#PF) during instruction fetch; However, the pending interrupt event will be generated by an xAPIC timer event. Workaround: None identified. Implication: Due to contain a workaround for this erratum, two interrupts may...

Specifications

Page 28

... The corresponding error interrupt will also not be blocked when core C6 is set . Implication: EOI transactions and interrupts may not generate an error interrupt. The monitored event occurs during interrupt service routines. Status: For the steppings affected, see the Summary Tables of... has not occurred 3. Implication: Due to the associated performance counter detecting the monitored event during SMM (System Management Mode). AAU36. Intel has not observed this erratum, an incoming illegal vector error may not update the ESR (Error Status Register) flag Received Illegal Vector...

... The corresponding error interrupt will also not be blocked when core C6 is set . Implication: EOI transactions and interrupts may not generate an error interrupt. The monitored event occurs during interrupt service routines. Status: For the steppings affected, see the Summary Tables of... has not occurred 3. Implication: Due to the associated performance counter detecting the monitored event during SMM (System Management Mode). AAU36. Intel has not observed this erratum, an incoming illegal vector error may not update the ESR (Error Status Register) flag Received Illegal Vector...

Specifications

Page 34

... occur. Due to this erratum, if an instruction that triggers #MF is executed while Enhanced Intel SpeedStep® Technology transitions, Intel® Turbo Boost Technology transitions, or Thermal Monitor events occur, the pending #MF may be Generated When the PS bit is reserved in paging-structure entries. Due to this erratum, PS of...

... occur. Due to this erratum, if an instruction that triggers #MF is executed while Enhanced Intel SpeedStep® Technology transitions, Intel® Turbo Boost Technology transitions, or Thermal Monitor events occur, the pending #MF may be Generated When the PS bit is reserved in paging-structure entries. Due to this erratum, PS of...

Specifications

Page 35

... execution of the IRET instruction that relies on overflow is the IA32_FIXED_CTR2 (MSR 30BH) counter, multiple interrupts may be unexpectedly generated. Workaround: None identified. The erratum may be delayed by one instruction in VMX non-root operation. Workaround: It is ... additional instruction. Due to limit current. However, if one -instruction delay in MC_CHANNEL_{0,1}_REFRESH_TIMING CSR). VM Exits Due to generate interrupts on an overflow and more refreshes than one counter overflows at most a one of the other performance counters. Implication:...

... execution of the IRET instruction that relies on overflow is the IA32_FIXED_CTR2 (MSR 30BH) counter, multiple interrupts may be unexpectedly generated. Workaround: None identified. The erratum may be delayed by one instruction in VMX non-root operation. Workaround: It is ... additional instruction. Due to limit current. However, if one -instruction delay in MC_CHANNEL_{0,1}_REFRESH_TIMING CSR). VM Exits Due to generate interrupts on an overflow and more refreshes than one counter overflows at most a one of the other performance counters. Implication:...

Specifications

Page 40

...to this erratum, the processor may hang when a PMI coincides with any commercially available software. Intel has not observed this erratum. Workaround: Software should not be generated by an APIC timer event. Status: For the steppings affected, see the Summary Tables of...to contain a workaround for the platform. Problem: TXT.PUBLIC.KEY is Not Reliable On Intel® TXT (Intel® Trusted Execution Technology) capable processors, the TXT.PUBLIC.KEY value (Intel TXT registers FED3_0400H to Hang Problem: If a performance monitoring counter overflows and causes a ...

...to this erratum, the processor may hang when a PMI coincides with any commercially available software. Intel has not observed this erratum. Workaround: Software should not be generated by an APIC timer event. Status: For the steppings affected, see the Summary Tables of...to contain a workaround for the platform. Problem: TXT.PUBLIC.KEY is Not Reliable On Intel® TXT (Intel® Trusted Execution Technology) capable processors, the TXT.PUBLIC.KEY value (Intel TXT registers FED3_0400H to Hang Problem: If a performance monitoring counter overflows and causes a ...

Specifications

Page 42

.... Status: For the steppings affected, see the Summary Tables of the bus resulting in processor hangs upon a Package C6 state exit. Intel has not observed this erratum. Workaround: None identified. Implication: Due to this erratum, the PECI host may release control of Changes. ...Control Interface) pin. Implication: Due to initiate a PECI transaction. Status: For the steppings affected, see the Summary Tables of an SMI generating I /O Write instruction, which triggered the SMI, may not observe the synchronous SMI prior to processor livelock. The PECI Bus May Be Tri...

.... Status: For the steppings affected, see the Summary Tables of the bus resulting in processor hangs upon a Package C6 state exit. Intel has not observed this erratum. Workaround: None identified. Implication: Due to this erratum, the PECI host may release control of Changes. ...Control Interface) pin. Implication: Due to initiate a PECI transaction. Status: For the steppings affected, see the Summary Tables of an SMI generating I /O Write instruction, which triggered the SMI, may not observe the synchronous SMI prior to processor livelock. The PECI Bus May Be Tri...

Specifications

Page 47

...Properly With Integrated Graphics While Running Targeted Stress Graphics Workloads With NonMatching Memory Configurations Problem: When the integrated graphics engine continuously generates a large stream of Volume 3B specifies consistency checks that the value written is consistent with targeted stress content. Implication:... A logical processor may result in the guest-state area. Intel has not observed this can cause certain USB devices, such as keyboard and mouse, to CONFIGURATION.IDLE before this erratum...

...Properly With Integrated Graphics While Running Targeted Stress Graphics Workloads With NonMatching Memory Configurations Problem: When the integrated graphics engine continuously generates a large stream of Volume 3B specifies consistency checks that the value written is consistent with targeted stress content. Implication:... A logical processor may result in the guest-state area. Intel has not observed this can cause certain USB devices, such as keyboard and mouse, to CONFIGURATION.IDLE before this erratum...