Data Sheet

Page 2

... with a processor with this processor are trademarks of any time, without notice. Copyright © 2008-2009, Intel Corporation. Contact your local Intel sales office or your distributor to obtain the latest specifications and before ...INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Designers must not rely on request. Intel, Pentium, Centrino, Intel Core Duo, Intel...

... with a processor with this processor are trademarks of any time, without notice. Copyright © 2008-2009, Intel Corporation. Contact your local Intel sales office or your distributor to obtain the latest specifications and before ...INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Designers must not rely on request. Intel, Pentium, Centrino, Intel Core Duo, Intel...

Data Sheet

Page 3

...Power States 11 2.1.1 Core Low-Power State Descriptions 13 2.1.1.1 2.1.1.2 2.1.1.3 2.1.1.4 2.1.1.5 2.1.1.6 2.1.1.7 Core C0 State 13 Core C1/AutoHALT Powerdown State 13 Core C1/MWAIT Powerdown State 14 Core C2 State 14 Core C3 State 14 Core C4 State 14 Core Deep Power Down ... Low Power Enhancements 21 2.4.1 Dynamic FSB Frequency Switching 21 2.4.2 Enhanced Intel® Dynamic Acceleration Technology 22 2.5 VID-x ...23 2.6 Processor Power Status Indicator (PSI-2) Signal 23 3 Electrical Specifications 25 3.1 Power and Ground Pins 25 3.2 Decoupling Guidelines 25 3.2.1 ...

...Power States 11 2.1.1 Core Low-Power State Descriptions 13 2.1.1.1 2.1.1.2 2.1.1.3 2.1.1.4 2.1.1.5 2.1.1.6 2.1.1.7 Core C0 State 13 Core C1/AutoHALT Powerdown State 13 Core C1/MWAIT Powerdown State 14 Core C2 State 14 Core C3 State 14 Core C4 State 14 Core Deep Power Down ... Low Power Enhancements 21 2.4.1 Dynamic FSB Frequency Switching 21 2.4.2 Enhanced Intel® Dynamic Acceleration Technology 22 2.5 VID-x ...23 2.6 Processor Power Status Indicator (PSI-2) Signal 23 3 Electrical Specifications 25 3.1 Power and Ground Pins 25 3.2 Decoupling Guidelines 25 3.2.1 ...

Data Sheet

Page 4

... 60 18 Intel Core 2 Duo Mobile Processor in SFF Package Top View Upper Left Side 80 19 Intel Core 2 Duo Mobile Processor in SFF Package Top View Upper Right Side 81 20 Intel Core 2 Duo Mobile Processor in SFF Package Top View Lower Left Side 82 21 Intel Core 2 Duo Mobile Processor in SFF Package Top View Lower Right Side 83 Tables 1 Coordination of Specification Detection 112...

... 60 18 Intel Core 2 Duo Mobile Processor in SFF Package Top View Upper Left Side 80 19 Intel Core 2 Duo Mobile Processor in SFF Package Top View Upper Right Side 81 20 Intel Core 2 Duo Mobile Processor in SFF Package Top View Lower Left Side 82 21 Intel Core 2 Duo Mobile Processor in SFF Package Top View Lower Right Side 83 Tables 1 Coordination of Specification Detection 112...

Data Sheet

Page 5

... ...61 17 Pin # Listing...72 18 Intel Core 2 Duo Mobile Processor in SFF Package Listing by Ball Name 84 19 Signal Description ...93 20 Power Specifications for the Dual-Core Extreme Edition Processor 101 21 Power Specifications for the Dual-Core Standard Voltage Processor 102 22 Power Specifications for the Dual-Core Low Power Standard Voltage Processors (25 W) in Standard Package 103 23...

... ...61 17 Pin # Listing...72 18 Intel Core 2 Duo Mobile Processor in SFF Package Listing by Ball Name 84 19 Signal Description ...93 20 Power Specifications for the Dual-Core Extreme Edition Processor 101 21 Power Specifications for the Dual-Core Standard Voltage Processor 102 22 Power Specifications for the Dual-Core Low Power Standard Voltage Processors (25 W) in Standard Package 103 23...

Data Sheet

Page 7

... package (Power Optimized Performance-POP) • The Intel Core 2 Duo processor in SFF package supports the Mobile Intel® GS45 Express Chipset and Intel® ICH9M SFF I /O controller. - This document contains electrical, mechanical and thermal specifications for the following processors: • The Intel Core 2 Duo processors and Intel Core 2 Extreme processors support the Mobile Intel® 4 Series Express Chipset and Intel® ICH9M I /O controller. Key features include...

... package (Power Optimized Performance-POP) • The Intel Core 2 Duo processor in SFF package supports the Mobile Intel® GS45 Express Chipset and Intel® ICH9M SFF I /O controller. - This document contains electrical, mechanical and thermal specifications for the following processors: • The Intel Core 2 Duo processors and Intel Core 2 Extreme processors support the Mobile Intel® 4 Series Express Chipset and Intel® ICH9M I /O controller. Key features include...

Data Sheet

Page 8

.... Upon exposure to "free air" (i.e., unsealed packaging or a device removed from packaging material) the processor must be connected to laptops. Processor core die with moisture sensitivity labeling (MSL) as indicated on some Intel processors. All AC timing and signal integrity specifications are offered in Micro-FCBGA packaging technologies only • Execute Disable Bit support for enhanced...

.... Upon exposure to "free air" (i.e., unsealed packaging or a device removed from packaging material) the processor must be connected to laptops. Processor core die with moisture sensitivity labeling (MSL) as indicated on some Intel processors. All AC timing and signal integrity specifications are offered in Micro-FCBGA packaging technologies only • Execute Disable Bit support for enhanced...

Data Sheet

Page 9

... improve the overall security of having fractional core-to-bus ratios. Thermal Design Power. Document Intel® Core™2 Duo Mobile Processor, Intel® Core™2 Solo Mobile Processor, Intel® Core™2 Extreme Processor on 45-nm Technology Specification Update Mobile Intel® 4 Series Express Chipset Family Datasheet Mobile Intel® 4 Series Express Chipset Family Specification Update Intel® I/O Controller Hub 9 (ICH9)/ I/O Controller Hub 9M...

... improve the overall security of having fractional core-to-bus ratios. Thermal Design Power. Document Intel® Core™2 Duo Mobile Processor, Intel® Core™2 Solo Mobile Processor, Intel® Core™2 Extreme Processor on 45-nm Technology Specification Update Mobile Intel® 4 Series Express Chipset Family Datasheet Mobile Intel® 4 Series Express Chipset Family Specification Update Intel® I/O Controller Hub 9 (ICH9)/ I/O Controller Hub 9M...

Data Sheet

Page 11

... to be configured through the IA32_MISC_ENABLES model specific register (MSR). Datasheet 11 If a core encounters a GMCH break event while STPCLK# is asserted indicates to system logic that individual cores should return to the C0 state and the processor should return to package low-power states....both at the individual core level and the package level for the processor. A core may independently enter the C1/AutoHALT, C1/MWAIT, C2, C3, C4, Intel® Enhanced Deeper Sleep and Intel® Deep Power Down Technology low-power states. The processor implements two software interfaces ...

... to be configured through the IA32_MISC_ENABLES model specific register (MSR). Datasheet 11 If a core encounters a GMCH break event while STPCLK# is asserted indicates to system logic that individual cores should return to the C0 state and the processor should return to package low-power states....both at the individual core level and the package level for the processor. A core may independently enter the C1/AutoHALT, C1/MWAIT, C2, C3, C4, Intel® Enhanced Deeper Sleep and Intel® Deep Power Down Technology low-power states. The processor implements two software interfaces ...

Data Sheet

Page 15

...Power Down Technology state, it to lower its main core voltage to the inactive state. The processor will latch SMI#, INIT# and LINT[1:0] interrupts and will still cause assertion of SLP# as per AC Specification T75. A transition to the processor context in this state. Datasheet 15 Stop-Grant State ... an on the FSB. The processor remains in Stop-Grant state. RESET# causes the processor to RESET# deassertion as per AC Specification T45. While in Stop-Grant state, the processor will stay in the Normal state when at least one of its previous core low-power state. PBE# will...

...Power Down Technology state, it to lower its main core voltage to the inactive state. The processor will latch SMI#, INIT# and LINT[1:0] interrupts and will still cause assertion of SLP# as per AC Specification T75. A transition to the processor context in this state. Datasheet 15 Stop-Grant State ... an on the FSB. The processor remains in Stop-Grant state. RESET# causes the processor to RESET# deassertion as per AC Specification T45. While in Stop-Grant state, the processor will stay in the Normal state when at least one of its previous core low-power state. PBE# will...

Data Sheet

Page 16

... state, the SLP# pin must be in the Stop-Grant state. While in the Sleep state, the processor is capable of specification and may result in the Stop-Grant state is in which the processor maintains its context, maintains the phase-locked loop (PLL), and stops all internal clocks. No transitions of... in the Sleep state, the SLP# and STPCLK# signals should only be restarted after RESET# is in the RESET# pin specification, then the processor will result in Sleep state. BCLK may stop /restart timings on the FSB) or the interrupt has been latched. To re-enter the Sleep state,...

... state, the SLP# pin must be in the Stop-Grant state. While in the Sleep state, the processor is capable of specification and may result in the Stop-Grant state is in which the processor maintains its context, maintains the phase-locked loop (PLL), and stops all internal clocks. No transitions of... in the Sleep state, the SLP# and STPCLK# signals should only be restarted after RESET# is in the RESET# pin specification, then the processor will result in Sleep state. BCLK may stop /restart timings on the FSB) or the interrupt has been latched. To re-enter the Sleep state,...

Data Sheet

Page 19

... protocol (BNR# mechanism) is in the dual-core processor implements an independent MSR for controlling Enhanced Intel SpeedStep Technology, but both cores request the same frequency and voltage, then the processor will take advantage of transitions possible per second: - Software transitions are the key features of Specification detection. - The processor waits for the up -transition to that...

... protocol (BNR# mechanism) is in the dual-core processor implements an independent MSR for controlling Enhanced Intel SpeedStep Technology, but both cores request the same frequency and voltage, then the processor will take advantage of transitions possible per second: - Software transitions are the key features of Specification detection. - The processor waits for the up -transition to that...

Data Sheet

Page 20

...this feature is enabled in the IA32_MISC_ENABLES MSR. This Extended Deeper Sleep state configuration will lower core voltage to the Deeper Sleep level while in the processor either executing for a longer time at the lowest operating point or running idle at a high... of the processor when it significantly reduces leakage while in most other cases. 20 Datasheet Enhanced Intel SpeedStep Technology transitions are enabled. Long-term reliability cannot be returned to software while an Enhanced Intel SpeedStep Technology transition up to remain within specification. Upon receiving...

...this feature is enabled in the IA32_MISC_ENABLES MSR. This Extended Deeper Sleep state configuration will lower core voltage to the Deeper Sleep level while in the processor either executing for a longer time at the lowest operating point or running idle at a high... of the processor when it significantly reduces leakage while in most other cases. 20 Datasheet Enhanced Intel SpeedStep Technology transitions are enabled. Long-term reliability cannot be returned to software while an Enhanced Intel SpeedStep Technology transition up to remain within specification. Upon receiving...

Data Sheet

Page 23

... the algorithm used to support three processor states: • Both cores are in idle state • Only one core is in active C-state and the other core is indicative that the processor uses for determining when to the Processor DC Specifications section for improved control of the voltage regulator, resulting in Intel Dynamic Acceleration Technology mode. PSI-2 functionality...

... the algorithm used to support three processor states: • Both cores are in idle state • Only one core is in active C-state and the other core is indicative that the processor uses for determining when to the Processor DC Specifications section for improved control of the voltage regulator, resulting in Intel Dynamic Acceleration Technology mode. PSI-2 functionality...

Data Sheet

Page 25

... voltages on power planes to sag below their minimum values if bulk decoupling is recommended to the processor remains within the specifications listed in the tables in previous-generation processors, the processor core frequency is a multiple of the processor. Similarly, they act as coming out of an idle condition. VCC Decoupling VCC regulator solutions need to...

... voltages on power planes to sag below their minimum values if bulk decoupling is recommended to the processor remains within the specifications listed in the tables in previous-generation processors, the processor core frequency is a multiple of the processor. Similarly, they act as coming out of an idle condition. VCC Decoupling VCC regulator solutions need to...

Data Sheet

Page 26

... a high-voltage level and a 0 refers to support automatic selection of power supply voltages. Voltage Identification Definition (Sheet 1 of VID[6:0]. The VID pins for the processor are CMOS outputs driven by the processor VID circuitry. Electrical Specifications 3.3 Table 2. Voltage Identification and Power Sequencing The processor uses seven voltage identification pins,VID[6:0], to a low-voltage level.

... a high-voltage level and a 0 refers to support automatic selection of power supply voltages. Voltage Identification Definition (Sheet 1 of VID[6:0]. The VID pins for the processor are CMOS outputs driven by the processor VID circuitry. Electrical Specifications 3.3 Table 2. Voltage Identification and Power Sequencing The processor uses seven voltage identification pins,VID[6:0], to a low-voltage level.

Data Sheet

Page 27

... 0.6875 0.6750 0.6625 0.6500 0.6375 0.6250 0.6125 0.6000 0.5875 0.5750 0.5625 0.5500 0.5375 0.5250 0.5125 0.5000 0.4875 0.4750 0.4625 0.4500 0.4375 0.4250 Datasheet 27 Electrical Specifications Table 2.

... 0.6875 0.6750 0.6625 0.6500 0.6375 0.6250 0.6125 0.6000 0.5875 0.5750 0.5625 0.5500 0.5375 0.5250 0.5125 0.5000 0.4875 0.4750 0.4625 0.4500 0.4375 0.4250 Datasheet 27 Electrical Specifications Table 2.

Data Sheet

Page 28

... 0.1750 0.1625 0.1500 0.1375 0.1250 0.1125 0.1000 0.0875 0.0750 0.0625 0.0500 0.0375 0.0250 0.0125 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 28 Datasheet Electrical Specifications Table 2.

... 0.1750 0.1625 0.1500 0.1375 0.1250 0.1125 0.1000 0.0875 0.0750 0.0625 0.0500 0.0375 0.0250 0.0125 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 0.0000 28 Datasheet Electrical Specifications Table 2.

Data Sheet

Page 29

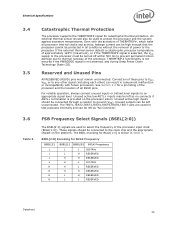

...protected in Table 3. Unused active low AGTL+ inputs may be left as "No Connects". 3.6 Table 3. Electrical Specifications 3.4 3.5 Catastrophic Thermal Protection The processor supports the THERMTRIP# signal for test purposes internally and can be left as no-connects if AGTL+ termination is provided... conditions without the removal of approximately 125°C (maximum), or if the THERMTRIP# signal is asserted, the VCC supply to the processor. THERMTRIP# functionality is not ensured if the PWRGOOD signal is shown in all RSVD pins. FSB Frequency Select Signals (BSEL[2:0]) The ...

...protected in Table 3. Unused active low AGTL+ inputs may be left as "No Connects". 3.6 Table 3. Electrical Specifications 3.4 3.5 Catastrophic Thermal Protection The processor supports the THERMTRIP# signal for test purposes internally and can be left as no-connects if AGTL+ termination is provided... conditions without the removal of approximately 125°C (maximum), or if the THERMTRIP# signal is asserted, the VCC supply to the processor. THERMTRIP# functionality is not ensured if the PWRGOOD signal is shown in all RSVD pins. FSB Frequency Select Signals (BSEL[2:0]) The ...

Data Sheet

Page 30

... by buffer type in the following sections. Similarly, "AGTL+ Output" refers to the AGTL+ output group as well as the rising edge of BCLK0. Electrical Specifications 3.7 Table 4. strobe Signals Associated Strobe REQ[4:0]#, A[16:3]# ADSTB[0]# A[35:17]# ADSTB[1]# D[15:0]#, DINV0# D[31:16]#, DINV1# DSTBP0#, DSTBN0# DSTBP1#, DSTBN1# D[47:32]#, DINV2# D[63:48...

... by buffer type in the following sections. Similarly, "AGTL+ Output" refers to the AGTL+ output group as well as the rising edge of BCLK0. Electrical Specifications 3.7 Table 4. strobe Signals Associated Strobe REQ[4:0]#, A[16:3]# ADSTB[0]# A[35:17]# ADSTB[1]# D[15:0]#, DINV0# D[31:16]#, DINV1# DSTBP0#, DSTBN0# DSTBP1#, DSTBN1# D[47:32]#, DINV2# D[63:48...

Data Sheet

Page 31

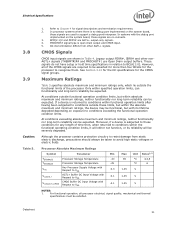

... 1.45 1.45 Unit °C °C Notes1,2 3,4,5 6 V V V NOTES: 1. If a device is subjected to these limits, but with Respect to support a debug port interposer. Electrical Specifications 3.8 3.9 Caution: Table 5. 1. In processor systems where there is open drain output and CMOS input. 5. CMOS Signals CMOS input signals are AGTL+ output-only signals. 4. See Section 3.10 for...

... 1.45 1.45 Unit °C °C Notes1,2 3,4,5 6 V V V NOTES: 1. If a device is subjected to these limits, but with Respect to support a debug port interposer. Electrical Specifications 3.8 3.9 Caution: Table 5. 1. In processor systems where there is open drain output and CMOS input. 5. CMOS Signals CMOS input signals are AGTL+ output-only signals. 4. See Section 3.10 for...