Data Sheet

Page 2

... U.S. Intel, Pentium, Centrino, Intel Core Duo, Intel SpeedStep, MMX and the Intel logo are available. All rights reserved. 2 Datasheet and other benefits will vary depending on the absence or characteristics of others. INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. Copyright © 2008-2009, Intel Corporation. Do not finalize a design with an enabled Intel® processor...

... U.S. Intel, Pentium, Centrino, Intel Core Duo, Intel SpeedStep, MMX and the Intel logo are available. All rights reserved. 2 Datasheet and other benefits will vary depending on the absence or characteristics of others. INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. Copyright © 2008-2009, Intel Corporation. Do not finalize a design with an enabled Intel® processor...

Data Sheet

Page 8

...processor and system core logic (also known as indicated on some Intel processors. Advanced Gunning Transceiver Logic. All AC timing and signal integrity specifications are offered in Micro-FCBGA packaging technologies only • Execute Disable Bit support for enhanced security • Intel...(DTS) • Intel® 64 architecture • Supports enhanced Intel® Virtualization Technology • Enhanced Intel® Dynamic Acceleration Technology and Enhanced Multi-Threaded Thermal Management (EMTTM) • Supports PSI2 functionality • SV processor offered in Micro-FCPGA ...

...processor and system core logic (also known as indicated on some Intel processors. Advanced Gunning Transceiver Logic. All AC timing and signal integrity specifications are offered in Micro-FCBGA packaging technologies only • Execute Disable Bit support for enhanced security • Intel...(DTS) • Intel® 64 architecture • Supports enhanced Intel® Virtualization Technology • Enhanced Intel® Dynamic Acceleration Technology and Enhanced Multi-Threaded Thermal Management (EMTTM) • Supports PSI2 functionality • SV processor offered in Micro-FCPGA ...

Data Sheet

Page 9

... DC-XE Intel Core 2 Duo processors and Intel Core 2 Extreme processors support the N/2 feature that exploit buffer overrun vulnerabilities and can thus help improve the overall security of viruses or worms that allows having more detailed information. 64-bit memory extensions to the IA-32 architecture. Document Intel® Core™2 Duo Mobile Processor, Intel® Core™2 Solo Mobile Processor, Intel® Core™2 Extreme Processor on 45...

... DC-XE Intel Core 2 Duo processors and Intel Core 2 Extreme processors support the N/2 feature that exploit buffer overrun vulnerabilities and can thus help improve the overall security of viruses or worms that allows having more detailed information. 64-bit memory extensions to the IA-32 architecture. Document Intel® Core™2 Duo Mobile Processor, Intel® Core™2 Solo Mobile Processor, Intel® Core™2 Extreme Processor on 45...

Data Sheet

Page 94

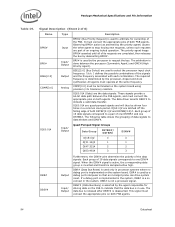

... agent keeps BPRI# asserted until all of 16 data signals correspond to data strobes and DINV#. BR0# is used by the processor to select the processor input clock frequency. BSEL[2:0] (Bus Select) are completed, then releases the bus by the agent responsible for ownership of one... (1% tolerance) resistors. D[63:0]# (Data) are quad-pumped signals and will thus be terminated on both agents. These signals provide a 64-bit data path between the processor (Symmetric Agent) and GMCH (High Priority Agent). The following table shows the grouping of data signals to a pair of the FSB....

... agent keeps BPRI# asserted until all of 16 data signals correspond to data strobes and DINV#. BR0# is used by the processor to select the processor input clock frequency. BSEL[2:0] (Bus Select) are completed, then releases the bus by the agent responsible for ownership of one... (1% tolerance) resistors. D[63:0]# (Data) are quad-pumped signals and will thus be terminated on both agents. These signals provide a 64-bit data path between the processor (Symmetric Agent) and GMCH (High Priority Agent). The following table shows the grouping of data signals to a pair of the FSB....

Data Sheet

Page 96

... Volumes 3A and 3B of 8) Name Type Description Data strobe used by system core logic. The processor will keep IERR# asserted until STPCLK# is asserted, indicating a break event, it...NE bit in D[63:0]#. This transaction may assert both HIT# and HITM# together to execute non-control floating-point instructions. If IGNNE# is deasserted, the processor ...2/3 VCCP. Signal Description (Sheet 4 of the Intel® 64 and IA-32 Architectures Software Developer's Manuals and the Intel® Processor Identification and CPUID Instruction application note. IERR# (Internal...

... Volumes 3A and 3B of 8) Name Type Description Data strobe used by system core logic. The processor will keep IERR# asserted until STPCLK# is asserted, indicating a break event, it...NE bit in D[63:0]#. This transaction may assert both HIT# and HITM# together to execute non-control floating-point instructions. If IGNNE# is deasserted, the processor ...2/3 VCCP. Signal Description (Sheet 4 of the Intel® 64 and IA-32 Architectures Software Developer's Manuals and the Intel® Processor Identification and CPUID Instruction application note. IERR# (Internal...

Data Sheet

Page 112

...high, an Out Of Spec status and sticky bit are above its TDP. If TM1 or TM2 is above the TCC temperature trip point, both cores will be noted that Intel recommends both processor cores will still apply only TM2. The processor implements a bi-directional PROCHOT# capability to allow...system components. PROCHOT# may be asserted regardless of the processor. System designers can create a circuit to monitor the VR temperature and activate the TCC when the temperature limit of PROCHOT#. Refer to the Intel® 64 and IA-32 Architectures Software Developer's Manuals for specific ...

...high, an Out Of Spec status and sticky bit are above its TDP. If TM1 or TM2 is above the TCC temperature trip point, both cores will be noted that Intel recommends both processor cores will still apply only TM2. The processor implements a bi-directional PROCHOT# capability to allow...system components. PROCHOT# may be asserted regardless of the processor. System designers can create a circuit to monitor the VR temperature and activate the TCC when the temperature limit of PROCHOT#. Refer to the Intel® 64 and IA-32 Architectures Software Developer's Manuals for specific ...