Programming Manual

Page 2

... platform software enabled for it. Current characterized errata are currently in development. 64-bit computing on the absence or characteristics of documents which processors support HT Technology. Consult with an Intel® processor supporting Hyper-Threading Technology and an HT Technology enabled chipset, BIOS and operating system. Copies of any time, without an...

... platform software enabled for it. Current characterized errata are currently in development. 64-bit computing on the absence or characteristics of documents which processors support HT Technology. Consult with an Intel® processor supporting Hyper-Threading Technology and an HT Technology enabled chipset, BIOS and operating system. Copies of any time, without an...

Programming Manual

Page 3

... Overview 2-9 2.3.2.1 C-Box PMU - On Overflow and the Consequences (PMI/Freeze 2-29 2.4.3 B-BOX Performance Monitors 2-30 2.4.3.1 B-Box Box Level PMON state 2-30 2.4.3.2 B-Box PMON state - INTEL® XEON® PROCESSOR 7500 SERIES UNCORE PROGRAMMING GUIDE CONTENTS CONTENTS CHAPTER 1 INTRODUCTION 1.1 INTRODUCTION 1-1 1.2 UNCORE PMU OVERVIEW 1-1 1.3 UNCORE PMU SUMMARY TABLES 1-2 1.4 REFERENCES 1-3 CHAPTER 2 UNCORE PERFORMANCE MONITORING 2.1 GLOBAL...

... Overview 2-9 2.3.2.1 C-Box PMU - On Overflow and the Consequences (PMI/Freeze 2-29 2.4.3 B-BOX Performance Monitors 2-30 2.4.3.1 B-Box Box Level PMON state 2-30 2.4.3.2 B-Box PMON state - INTEL® XEON® PROCESSOR 7500 SERIES UNCORE PROGRAMMING GUIDE CONTENTS CONTENTS CHAPTER 1 INTRODUCTION 1.1 INTRODUCTION 1-1 1.2 UNCORE PMU OVERVIEW 1-1 1.3 UNCORE PMU SUMMARY TABLES 1-2 1.4 REFERENCES 1-3 CHAPTER 2 UNCORE PERFORMANCE MONITORING 2.1 GLOBAL...

Programming Manual

Page 4

...An Event To Monitor - Counter/Control Pairs 2-100 M-Box PMU Filter Registers 2-102 M-Box PMU Subcontrol Registers - INTEL® XEON® PROCESSOR 7500 SERIES UNCORE PROGRAMMING GUIDE CONTENTS 2.5.4.2 2.5.4.3 2.5.5 2.5.6 2.6 2.6.1 2.6.1.1 2.6.1.2 2.6.1.3 2.6.1.4 2.6.2 2.6.2.1 2.6.2.2 2.6.3 2.6.3.1 2.6.3.2 2.6.3.3 2.6.3.4 2.6.3.5 2.6.3.6 2.6.4 2.6.4.1 2.6.5 2.6.6 2.7 2.7.1 2.7.2 2.7.2.1 2.7.3 2.7.3.1 2.7.3.2 2.7.4 2.7.4.1 2.7.4.2 2.7.4.3 2.7.4.4 2.7.5 2.7.5.1 2.7.6 2.7.7 2.8 2.8.1 2.8.2 2.8.2.1 2.8.3 2.8.3.1 2.8.3.2 2.8.4 2.8.4.1 2.8.5 2.8.6 2.9 On Queue Occupancy Usage 2-51 On Packet...

...An Event To Monitor - Counter/Control Pairs 2-100 M-Box PMU Filter Registers 2-102 M-Box PMU Subcontrol Registers - INTEL® XEON® PROCESSOR 7500 SERIES UNCORE PROGRAMMING GUIDE CONTENTS 2.5.4.2 2.5.4.3 2.5.5 2.5.6 2.6 2.6.1 2.6.1.1 2.6.1.2 2.6.1.3 2.6.1.4 2.6.2 2.6.2.1 2.6.2.2 2.6.3 2.6.3.1 2.6.3.2 2.6.3.3 2.6.3.4 2.6.3.5 2.6.3.6 2.6.4 2.6.4.1 2.6.5 2.6.6 2.7 2.7.1 2.7.2 2.7.2.1 2.7.3 2.7.3.1 2.7.3.2 2.7.4 2.7.4.1 2.7.4.2 2.7.4.3 2.7.4.4 2.7.5 2.7.5.1 2.7.6 2.7.7 2.8 2.8.1 2.8.2 2.8.2.1 2.8.3 2.8.3.1 2.8.3.2 2.8.4 2.8.4.1 2.8.5 2.8.6 2.9 On Queue Occupancy Usage 2-51 On Packet...

Programming Manual

Page 6

INTEL® XEON® PROCESSOR 7500 SERIES UNCORE PROGRAMMING GUIDE This page intentionally left blank FIGURES

INTEL® XEON® PROCESSOR 7500 SERIES UNCORE PROGRAMMING GUIDE This page intentionally left blank FIGURES

Programming Manual

Page 7

... 1-2 Uncore Performance Monitoring MSRs 1-2 Global Performance Monitoring Control MSRs 2-3 U_MSR_PMON_GLOBAL_CTL Register - Field Definitions 2-5 U_MSR_PMON_CTR Register - Field Definitions 2-14 C_MSR_PMON_GLOBAL_OVF_CTL Register - INTEL® XEON® PROCESSOR 7500 SERIES UNCORE PROGRAMMING GUIDE TABLES TABLES Table 1-1. Table 1-2. Table 2-2. Table 2-6. Table 2-8. Table 2-13. Table 2-14. Table 2-17. Table 2-18...Masks for EOT_ROLL_DEPTH_ACC 2-90 Unit Masks for GLOBAL_ARB_BID_FAIL 2-91 Unit Masks for NEW_PACKETS_RECV 2-92 Unit Masks for QUE_ARB_BID 2-93

... 1-2 Uncore Performance Monitoring MSRs 1-2 Global Performance Monitoring Control MSRs 2-3 U_MSR_PMON_GLOBAL_CTL Register - Field Definitions 2-5 U_MSR_PMON_CTR Register - Field Definitions 2-14 C_MSR_PMON_GLOBAL_OVF_CTL Register - INTEL® XEON® PROCESSOR 7500 SERIES UNCORE PROGRAMMING GUIDE TABLES TABLES Table 1-1. Table 1-2. Table 2-2. Table 2-6. Table 2-8. Table 2-13. Table 2-14. Table 2-17. Table 2-18...Masks for EOT_ROLL_DEPTH_ACC 2-90 Unit Masks for GLOBAL_ARB_BID_FAIL 2-91 Unit Masks for NEW_PACKETS_RECV 2-92 Unit Masks for QUE_ARB_BID 2-93

Programming Manual

Page 8

.... Table 2-79. Table 2-81. Table 2-84. Table 2-89. Table 2-92. Table 2-93. Table 2-95. Table 2-100. Unit Masks for QUE_ARB_BID_FAIL 2-93 Unit Masks for TARGET_AVAILABLE 2-94 M-Box Performance Monitoring MSRs 2-98 M_MSR_PERF_GLOBAL_CTL Register Fields 2-100 M_MSR_PERF_GLOBAL_STATUS ...Field Definitions 2-106 M_MSR_PMU_PLD Register - Table 2-80. Table 2-82. Table 2-64. Table 2-71. Table 2-101. INTEL® XEON® PROCESSOR 7500 SERIES UNCORE PROGRAMMING GUIDE TABLES Table 2-61. Field Definitions 2-104 M_CSR_ISS_PMU Register - Field Definitions 2-102 M_MSR_PMU_DSP Register ...

.... Table 2-79. Table 2-81. Table 2-84. Table 2-89. Table 2-92. Table 2-93. Table 2-95. Table 2-100. Unit Masks for QUE_ARB_BID_FAIL 2-93 Unit Masks for TARGET_AVAILABLE 2-94 M-Box Performance Monitoring MSRs 2-98 M_MSR_PERF_GLOBAL_CTL Register Fields 2-100 M_MSR_PERF_GLOBAL_STATUS ...Field Definitions 2-106 M_MSR_PMU_PLD Register - Table 2-80. Table 2-82. Table 2-64. Table 2-71. Table 2-101. INTEL® XEON® PROCESSOR 7500 SERIES UNCORE PROGRAMMING GUIDE TABLES Table 2-61. Field Definitions 2-104 M_CSR_ISS_PMU Register - Field Definitions 2-102 M_MSR_PMU_DSP Register ...

Programming Manual

Page 9

... and extract information from the monitors. INTEL® XEON® PROCESSOR 7500 SERIES UNCORE PROGRAMMING GUIDE INTRODUCTION CHAPTER 1 INTRODUCTION 1.1 INTRODUCTION Figure 1-1 provides an Intel® Xeon® Processor 7500 Series block diagram. Software may be executed on any core. 1-1 Each of an overflowing uncore counter on coreId = 0, threadId = 0. Intel Xeon Processor 7500 Series Block Diagram 1.2 Uncore PMU...

... and extract information from the monitors. INTEL® XEON® PROCESSOR 7500 SERIES UNCORE PROGRAMMING GUIDE INTRODUCTION CHAPTER 1 INTRODUCTION 1.1 INTRODUCTION Figure 1-1 provides an Intel® Xeon® Processor 7500 Series block diagram. Software may be executed on any core. 1-1 Each of an overflowing uncore counter on coreId = 0, threadId = 0. Intel Xeon Processor 7500 Series Block Diagram 1.2 Uncore PMU...

Programming Manual

Page 10

...-0xD30 Counter/Config Registers 0xD22-0xD20 Global (Control/Status/Ovf Control) 0xD1B-0xD10 Counter/Config Registers 0xD02-0xD00 Global (Control/Status/Ovf Control) 1-2 INTEL® XEON® PROCESSOR 7500 SERIES UNCORE PROGRAMMING GUIDE INTRODUCTION The general performance monitoring capabilities in each box are outlined in the following table. 1.3 Box C-Box S-Box B-Box...

...-0xD30 Counter/Config Registers 0xD22-0xD20 Global (Control/Status/Ovf Control) 0xD1B-0xD10 Counter/Config Registers 0xD02-0xD00 Global (Control/Status/Ovf Control) 1-2 INTEL® XEON® PROCESSOR 7500 SERIES UNCORE PROGRAMMING GUIDE INTRODUCTION The general performance monitoring capabilities in each box are outlined in the following table. 1.3 Box C-Box S-Box B-Box...

Programming Manual

Page 11

... 2.3, "C-Box Performance Monitoring" • Section 2.4, "B-Box Performance Monitoring" • Section 2.5, "S-Box Performance Monitoring" • Section 2.6, "R-Box Performance Monitoring" • Section 2.7, "M-Box Performance Monitoring" 1-3 INTEL® XEON® PROCESSOR 7500 SERIES UNCORE PROGRAMMING GUIDE INTRODUCTION Box M-Box 1 M-Box 0 S-Box Counters S-Box 1 S-Box 0 B-Box Counters B-Box 1 B-Box 0 U-Box Counters U-Box W-Box Counters W-Box Table 1-2.

... 2.3, "C-Box Performance Monitoring" • Section 2.4, "B-Box Performance Monitoring" • Section 2.5, "S-Box Performance Monitoring" • Section 2.6, "R-Box Performance Monitoring" • Section 2.7, "M-Box Performance Monitoring" 1-3 INTEL® XEON® PROCESSOR 7500 SERIES UNCORE PROGRAMMING GUIDE INTRODUCTION Box M-Box 1 M-Box 0 S-Box Counters S-Box 1 S-Box 0 B-Box Counters B-Box 1 B-Box 0 U-Box Counters U-Box W-Box Counters W-Box Table 1-2.

Programming Manual

Page 12

INTEL® XEON® PROCESSOR 7500 SERIES UNCORE PROGRAMMING GUIDE • Section 2.8, "W-Box Performance Monitoring" • Section 2.9, "Packet Matching Reference" INTRODUCTION 1-4

INTEL® XEON® PROCESSOR 7500 SERIES UNCORE PROGRAMMING GUIDE • Section 2.8, "W-Box Performance Monitoring" • Section 2.9, "Packet Matching Reference" INTRODUCTION 1-4

Programming Manual

Page 13

... PMI on Counter Overflow The uncore may also be configured to, upon detection of a performance counter overflow, send a PMI signal to the core executing the monitoring software. b) Select event to monitor: Determine what events should be disabled. Set B_MSR_PMON_EVT_SEL3.ev_sel to 0x03 to capture them (i.e.... overflow, disable (or 'freeze') all other counters in the individual counter's control register must be set to 1. The Intel® Xeon® Processor 7500 Series uncore performance monitors may be configured to respond to this overflow with two basic actions: 2.1.1.1 Freezing on...

... PMI on Counter Overflow The uncore may also be configured to, upon detection of a performance counter overflow, send a PMI signal to the core executing the monitoring software. b) Select event to monitor: Determine what events should be disabled. Set B_MSR_PMON_EVT_SEL3.ev_sel to 0x03 to capture them (i.e.... overflow, disable (or 'freeze') all other counters in the individual counter's control register must be set to 1. The Intel® Xeon® Processor 7500 Series uncore performance monitors may be configured to respond to this overflow with two basic actions: 2.1.1.1 Freezing on...

Programming Manual

Page 14

... SERIES UNCORE PROGRAMMING GUIDE d) Enable counting at the box-level: Enable counters within the Intel Xeon Processor 7500 Series uncore. UNCORE PERFORMANCE MONITORING e) Select how to 4. Capturing a performance monitoring sample every 'X cycles' (the fixed counter in ... value of this mechanism. Set the .rst_all field to freeze on . b) Frozen counters - If sampling: To set U_MSR_PMON_GLOBAL_CTL.pmi_core_sel to which core the monitoring thread is executing on overflow and send notification when it happens, the next question is to read the U_MSR_PMON_GLOBAL_STATUS.ov_* bits to 1....

... SERIES UNCORE PROGRAMMING GUIDE d) Enable counting at the box-level: Enable counters within the Intel Xeon Processor 7500 Series uncore. UNCORE PERFORMANCE MONITORING e) Select how to 4. Capturing a performance monitoring sample every 'X cycles' (the fixed counter in ... value of this mechanism. Set the .rst_all field to freeze on . b) Frozen counters - If sampling: To set U_MSR_PMON_GLOBAL_CTL.pmi_core_sel to which core the monitoring thread is executing on overflow and send notification when it happens, the next question is to read the U_MSR_PMON_GLOBAL_STATUS.ov_* bits to 1....

Programming Manual

Page 15

... indicates if a disable was received from one of the boxes. Therefore it is detected in any uncore counters will be summarized in U_MSR_PMON_GLOBAL_STATUS. INTEL® XEON® PROCESSOR 7500 SERIES UNCORE PROGRAMMING GUIDE UNCORE PERFORMANCE MONITORING a) Clear all PMUs in the uncore, both to exert global control and collect box-level information...

... indicates if a disable was received from one of the boxes. Therefore it is detected in any uncore counters will be summarized in U_MSR_PMON_GLOBAL_STATUS. INTEL® XEON® PROCESSOR 7500 SERIES UNCORE PROGRAMMING GUIDE UNCORE PERFORMANCE MONITORING a) Clear all PMUs in the uncore, both to exert global control and collect box-level information...

Programming Manual

Page 16

... Description 31 30 29:4 3 2 1 0 0 Clear Condition Change 0 Clear PMI Received bit. 0 Read zero; Send PMI to core 0 10000000 - en 0 0 Enable U-Box PMON counters Table 2-3. U_MSR_PMON_GLOBAL_STATUS Register - U_MSR_PMON_GLOBAL_CTL Register - Field Definitions Field cond pmi ig... Val Description 31 30 31:4 3 2 1 0 0 Condition Change 0 PMI Received from a U-Box PMON register. INTEL® XEON® PROCESSOR 7500 SERIES UNCORE PROGRAMMING GUIDE UNCORE PERFORMANCE MONITORING Table 2-2. U_MSR_PMON_GLOBAL_OVF_CTL Register - Send PMI to U-Box for Box with overflowing ...

... Description 31 30 29:4 3 2 1 0 0 Clear Condition Change 0 Clear PMI Received bit. 0 Read zero; Send PMI to core 0 10000000 - en 0 0 Enable U-Box PMON counters Table 2-3. U_MSR_PMON_GLOBAL_STATUS Register - U_MSR_PMON_GLOBAL_CTL Register - Field Definitions Field cond pmi ig... Val Description 31 30 31:4 3 2 1 0 0 Condition Change 0 PMI Received from a U-Box PMON register. INTEL® XEON® PROCESSOR 7500 SERIES UNCORE PROGRAMMING GUIDE UNCORE PERFORMANCE MONITORING Table 2-2. U_MSR_PMON_GLOBAL_OVF_CTL Register - Send PMI to U-Box for Box with overflowing ...

Programming Manual

Page 17

... control bits include: - .pmi_en which can capture transitions from no event to Section 2.1, "Global Performance Monitoring Control" for the Intel Xeon Processor 7500 Series. writes ignored. (?) 0 Reserved; Must write to do if an overflow is undefined. 0 Read zero; writes ignored... Read zero; writes ignored. (?) 0 Select event to enable counting. writes ignored. (?) 0 Local Counter Enable. INTEL® XEON® PROCESSOR 7500 SERIES UNCORE PROGRAMMING GUIDE UNCORE PERFORMANCE MONITORING 2.2 U-Box Performance Monitoring The U-Box serves as the system configuration controller...

... control bits include: - .pmi_en which can capture transitions from no event to Section 2.1, "Global Performance Monitoring Control" for the Intel Xeon Processor 7500 Series. writes ignored. (?) 0 Reserved; Must write to do if an overflow is undefined. 0 Read zero; writes ignored... Read zero; writes ignored. (?) 0 Select event to enable counting. writes ignored. (?) 0 Local Counter Enable. INTEL® XEON® PROCESSOR 7500 SERIES UNCORE PROGRAMMING GUIDE UNCORE PERFORMANCE MONITORING 2.2 U-Box Performance Monitoring The U-Box serves as the system configuration controller...

Programming Manual

Page 18

INTEL® XEON® PROCESSOR 7500 SERIES UNCORE PROGRAMMING GUIDE UNCORE PERFORMANCE MONITORING The U-Box performance monitor data register is detected. Table 2-7. ...Field Definitions Field event_count Bits HW Reset Val Description 47:0 0 48-bit performance event counter 2.2.2 U-Box Performance Monitoring Events The set of core IPIs sent 1 Recoverable 1 Corrected Error 2-6 Performance Monitor Events for U-Box Events Symbol Name BUF_VALID_LOCAL_INT BUF_VALID_REMOTE_INT BUF_VALID_LOCK BUF_VALID_STST BUF_VALID_SPC_CYCLES U2R_REQUESTS U2B_REQUEST_CYCLES WOKEN IPIS_SENT...

INTEL® XEON® PROCESSOR 7500 SERIES UNCORE PROGRAMMING GUIDE UNCORE PERFORMANCE MONITORING The U-Box performance monitor data register is detected. Table 2-7. ...Field Definitions Field event_count Bits HW Reset Val Description 47:0 0 48-bit performance event counter 2.2.2 U-Box Performance Monitoring Events The set of core IPIs sent 1 Recoverable 1 Corrected Error 2-6 Performance Monitor Events for U-Box Events Symbol Name BUF_VALID_LOCAL_INT BUF_VALID_REMOTE_INT BUF_VALID_LOCK BUF_VALID_STST BUF_VALID_SPC_CYCLES U2R_REQUESTS U2B_REQUEST_CYCLES WOKEN IPIS_SENT...

Programming Manual

Page 19

...Special Cycle packet buffer contains a valid entry. 'Special Cycles' are NcMsgS packets generated by the U-Box and broadcast to internal cores to cover such things as Shutdown, Invd_Ack and WbInvd_Ack conditions. Inc/Cyc: 1, • Definition: Number of uncore cycles the ... Event Max Code Inc/Cyc Description 0x1E5 0x1E6 1 Uncorrected Error 1 Fatal Error 2.2.4 U-Box Performance Monitor Event List This section enumerates Intel Xeon Processor 7500 Series uncore performance monitoring events for the U-Box. BUF_VALID_LOCK • Title: Lock Buffer Valid • Category: U-Box Events ...

...Special Cycle packet buffer contains a valid entry. 'Special Cycles' are NcMsgS packets generated by the U-Box and broadcast to internal cores to cover such things as Shutdown, Invd_Ack and WbInvd_Ack conditions. Inc/Cyc: 1, • Definition: Number of uncore cycles the ... Event Max Code Inc/Cyc Description 0x1E5 0x1E6 1 Uncorrected Error 1 Fatal Error 2.2.4 U-Box Performance Monitor Event List This section enumerates Intel Xeon Processor 7500 Series uncore performance monitoring events for the U-Box. BUF_VALID_LOCK • Title: Lock Buffer Valid • Category: U-Box Events ...

Programming Manual

Page 20

INTEL® XEON® PROCESSOR 7500 SERIES UNCORE PROGRAMMING GUIDE FATAL_ERR • Title: Fatal Errors • Category: U-Box Events • Event Code: 0x1E6, Max. Inc/Cyc: 1, • Definition: Number of recoverable errors. Inc/Cyc: 1, • Definition: Number of core IPIs sent. WOKEN • Title: Number Cores... Requests • Category: U-Box Events • Event Code: 0x050, Max. UNCORE PERFORMANCE MONITORING 2-8 IPIS_SENT • Title: Number Core IPIs Sent • Category: U-Box Events • Event Code: 0x0F9, Max. Inc/Cyc: 1, • Definition: Number U...

INTEL® XEON® PROCESSOR 7500 SERIES UNCORE PROGRAMMING GUIDE FATAL_ERR • Title: Fatal Errors • Category: U-Box Events • Event Code: 0x1E6, Max. Inc/Cyc: 1, • Definition: Number of recoverable errors. Inc/Cyc: 1, • Definition: Number of core IPIs sent. WOKEN • Title: Number Cores... Requests • Category: U-Box Events • Event Code: 0x050, Max. UNCORE PERFORMANCE MONITORING 2-8 IPIS_SENT • Title: Number Core IPIs Sent • Category: U-Box Events • Event Code: 0x0F9, Max. Inc/Cyc: 1, • Definition: Number U...

Programming Manual

Page 21

... SERIES UNCORE PROGRAMMING GUIDE UNCORE PERFORMANCE MONITORING 2.3 C-Box Performance Monitoring 2.3.1 Overview of the C-Box For the Intel Xeon Processor 7500 Series, the LLC coherence engine (C-Box) manages the interface between the cores within the socket that pass through the socket's LLC remain coherent. For information on how to setup a monitoring session, refer to...

... SERIES UNCORE PROGRAMMING GUIDE UNCORE PERFORMANCE MONITORING 2.3 C-Box Performance Monitoring 2.3.1 Overview of the C-Box For the Intel Xeon Processor 7500 Series, the LLC coherence engine (C-Box) manages the interface between the cores within the socket that pass through the socket's LLC remain coherent. For information on how to setup a monitoring session, refer to...

Programming Manual

Page 22

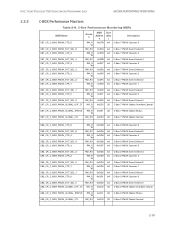

... WO_R L O 0xDC2 32 C-Box 3 PMON Global Overflow Control CB3_CR_C_MSR_PMON_GLOBAL_STATUS RW_R W 0xDC1 32 C-Box 3 PMON Global Status CB3_CR_C_MSR_PMON_GLOBAL_CTL RW_RO 0xDC0 32 C-Box 3 PMON Global Control 2-10 INTEL® XEON® PROCESSOR 7500 SERIES UNCORE PROGRAMMING GUIDE UNCORE PERFORMANCE MONITORING 2.3.3 C-BOX Performance Monitors Table 2-9.

... WO_R L O 0xDC2 32 C-Box 3 PMON Global Overflow Control CB3_CR_C_MSR_PMON_GLOBAL_STATUS RW_R W 0xDC1 32 C-Box 3 PMON Global Status CB3_CR_C_MSR_PMON_GLOBAL_CTL RW_RO 0xDC0 32 C-Box 3 PMON Global Control 2-10 INTEL® XEON® PROCESSOR 7500 SERIES UNCORE PROGRAMMING GUIDE UNCORE PERFORMANCE MONITORING 2.3.3 C-BOX Performance Monitors Table 2-9.