English Manual.

Page 9

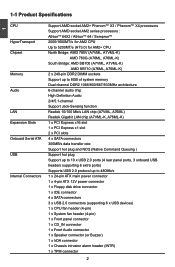

1-1 Product Specifications 1 CPU Support AMD socket AM2+ PhenomTM X3 / PhenomTM X4 processors Support AMD socket AM2 series processors : AthlonTM 64X2 / AthlonTM 64 / SempronTM HyperTransport 2000/1600MT/s for AM2 CPU Up to 5200MT/s (HT3.0) for AM2+ CPU Chipset North Bridge: AMD 780V (A7VML, A7VML-K) AMD 760G (A76ML, A76ML-K) South Bridge: AMD SB700 (A7VML, A7VML-K) AMD SB710 (A76ML, A76ML-K) Memory 2 x 240-pin DDR2 DIMM sockets Support up...

1-1 Product Specifications 1 CPU Support AMD socket AM2+ PhenomTM X3 / PhenomTM X4 processors Support AMD socket AM2 series processors : AthlonTM 64X2 / AthlonTM 64 / SempronTM HyperTransport 2000/1600MT/s for AM2 CPU Up to 5200MT/s (HT3.0) for AM2+ CPU Chipset North Bridge: AMD 780V (A7VML, A7VML-K) AMD 760G (A76ML, A76ML-K) South Bridge: AMD SB700 (A7VML, A7VML-K) AMD SB710 (A76ML, A76ML-K) Memory 2 x 240-pin DDR2 DIMM sockets Support up...

English Manual.

Page 38

...of the target clock frequency. DRAM Timing Configuration CMOS Setup Utility - The value that BIOS programs into the memory controller is determined from the supported CAS latencies at given clock frequencies of each DIMM. ► TRCD (RAS-to-CAS Delay) This item allows you to select the write... ► DRAM Timing Mode When both DCTs (DRAM controller) are : [Auto], [DCT 0], [DCT 1], [Both]. [DCT 1] and [Both] will appear only in AM2+ CPU. ► CAS Latency The number of a Different Bank) This item allows you to select a delay time (in clock cycles) between the CAS# and RAS# strobe...

...of the target clock frequency. DRAM Timing Configuration CMOS Setup Utility - The value that BIOS programs into the memory controller is determined from the supported CAS latencies at given clock frequencies of each DIMM. ► TRCD (RAS-to-CAS Delay) This item allows you to select the write... ► DRAM Timing Mode When both DCTs (DRAM controller) are : [Auto], [DCT 0], [DCT 1], [Both]. [DCT 1] and [Both] will appear only in AM2+ CPU. ► CAS Latency The number of a Different Bank) This item allows you to select a delay time (in clock cycles) between the CAS# and RAS# strobe...