Product Specification

Page 2

... Architecture Section; Updated Section 3.3.4.1 Memory Reservation for S5520HCT - Added Appendix G Installation Guidelines - Updated Section 2.1, the feature set table - Updated Appendix G - Revision History Intel® Server Boards S5520HC, S5500HCV, and S5520HCT TPS Revision History Date February 2008 March 2008 March... Content Update Updated sections 2.1 and 3.2 Updated product code and processor support related information. and updated Appendix. - Updated Boot Option BIOS Setup Menu (Table 34 and Figure 36) - Updated Table 2, Table 8, Table 9, Table 25, Figure 13, and Figure 14...

... Architecture Section; Updated Section 3.3.4.1 Memory Reservation for S5520HCT - Added Appendix G Installation Guidelines - Updated Section 2.1, the feature set table - Updated Appendix G - Revision History Intel® Server Boards S5520HC, S5500HCV, and S5520HCT TPS Revision History Date February 2008 March 2008 March... Content Update Updated sections 2.1 and 3.2 Updated product code and processor support related information. and updated Appendix. - Updated Boot Option BIOS Setup Menu (Table 34 and Figure 36) - Updated Table 2, Table 8, Table 9, Table 25, Figure 13, and Figure 14...

Product Specification

Page 5

... 3.4.2 USB 2.0 Support ...41 3.5 PCI Subsystem...42 3.5.1 PCI Express* Riser Slot (S5520HC - Supported only on S5520HCT 52 3.13.1 Overview...52 3.13.2 TPM security BIOS 52 3.13.3 Intel® Trusted Execution Technology (Intel® TXT 55 3.14 ACPI Support ...59 3.15 Intel® Virtualization Technology 60 3.15.1 Intel® Virtualization Technology for Management (WS-MAN 65 4.2.5 Embedded Web server...

... 3.4.2 USB 2.0 Support ...41 3.5 PCI Subsystem...42 3.5.1 PCI Express* Riser Slot (S5520HC - Supported only on S5520HCT 52 3.13.1 Overview...52 3.13.2 TPM security BIOS 52 3.13.3 Intel® Trusted Execution Technology (Intel® TXT 55 3.14 ACPI Support ...59 3.15 Intel® Virtualization Technology 60 3.15.1 Intel® Virtualization Technology for Management (WS-MAN 65 4.2.5 Embedded Web server...

Product Specification

Page 6

...; Light Guided Diagnostics 122 8.1 5-volt Stand-by Outputs 131 9.4.3 Remote Sense...132 vi Revision 1.8 Intel order number E39529-013 Table of Contents Intel® Server Boards S5520HC, S5500HCV, and S5520HCT TPS 5.3 BIOS Setup Utility...72 5.3.1 Operation ...72 5.3.2 Server Platform Setup Utility Screens 75 6. Connector/Header Locations and Pin-outs 108 6.1 Board Connector Information 108 6.2 Power...

...; Light Guided Diagnostics 122 8.1 5-volt Stand-by Outputs 131 9.4.3 Remote Sense...132 vi Revision 1.8 Intel order number E39529-013 Table of Contents Intel® Server Boards S5520HC, S5500HCV, and S5520HCT TPS 5.3 BIOS Setup Utility...72 5.3.1 Operation ...72 5.3.2 Server Platform Setup Utility Screens 75 6. Connector/Header Locations and Pin-outs 108 6.1 Board Connector Information 108 6.2 Power...

Product Specification

Page 8

...Mounting Hole Locations 8 Figure 5. Primary Side Keep-out Zone (2 of Figures Figure 1. Primary Side Air Duct Keep-out Zone 13 Figure 10. BIOS setting for TXT 59 Figure 26. Setup Utility - Main Screen Display 76 Figure 29. Rear I/O Layout ...16 Figure 13. Unified Retention System ... 92 Figure 39. Setup Utility - Setup Utility - System Acoustic and Performance Configuration Screen Display ... 91 Figure 38. List of Figures Intel® Server Boards S5520HC, S5500HCV, and S5520HCT TPS List of 2 12 Figure 9. Major Connector Pin-1 Locations (1 of 2 9 Figure 6. Setup Utility...

...Mounting Hole Locations 8 Figure 5. Primary Side Keep-out Zone (2 of Figures Figure 1. Primary Side Air Duct Keep-out Zone 13 Figure 10. BIOS setting for TXT 59 Figure 26. Setup Utility - Main Screen Display 76 Figure 29. Rear I/O Layout ...16 Figure 13. Unified Retention System ... 92 Figure 39. Setup Utility - Setup Utility - System Acoustic and Performance Configuration Screen Display ... 91 Figure 38. List of Figures Intel® Server Boards S5520HC, S5500HCV, and S5520HCT TPS List of 2 12 Figure 9. Major Connector Pin-1 Locations (1 of 2 9 Figure 6. Setup Utility...

Product Specification

Page 10

... System Information Fields 98 Table 35. Setup Utility - List of Tables Intel® Server Boards S5520HC, S5500HCV, and S5520HCT TPS List of Tables Table 1. Intel® Server Board S5520HC PCI Riser Slot (Slot 6 43 Table 11. S5520HC, S5500HCV and S5520HCT Fan Domain Table 69 Table 19. BIOS Setup Page Layout 73 Table 20. Onboard NIC Status LED 51...

... System Information Fields 98 Table 35. Setup Utility - List of Tables Intel® Server Boards S5520HC, S5500HCV, and S5520HCT TPS List of Tables Table 1. Intel® Server Board S5520HC PCI Riser Slot (Slot 6 43 Table 11. S5520HC, S5500HCV and S5520HCT Fan Domain Table 69 Table 19. BIOS Setup Page Layout 73 Table 20. Onboard NIC Status LED 51...

Product Specification

Page 15

...BIOS Setup Utility ƒ Chapter 6 - Integration and Usage Tips ƒ Appendix B - POST Code Diagnostic LED Decoder ƒ Appendix F - Installation Guidelines ƒ Glossary ƒ Reference Documents 1.2 Server Board Use Disclaimer Intel® Server Boards contain a number of high-density VLSI (Very-large-scale integration) and power delivery components that when Intel... Tables ƒ Appendix D - Intel® Server Boards S5520HC, S5500HCV, and S5520HCT TPS Introduction 1. Platform Specific BMC Appendix ƒ Appendix E - Intel® Light Guided Diagnostics ƒ...

...BIOS Setup Utility ƒ Chapter 6 - Integration and Usage Tips ƒ Appendix B - POST Code Diagnostic LED Decoder ƒ Appendix F - Installation Guidelines ƒ Glossary ƒ Reference Documents 1.2 Server Board Use Disclaimer Intel® Server Boards contain a number of high-density VLSI (Very-large-scale integration) and power delivery components that when Intel... Tables ƒ Appendix D - Intel® Server Boards S5520HC, S5500HCV, and S5520HCT TPS Introduction 1. Platform Specific BMC Appendix ƒ Appendix E - Intel® Light Guided Diagnostics ƒ...

Product Specification

Page 18

Overview Intel® Server Boards S5520HC, S5500HCV, and S5520HCT TPS Feature Server Management BIOS Flash Form Factor Compatible Intel® Server Chassis Description • Onboard ServerEngines* LLC Pilot II* Controller ƒ Integrated Baseboard Management Controller (Integrated BMC), IPMI 2.0 compliant ƒ Integrated Super I/O on LPC interface • Support for Intel® Remote Management Module 3 • Intel® Light-Guided...

Overview Intel® Server Boards S5520HC, S5500HCV, and S5520HCT TPS Feature Server Management BIOS Flash Form Factor Compatible Intel® Server Chassis Description • Onboard ServerEngines* LLC Pilot II* Controller ƒ Integrated Baseboard Management Controller (Integrated BMC), IPMI 2.0 compliant ƒ Integrated Super I/O on LPC interface • Support for Intel® Remote Management Module 3 • Intel® Light-Guided...

Product Specification

Page 37

Intel® Server Boards S5520HC, S5500HCV, and S5520HCT TPS Functional Architecture Error Processor family not identical Processor stepping mismatch Table 2. Mixed Processor Configurations Severity Halt Pause System Action The BIOS detects the error condition and responds as follows: - Does not disable the processor. - Halts the system and will not boot until the fault condition is...

Intel® Server Boards S5520HC, S5500HCV, and S5520HCT TPS Functional Architecture Error Processor family not identical Processor stepping mismatch Table 2. Mixed Processor Configurations Severity Halt Pause System Action The BIOS detects the error condition and responds as follows: - Does not disable the processor. - Halts the system and will not boot until the fault condition is...

Product Specification

Page 38

... successfully. The Default is operating below power, temperature, and current limits. Functional Architecture Intel® Server Boards S5520HC, S5500HCV, and S5520HCT TPS Error Processor Intel® QuickPath Interconnect speeds not identical Processor microcode missing Severity Halt Minor System Action The BIOS detects the error condition and responds as follows: - Adjusts all QPI links cannot be...

... successfully. The Default is operating below power, temperature, and current limits. Functional Architecture Intel® Server Boards S5520HC, S5500HCV, and S5520HCT TPS Error Processor Intel® QuickPath Interconnect speeds not identical Processor microcode missing Severity Halt Minor System Action The BIOS detects the error condition and responds as follows: - Adjusts all QPI links cannot be...

Product Specification

Page 39

...protocol in the heatsink, provides the necessary compressive load for active core count. This is executed. You can do this feature. The BIOS setup provides an option to enable or disable this through hints to the processor to minimize cache misses when a demand read is ...captive to the heatsink and only require a Phillips* screwdriver to attach to selectively enable one or more cores. Intel® Server Boards S5520HC, S5500HCV, and S5520HCT TPS Functional Architecture z Intel® 64 mode when 64-bit extension technology is to perform a data pre-fetch and install it in...

...protocol in the heatsink, provides the necessary compressive load for active core count. This is executed. You can do this feature. The BIOS setup provides an option to enable or disable this through hints to the processor to minimize cache misses when a demand read is ...captive to the heatsink and only require a Phillips* screwdriver to attach to selectively enable one or more cores. Intel® Server Boards S5520HC, S5500HCV, and S5520HCT TPS Functional Architecture z Intel® 64 mode when 64-bit extension technology is to perform a data pre-fetch and install it in...

Product Specification

Page 41

... are identified as Channels A, B, and C. z DIMMs are organized into autonomous memory. 3.3.1 Memory Subsystem Nomenclature The nomenclature for DIMM sockets implemented in the Intel® Server Boards S5520HC, S5500HCV and S5520HCT is represented in the BIOS setup, such as RAS, Error Management, and so forth, are identified as Channels D, E, and F. The memory channels for the...

... are identified as Channels A, B, and C. z DIMMs are organized into autonomous memory. 3.3.1 Memory Subsystem Nomenclature The nomenclature for DIMM sockets implemented in the Intel® Server Boards S5520HC, S5500HCV and S5520HCT is represented in the BIOS setup, such as RAS, Error Management, and so forth, are identified as Channels D, E, and F. The memory channels for the...

Product Specification

Page 44

...During memory discovery, the BIOS arrives at a fastest common frequency that matches the requirements of all components of the memory system and then configures the DDR3 DIMMs for the QPI links. and Dual-Rank - Functional Architecture Intel® Server Boards S5520HC, S5500HCV, and S5520HCT TPS „ Mixing of... RDIMMs and UDIMMs is not supported. „ Mixing memory type, size, speed and/or rank on this platform by Intel „ Non-ECC memory is not supported...

...During memory discovery, the BIOS arrives at a fastest common frequency that matches the requirements of all components of the memory system and then configures the DDR3 DIMMs for the QPI links. and Dual-Rank - Functional Architecture Intel® Server Boards S5520HC, S5500HCV, and S5520HCT TPS „ Mixing of... RDIMMs and UDIMMs is not supported. „ Mixing memory type, size, speed and/or rank on this platform by Intel „ Non-ECC memory is not supported...

Product Specification

Page 46

... POST if the "Quiet Boot" is set to 64 buses, rather than 4 GB. The BIOS displays the "Effective Memory" of POST. For details, see ). Functional Architecture Intel® Server Boards S5520HC, S5500HCV, and S5520HCT TPS 3.3.4 z z z z Publishing System Memory The BIOS displays the "Total Memory" of standard PCI Express* MMIO configuration space. In addition to this...

... POST if the "Quiet Boot" is set to 64 buses, rather than 4 GB. The BIOS displays the "Effective Memory" of POST. For details, see ). Functional Architecture Intel® Server Boards S5520HC, S5500HCV, and S5520HCT TPS 3.3.4 z z z z Publishing System Memory The BIOS displays the "Total Memory" of standard PCI Express* MMIO configuration space. In addition to this...

Product Specification

Page 47

...and support the right population. The BIOS enables both the memory cells and the data paths emanating from the DDR3 DIMMs. The BIOS also uses the Memory BIST to Section 3.3.9. Intel® Server Boards S5520HC, S5500HCV, and S5520HCT TPS Functional Architecture • Bank ... are supported only if both CPU sockets are installed in slots for mirroring, the BIOS disables it automatically. 3.3.8 Memory RAS 3.3.8.1 RAS Features The Intel® Server Boards S5520HC, S5500HCV and S5520HCT support the following memory channel modes: • Independent Channel Mode • Mirrored ...

...and support the right population. The BIOS enables both the memory cells and the data paths emanating from the DDR3 DIMMs. The BIOS also uses the Memory BIST to Section 3.3.9. Intel® Server Boards S5520HC, S5500HCV, and S5520HCT TPS Functional Architecture • Bank ... are supported only if both CPU sockets are installed in slots for mirroring, the BIOS disables it automatically. 3.3.8 Memory RAS 3.3.8.1 RAS Features The Intel® Server Boards S5520HC, S5500HCV and S5520HCT support the following memory channel modes: • Independent Channel Mode • Mirrored ...

Product Specification

Page 48

...then the effective memory size is established using the Independent Channel mode by at least one-half. Functional Architecture Intel® Server Boards S5520HC, S5500HCV, and S5520HCT TPS 3.3.8.2 Independent Channel Mode In the Independent Channel mode, you can continue to operate despite the presence ...is not suitable for mirroring, it allows the best interleave mode possible and thereby increases performance and thermal characteristics. If the BIOS finds the DIMM population is a RAS feature in independent channel mode. Adjacent slots on the following factors: • Current...

...then the effective memory size is established using the Independent Channel mode by at least one-half. Functional Architecture Intel® Server Boards S5520HC, S5500HCV, and S5520HCT TPS 3.3.8.2 Independent Channel Mode In the Independent Channel mode, you can continue to operate despite the presence ...is not suitable for mirroring, it allows the best interleave mode possible and thereby increases performance and thermal characteristics. If the BIOS finds the DIMM population is a RAS feature in independent channel mode. Adjacent slots on the following factors: • Current...

Product Specification

Page 49

..., the system operates in slot A1. 7. When only CPU1 socket is populated, Mirrored Channel mode is (essentially) disabled by the BIOS. 8. For example, while CPU1 memory channels A, B, and C have a different match of the parameters, channel RAS still functions....populated to conform to maximize memory bandwidth In the Independent Channel mode, all the DDR3 channels operate independently. Intel® Server Boards S5520HC, S5500HCV, and S5520HCT TPS Functional Architecture • Optimization techniques used by default. In this mode becomes the default mode of timing...

..., the system operates in slot A1. 7. When only CPU1 socket is populated, Mirrored Channel mode is (essentially) disabled by the BIOS. 8. For example, while CPU1 memory channels A, B, and C have a different match of the parameters, channel RAS still functions....populated to conform to maximize memory bandwidth In the Independent Channel mode, all the DDR3 channels operate independently. Intel® Server Boards S5520HC, S5500HCV, and S5520HCT TPS Functional Architecture • Optimization techniques used by default. In this mode becomes the default mode of timing...

Product Specification

Page 50

...; Supported - The DIMMs on different CPU sockets need not be identical and can provide customers with information on the Intel® Server Boards S5520HC, S5500HCV and S5520HCT. 3.3.10.1.1 Levels of operation. Indicates the DIMM is not empty, the BIOS disables the Mirrored Channel Mode. 17. It is a description of possible configuration combinations. Functional Architecture...

...; Supported - The DIMMs on different CPU sockets need not be identical and can provide customers with information on the Intel® Server Boards S5520HC, S5500HCV and S5520HCT. 3.3.10.1.1 Levels of operation. Indicates the DIMM is not empty, the BIOS disables the Mirrored Channel Mode. 17. It is a description of possible configuration combinations. Functional Architecture...

Product Specification

Page 52

Functional Architecture Intel® Server Boards S5520HC, S5500HCV, and S5520HCT TPS 3.3.11 Memory Error Handling The BIOS classifies memory errors into the following categories: ƒ Correctable ECC errors: This correction could be the result of an ECC correction, a successfully retried memory cycle, ... Parity Error is logged as such in the SEL, but in all other ways, is treated the same as an Uncorrectable ECC Error. 38 Revision 1.8 Intel order number E39529-013

Functional Architecture Intel® Server Boards S5520HC, S5500HCV, and S5520HCT TPS 3.3.11 Memory Error Handling The BIOS classifies memory errors into the following categories: ƒ Correctable ECC errors: This correction could be the result of an ECC correction, a successfully retried memory cycle, ... Parity Error is logged as such in the SEL, but in all other ways, is treated the same as an Uncorrectable ECC Error. 38 Revision 1.8 Intel order number E39529-013

Product Specification

Page 53

... host interface with independent DMA operation on up to 3.0 Gb/s. Intel® Server Boards S5520HC, S5500HCV, and S5520HCT TPS Functional Architecture 3.4 ICH10R The ICH10R provides extensive I /O Controller Hub • Software RAID option is selected on the BIOS menu for the SATA controller Revision 1.8 39 Intel order number E39529-013 six UHCI host controllers; Functions and...

... host interface with independent DMA operation on up to 3.0 Gb/s. Intel® Server Boards S5520HC, S5500HCV, and S5520HCT TPS Functional Architecture 3.4 ICH10R The ICH10R provides extensive I /O Controller Hub • Software RAID option is selected on the BIOS menu for the SATA controller Revision 1.8 39 Intel order number E39529-013 six UHCI host controllers; Functions and...

Product Specification

Page 54

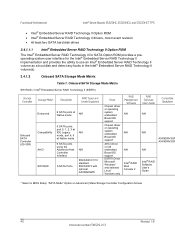

...Intel® Server Boards S5520HC, S5500HCV, and S5520HCT TPS • Intel® Embedded Server RAID Technology II Option ROM • Intel® Embedded Server RAID Technology II drivers, most recent revision • At least two SATA hard disk drives 3.4.1.1.1 Intel® Embedded Server RAID Technology II Option ROM The Intel... disk and detect any faults in BIOS Setup: "SATA Mode" Option on Advanced | Mass Storage Controller Configuration Screen 40 Revision 1.8 Intel order number E39529-013 Onboard SATA Storage Mode Matrix SW RAID = Intel® Embedded Server RAID Technology II...

...Intel® Server Boards S5520HC, S5500HCV, and S5520HCT TPS • Intel® Embedded Server RAID Technology II Option ROM • Intel® Embedded Server RAID Technology II drivers, most recent revision • At least two SATA hard disk drives 3.4.1.1.1 Intel® Embedded Server RAID Technology II Option ROM The Intel... disk and detect any faults in BIOS Setup: "SATA Mode" Option on Advanced | Mass Storage Controller Configuration Screen 40 Revision 1.8 Intel order number E39529-013 Onboard SATA Storage Mode Matrix SW RAID = Intel® Embedded Server RAID Technology II...